Mikrocontroller(639)

- 8-bit-8051-MCUs(88)

- 8bit KM101 MCUs(27)

-

Arm Cortex-M0-MCUs(293)

-

M029G/M030G/M031G Series(9)

-

M031-Serie(21)

-

M031BT Series(2)

-

M032-Serie(16)

-

M032BT Series(2)

-

M071 Series(4)

-

M091 Series(4)

-

M0A21 Series(4)

-

M0A23 Series(4)

- NUC029-Serie(12)

- Nano103-Base-Serie(3)

- Nano100/102-Base-Serie(19)

- Nano110/112-LCD-Serie(19)

- Nano120-USB-Serie(10)

- Nano130-Advanced-Serie(8)

- NUC100/200-Advanced-Serie(15)

-

NUC120/122/123/220-USB-Serie(38)

- NUC120LC1DN

- NUC120LD2DN

- NUC120LE3DN

- NUC120RD2DN

- NUC120RC1DN

- NUC120RE3DN

- NUC120VE3DN

- NUC122LC1AN

- NUC122LC1DN

- NUC122LD2AN

- NUC122LD2DN

- NUC122SC1AN

- NUC122SC1DN

- NUC122SD2AN

- NUC122SD2DN

- NUC122ZC1AN

- NUC122ZC1DN

- NUC122ZD2AN

- NUC122ZD2DN

- NUC123LC2AE1

- NUC123LD4AE0

- NUC123LD4AN0

- NUC123SC2AE1

- NUC123LC2AN1

- NUC123SC2AN1

- NUC123SD4AE0

- NUC123SD4AN0

- NUC123ZC2AE1

- NUC123ZC2AN1

- NUC123ZD4AN0

- NUC123ZD4AE0

- NUC220LC2AN

- NUC220LD2AN

- NUC220LE3AN

- NUC220SC2AN

- NUC220SD2AN

- NUC220SE3AN

- NUC220VE3AN

- NUC121/125-Serie(6)

- NUC126-USB-Serie(6)

- NUC130/230-CAN-Serie(14)

- NUC140/240-Konnektivität-Serie(14)

- M051-Base-Serie(21)

- Mini51-Base-Serie(21)

- M0518-Serie(4)

- NUC131-NUC1311-CAN-Serie(7)

- M0519-Serie(5)

- M0564-Serie(5)

-

M029G/M030G/M031G Series(9)

- Arm Cortex-M23 Mikrocontroller(77)

-

Arm Cortex-M4-MCUs(145)

-

M433 CAN/USB FS OTG Series(2)

- KM1M4BF Series(1)

-

M463 CAN FD/USB HS Series(7)

-

M467 Ethernet/Crypto Series(8)

-

M471 Series(6)

- M487-Ethernet-Serie(4)

- M485-Crypto-Serie(5)

- M484-USB-HS-OTG-Serie(5)

- M483-CAN-Serie(8)

- M482-USB-FS-OTG-Serie(14)

- M481-Base-Serie(11)

- M4TK-Touch-Key-Serie(6)

- M451-Base-Serie(10)

- M4521 USB Serie(2)

- NUC442/472-Serie(16)

- M452-USB-Serie(9)

- M453-CAN-Serie(10)

- NUC505-Serie(7)

- M451M-Serie(6)

-

M433 CAN/USB FS OTG Series(2)

- Arm Cortex-M7 MCUs(3)

- 32bit KM103 MCUs(6)

MOSFET(73)

-

Low On Resistance MOSFET for Li-ion Battery Protection(47)

-

12V-30V Nch Dual MOSFET(47)

- KFCAB21B10L

- KFCAB21C00L

- KFCAB21860L

- KFCAB21520L

- KFCAB21B50L

- KFCAB21890L

- KFCAB21770L

- KFCAB21260L

- KFCAB21B30L

- KFCAB21740L

- KFCAB21490L

- KFCAB21A50L

- KFCAB21350L

- KFCAB21830L

- KFCAB12004NL

- KFC6B21150L

- KFC6B21B70L

- FC6B21100L

- KFC4B21A30L

- KFC4B21210L

- KFC4B21280L

- KFC4B21220L

- KFC4B21080L

- KFC4B21320L

- KFC4A21300L

- KFC4B21300L

- KFC4B21330L

- KFCAB22370L

- KFC6B22160L

- KFCAB22510L

- KFC6B22500L

- KFC4B22180L

- KFC4B22270L

- KFC4B22690L

- KFC4B22670L

- KFC4B22830L

- KFCAB22014NL

- KFCAB22020NL

- KFCAB22630L

- KFCAB22620L

- KFCAB22680L

- KFCAB22900L

- KFC6B22100L

- KFC6B22220L

- KFC4B22070L

- KFC7P23440L

- KFCAB30029NL

-

12V-30V Nch Dual MOSFET(47)

- Low On Resistance MOSFET for Li-ion Battery Charging Control(5)

- Small Size MOSFET for Automotive Switching(11)

- Small Size MOSFET for General Switching(10)

Audio(325)

- Audio SoCs(20)

- ISD-ChipCorder-Familie(28)

- Audiowandler(37)

- Audioverstärker(20)

- Audioverstärkung(3)

-

ISD-Sprache-ICs(217)

- NuVoice-Serie(4)

-

PowerSpeech-Serie(128)

- N584L020

- N584L030

- N584L031

- N584L040

- N584L041

- N584L061

- N584L080

- N584L081

- N584L120

- N584L121

- N588H061

- N588H061

- N588H120

- N588H170

- N588H250

- N588H340

- N588HP340(OTP)

- W584A011

- W584A016

- W584A017

- W584A021

- W584A022

- W584A025

- W584A031

- W584A032

- W584A035

- W584A041

- W584A042

- W584A045

- W584A051

- W584A052

- W584A061

- W584A062

- W584A065

- W584A071

- W584A075

- W584A081

- W584A085

- W584A100

- W584A120

- W584A151

- W584A171

- W584A191

- W584A300

- W584A340

- W584AP017(OTP)

- W584AP065(OTP)

- W584B010

- W584B015

- W584B016

- W584B020

- W584B021

- W584B030

- W584B031

- W584B040

- W584B041

- W584B052

- W584B062

- W584B070

- W584B080

- W584B100

- W584B120

- W584B150

- W584B170

- W584B190

- W588C003

- W588C006

- W588C009

- W588C012

- W588C015

- W588C020

- W588C025

- W588C030

- W588C036

- W588C041

- W588C046

- W588C051

- W588C056

- W588C061

- W588C071

- W588C081

- W588C101

- W588C121

- W588C150

- W588C170

- W588C210

- W588C260

- W588C300

- W588C350

- W588C400

- W588D003

- W588D006

- W588D009

- W588D012

- W588D015

- W588D020

- W588D025

- W588D030

- W588D035

- W588D040

- W588D045

- W588D050

- W588D055

- W588D060

- W588D070

- W588D080

- W588D100

- W588D120

- W588D150

- W588D170

- W588D210

- W588D260

- W588D300

- W588D350

- W588D400

- W588DF060(MTP)

- W588L020

- W588L030

- W588L035

- W588L040

- W588L050

- W588L060

- W588L070

- W588L080

- W588L100

- W588L121

- W588L150

- W588L170

-

BandDirector-Serie(48)

- N567G030

- N567G041

- N567G080

- N567G120

- N567G160

- N567G200

- N567G240

- N567G280

- N567G330

- N567H030

- N567H041

- N567H080

- N567H120

- N567H160

- N567H200

- N567H240

- N567H280

- N567H330

- N567HP330(OTP)

- N567K030

- N567K041

- N567K080

- N567K120

- N567K160

- N567K200

- N567K240

- N567K280

- N567K330

- N567L120

- N567L160

- N567L200

- W567C070

- W567C080

- W567C100

- W567C120

- W567C126

- W567C151

- W567C171

- W567C210

- W567C260

- W567C266

- W567C300

- W567C306

- W567C340

- W567C346

- W567C380

- W567C386

- W567CP260(OTP)

- ViewTalk-Serie(20)

- Peripherie-Serie(17)

- NuSpeech-Serie

- NSPxx Series

IoT-Lösung(20)

-

IoT-Plattform(18)

- NuMaker-IoT-MA35D0-A1

-

NuMaker-IoT-MA35D1-A1

- NuMaker-IoT-M2354

- NuMaker-RTU-NUC980(Chili)

- NuMaker-Server-NUC980

- NuMaker-IIoT-NUC980

- NuMaker-IIoT-NUC980G2

-

NuMaker-IIoT-NUC980G2D

- NuMaker-Tomato

- NuMaker-IoT-M487

- NuMaker-PFM-M487

- NuMaker-PFM-M453

- NuMaker-PFM-NUC472

- NuMaker-PFM-M2351

- NuMaker-IoT-M263A

- NuMaker-PFM-NANO130

- NuMaker-Brick

- NuMaker-Uni

- Alexa Connect Kit Platform

- IoT-Engine-Plattform(1)

- Arduino-kompatible Entwicklerboard(1)

- LoRa Platform

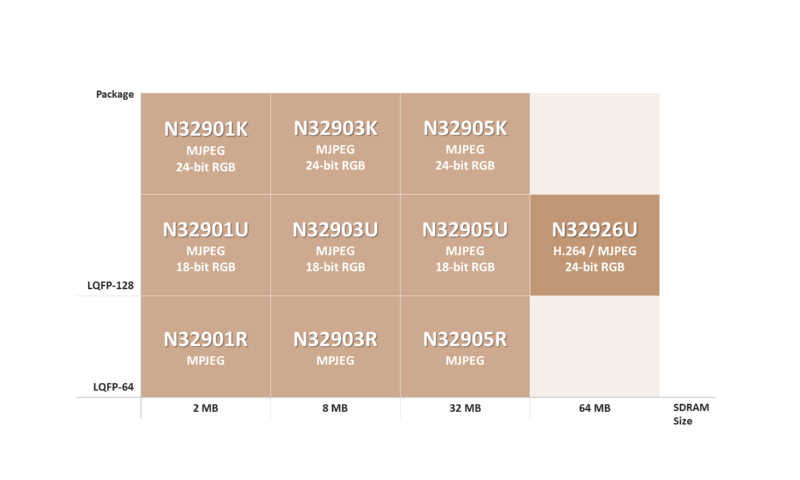

N3290-MJPEG-Serie

Nuvoton’s N329 Series is an ARM926EJ-S running up to 200MHz/240MHz and hardware JPEG/H.264 codec based product line targeting for low-cost ELA (Educational Learning Aid) , Video Baby Monitor, WiFi Camera and HMI (Human Machine Interface) applications. The N329 series is 64-pin and 128-pin LQFP package stacked with 2 MB, 8 MB, 32 MB or 64 MB DRAM. It can also be used as a general purpose MCU.

| • | Stack SDRAM @LQFP package | |

| - | Up to 64MB DDR Memory | |

| - | LQFP64/LQFP128 | |

| • | TFT-LCD controller | |

| - | Up to 24-bit RGB | |

| - | Up to 1024x768 | |

| - | 2D graphic engine | |

| • | Hardware video codec | |

| - | H.264 720P @25fps | |

| - | MJPEG | |

| • | Peripheral | |

| - | USB2.0 HS Host/Device | |

| - | Up to 3 sets SD Card/SDIO | |

| - | 10/100 Ethernet MAC | |

| - | Up to 2 sets Camera Sensor Interface | |

| • | Operating system | |

| - | Embedded Linux | |

| - | FreeRTOS | |

| - | Non-OS | |