# **Industrial Application Battery Monitoring IC**

# KA49517A Product Brief

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation Japan and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing document only for reference purposes of KA49517A Battery Monitoring IC based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

#### **Characteristics**

- Maximum support 17 battery cells in series

- 10mV measurement accuracy with 14 bits voltage ADC for cell voltage, and 5 channels analog input measurement for Thermistor

- Built-in 16 bits Low speed Current measurement ADC (Coulomb Counter) and 15 bits High speed Current measurement ADC

- Low-side Sense resistor Current measurement and monitoring

- Operation mode Active, Standby/Low power; Sleep and Shutdown

- SPI serial communication interface up to 1MHz clock with CRC code correction and watchdog timer

- Built-in ALARM pins for overvoltage, undervoltage, overcurrent and short circuit detection and protection feature

- Built-in cell balancing MOSFET, support external cell balance MOSFET operation as well

- 3 channels General GPIO and 2 channels high voltage output GPOH

- Interrupt signal provision for MCU to notify state of operation as well as measurement cycle indication at the available GPIO pins

- High-side N-MOSFET driver: Charge (CHG) & Discharge (DIS) with built-in charge pump and FETOFF control pin

- Built in controllable fuse driver for cell OV and overcurrent monitoring algorithm to serve as secondary protection system

- Regulator (REG\_EXT) for external circuit power provision with selectable output setting 5V/3.3V/2.5V, and 50mA drive ability

- Safety Diagnostic function for measurement related check and FET driver check to enhance the total diagnostic coverage of the chip

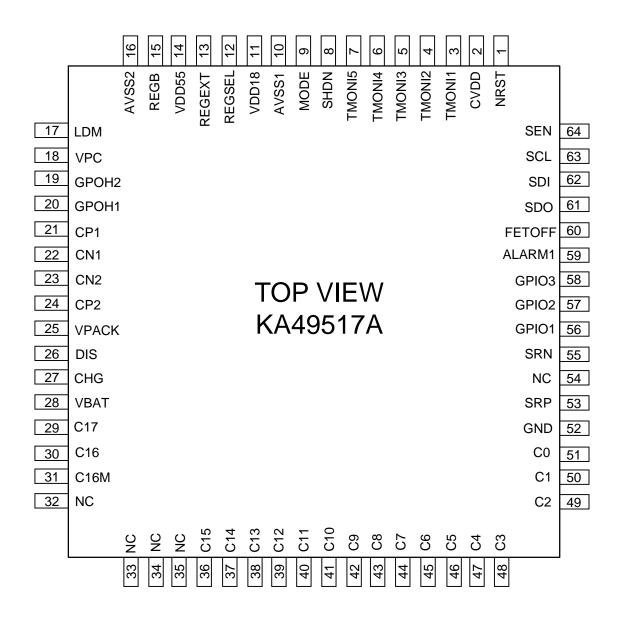

- Package: TQFP 64L (10x10x1mm³, Lead Pitch 0.5mm)

#### Overview

KA49517A is a battery monitoring IC with protection function. With high resolution ADC built-in, KA49517A is capable to measure battery cell voltage and current level accurately. Through SPI serial interface, microcontroller unit (MCU) is able to read the status and measured result by KA49517A. The ALARM pins alert the MCU with the abnormal condition such as over voltage (OV), under voltage (UV), over current (OC) and short circuit (SC).

KA49517A can support an application with up to 17 batteries cells in series or a maximum voltage of 85V, it is suitable for application with high input voltage such as E-bike, UPS etc.

### Applications

Pedelec, e-Bike, UPS, Server Backup System, Power Tool, Energy Storage Systems etc

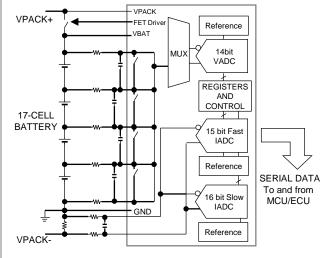

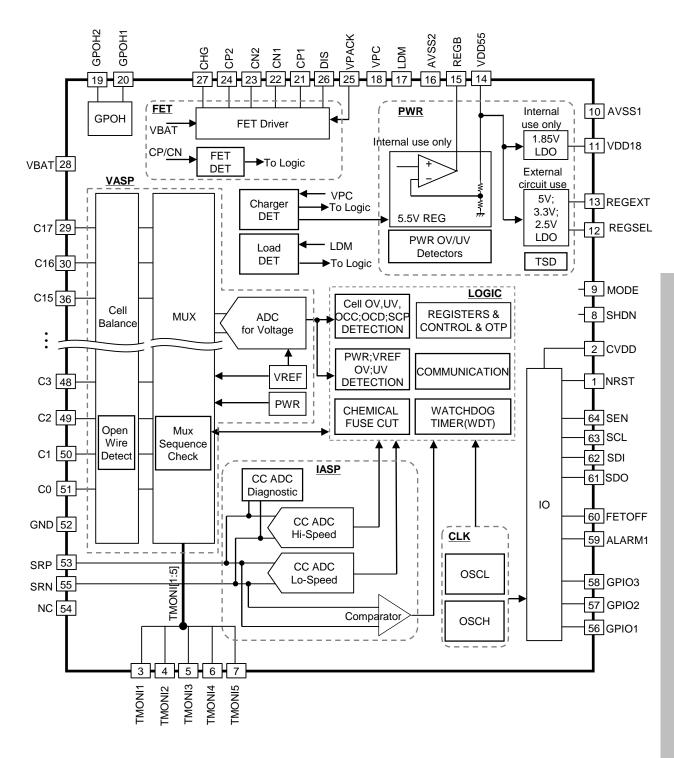

# System Block Diagram

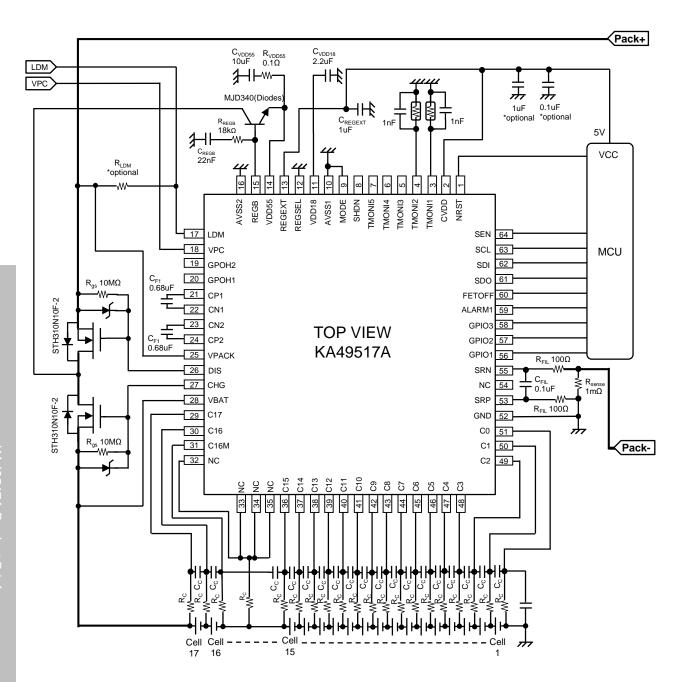

Notes: This is just an example of a circuit set: it is not guaranteed to function identically to the final production version.

When designing a set for production, make sure to carefully evaluate and verify the circuitry.

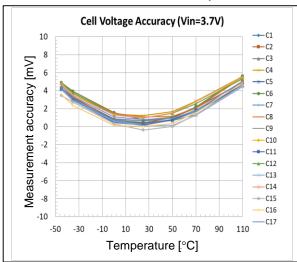

# **Representation Characteristics**

Measurement accuracy

Application circuit example (17cells connection), VBAT=62.9V , cell voltage  $\Delta$ Cn ( $C_n$ - $C_{n-1}$ ) = 3.7V

# **Table of Contents**

| Characteristics                            | 2    |

|--------------------------------------------|------|

| Overview                                   |      |

| ■ Applications                             |      |

| System Block Diagram                       |      |

| Representative Characteristic              | 2    |

| Absolute Maximum Ratings                   | 4    |

| Power Dissipation Ratings                  | 5    |

| Recommended Operating Conditions           | 5    |

| ■ Electrical Characteristics               | 6    |

| ■ Pin Assignment                           | 17   |

| ■ Pin Description                          | 18   |

| ■ Block Diagram                            | 21   |

| Application Circuit Example                | 22   |

| Recommended Constant of External Component | 23   |

| ■ Description of Functions                 | 24   |

| 1. Battery Connection                      | 24   |

| ■ Dimensions                               | . 25 |

| ■ IMPORTANT NOTICE                         | . 26 |

# **Absolute Maximum Ratings**

| Parameter                      | Symbol *1                               | Rating                          | Unit | Notes |

|--------------------------------|-----------------------------------------|---------------------------------|------|-------|

|                                | V <sub>VBAT</sub> to GND                | -0.3 to 130                     | V    | *5    |

|                                | V <sub>CVDD</sub> to GND                | -0.3 to 6.4                     | V    | *2    |

| Supply voltage                 | V <sub>VDD55</sub> to GND               | -0.3 to 6.4                     | V    | *2    |

|                                | V <sub>VDD18</sub> to GND               | -0.3 to 2.3                     | V    | *2    |

|                                | V <sub>REGEXT</sub> to GND              | -0.3 to 6.4                     | V    | *2    |

|                                | Cn (n=10 ~17)                           | -0.3 to $V_{VBAT}$              | V    |       |

|                                | Cn (n=1∼9)                              | -0.3 to 38 + 11*(N-1)           | V    |       |

|                                | C0                                      | -0.3 to 38                      | V    |       |

|                                | SEN, SCL, SDI, FETOFF,<br>GPIOn (n=1∼3) | -0.3 to $V_{\text{CVDD}}$ +0.3  | V    | *3    |

| Input Voltage Range            | TMONIn (n=1~5),<br>REGSEL               | -0.3 to V <sub>VDD55</sub> +0.3 | V    | *3    |

|                                | SRP.SRN                                 | -0.5 to 2.0                     | V    |       |

|                                | VPC                                     | -0.3 to 130                     | V    |       |

|                                | LDM                                     | -0.3 to 130                     | V    |       |

|                                | SHDN                                    | -0.3 to 6.4                     | V    |       |

|                                | ALARM1,SDO,NRST                         | -0.3 to V <sub>CVDD</sub> +0.3  | V    |       |

| Output Voltage Range           | GPOHn (n=1~2)                           | -0.3 to 130                     | V    |       |

|                                | REGB                                    | -0.3 to 14                      | V    |       |

|                                | ALARM1,SDO,NRST                         | -6.0 to +6.0                    | mA   |       |

|                                | GPIOn (n=1~3)                           | (-12.0 to +12.0)                | IIIA | *4    |

| Output Current Range           | REGB                                    | -3.5 to 3.5                     | mA   |       |

|                                | REGEXT                                  | -50.0 to 0                      | mA   | *6    |

| Allowable Voltage Between Pins | $C_n - C_{n-1} (n=1 \sim 17)$           | -0.3 to 11                      | V    |       |

| Operating junction temperature | T <sub>i</sub>                          | -40 to 125                      | °C   | *2    |

| Storage temperature            | T <sub>stg</sub>                        | -55 to 125                      | °C   | *2    |

Notes: Stresses that exceed the absolute maximum ratings may cause fatal damage to the product.

This specifies the maximum rating for stress.

It is NOT a guaranteed operating region because it exceeds the recommended operating conditions.

The reliability of the IC may be affected if it is kept under absolute maximum rating conditions for long periods.

Applied external current and voltage to pins should also not exceed the absolute maximum ratings listed here.

- \*2: The maximum ratings are allowable unless the power consumption exceeds the power dissipation ratings.

- \*3:  $V_{CVDD}$  is the voltage of CVDD.  $V_{VDD55}$  is the voltage of VDD55. It should not exceed the rated 6.4 V.

- \*4: + Polarity is the direction in which current flows into the IC pins.

- Polarity is the direction in which current flows out from the IC pins.

- \*5: V<sub>VBAT</sub> is the voltage of VBAT. It should not exceed the rated 130V.

- \*6: The output circuit consists of both external components and internal circuitry. Refer to the application circuit diagram.

<sup>\*1:</sup> GND is the voltage of pins GND1, GND2, and GND3 which are connected inside the device. Connect these pins on the board and apply the same voltage.

# **Power Dissipation Ratings**

| Package                                    | θј-а      | θј-с     | P <sub>D</sub> (Ta = 25°C) | P <sub>D</sub> (Ta=105°C) | Note |

|--------------------------------------------|-----------|----------|----------------------------|---------------------------|------|

| TQFP 64L (10x10x1mm³,<br>Lead Pitch 0.5mm) | 37.7 °C/W | 2.7 °C/W | 2.65 W                     | 0.53 W                    | *1   |

Notes: These characteristics are the reference values for design.

Refer to the PD-Ta characteristics diagram in the package specifications. Thermal design with a sufficient margin is recommended based on the conditions of supply voltage, load, and ambient temperature.

\*1: Mounting board: Glass epoxy 4-layer board without soldered heat spreader measuring 50 mm x 50 mm x 0.8 mm Wiring layer thickness: all layers 0.035 mm, proportion of copper foil: 57% / 100% / 100% / 57%

#### CAUTION

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

# **Recommended Operating Conditions**

Below items must be within the range of Recommended Operating Conditions.

| Parameter                        | Symbol *1                                  | Min.  | Тур. | Max.        | Unit | Note |

|----------------------------------|--------------------------------------------|-------|------|-------------|------|------|

| Cupply voltage range             | $V_{VBAT}$                                 | 12.5  | 62.9 | 85          | V    | *2   |

| Supply voltage range             | V <sub>CVDD</sub>                          | 3.0   | 5.0  | 5.5         | V    |      |

|                                  | C <sub>n</sub> - C <sub>n-1</sub> (n=1~17) | 1.0   | _    | 4.8         | V    | *3   |

|                                  | SEN, SCL, SDI                              | 0     | _    | $V_{CVDD}$  | V    |      |

|                                  | TMONIn (n=1∼5)                             | 0     |      | $V_{VDD55}$ | V    |      |

|                                  | GPIOn (n=1∼3)                              | 0     |      | $V_{CVDD}$  | ٧    |      |

| Input Voltage Range              | REGSEL                                     | 0     | _    | $V_{VDD55}$ | V    |      |

|                                  | SRP,SRN                                    | -0.18 | _    | 0.18        | ٧    |      |

|                                  | VPC                                        | 0     | _    | 85          | V    |      |

|                                  | LDM                                        | 0     | _    | 85          | V    |      |

|                                  | SHDN                                       | 0     | _    | $V_{VDD55}$ | V    |      |

| Operating Ambient<br>Temperature | Ta <sub>opr</sub>                          | -40   | 25   | 105         | °C   |      |

<sup>\*1:</sup> GND is the voltage of pins GND1, GND2, and GND3, which are connected inside the device. Connect these pins on the board and apply the same voltage.

<sup>\*2 :</sup> The recommended operating supply range varies due to the characteristics of the external Nch BJT connected to VDD55. Use the parts described in the recommended circuit.

<sup>\*3:</sup> The  $C_n$  -  $C_{n-1}$  voltage measurement accuracy is not guaranteed if input is less than 2.0 V or more than 4.3 V. Moreover, the measurement accuracy is not guaranteed unless the following conditions are fulfilled. C2 > 2.0 V, C17 > 12 V, VBAT - C17 > -2 V, VBAT - C16 > 1 V

<sup>\*</sup> Cn (n = 1 to 17) and VBAT voltage in this conditions are in reference to GND.

<sup>\*</sup> Similarly for the monitoring system, replace the above condition Cn (n = 1 to 17) with CBn (n = 1 to 17).

Unless otherwise noted, the characteristics are specified under the recommended operating condition:  $VBAT = 62.9 \text{ V. CVDD} = 5.0 \text{V. ambient temperature. T.} = 25^{\circ}\text{C} + 2^{\circ}\text{C}$  and test circuit reference.

| Parameter              | Symbol               | Condition                                                                                                    |      | Limits |      | Unit  | Not |

|------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|------|--------|------|-------|-----|

| raiailletei            | Symbol               | Condition                                                                                                    | Min  | Тур    | Max  | Offic | INO |

| UPPLY CURRENT*1        |                      |                                                                                                              |      |        |      |       |     |

| VBAT Active Mode       | I <sub>BAT1</sub>    |                                                                                                              | _    | 3.6    | 4.5  | mA    |     |

| VBAT Low Power Mode    | I <sub>BAT2</sub>    | INTMSEL=10<br>20ms intermittent mode                                                                         | _    | 1.35   | 1.75 | mA    | **  |

| VBAT Standby Mode      | I <sub>BAT3</sub>    | VDD55=Low Power, REGEXT=Low Power Coulomb Counter=off FDRV=power reduction mode INTMSEL=00 Communication=off | _    | 0.22   | 0.30 | mA    |     |

| VBAT Sleep Mode        | I <sub>BAT4</sub>    | VDD55=Low Power,<br>REG18=Low Power,<br>REGEXT=off,<br>Communication=off                                     | _    | 80     | 130  | μА    |     |

| VBAT Shutdown Mode     | I <sub>BAT5</sub>    |                                                                                                              | _    | 0      | 1    | μА    |     |

| DD55                   |                      |                                                                                                              |      |        |      |       |     |

| VDD55 Output Voltage   | $V_{VDD55}$          |                                                                                                              | 5.3  | 5.5    | 5.8  | V     |     |

| VDD55 Base Current1    | IB <sub>VDD551</sub> | High Power mode;<br>Temp=25°C; VBAT=62.9V                                                                    | 0.75 | 1.025  | 1.30 | mA    |     |

| VDD55 Base Current2    | IB <sub>VDD552</sub> | Low Power mode;<br>Temp=25°C; VBAT=62.9V                                                                     | 0.4  | 0.65   | 0.9  | mA    |     |

| EGEXT                  |                      |                                                                                                              |      |        |      |       |     |

| REGEXT Output Voltage1 | V <sub>EXT1</sub>    | REGSEL pin=L                                                                                                 | 4.75 | 5      | 5.25 | ٧     |     |

| REGEXT Output Voltage2 | $V_{EXT2}$           | REGSEL pin=H                                                                                                 | 3.05 | 3.3    | 3.55 | V     |     |

| REGEXT Output Voltage3 | V <sub>EXT3</sub>    | REGSEL pin=Float                                                                                             | 2.3  | 2.5    | 2.7  | V     |     |

| REGEXT Output Current1 | I <sub>EXT1</sub>    | Normal mode                                                                                                  | 0    | _      | 50   | mA    |     |

| REGEXT Output Current2 | I <sub>EXT2</sub>    | Low Power mode                                                                                               | 0    | _      | 10   | mA    |     |

| EG18                   |                      |                                                                                                              |      |        |      |       |     |

|                        | $V_{REG18}$          | No load condition                                                                                            | 1.78 | 1.85   | 1.92 | V     |     |

<sup>\*1 :</sup> Current consumption is based on the following settings.

- Consumption current is measured based total current from VBAT pin (pin 14) and VDD55 pin (pin 28).

- LDM pin is HIZ condition unless specified ;All pins no load ;SEN, SCL, and SDI = Low

- Unless otherwise specified, all registers are in the default setting.

If VDD55 and CVDD are supplying an external load, this extra current should be included additionally .

<sup>\*2 :</sup> Design reference value not tested during final production inspection.

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a = 25^{\circ}\text{C} \pm 2^{\circ}\text{C}$  and test circuit reference.

| Parameter                         | Symbol                       | Condition                                                               |            | Limits |     | Unit  | NIO            |

|-----------------------------------|------------------------------|-------------------------------------------------------------------------|------------|--------|-----|-------|----------------|

| Parameter                         | Symbol                       | Condition                                                               | Min        | Тур    | Max | Offic | INOI           |

| ELL VOLTAGE MONITOR               |                              |                                                                         |            |        |     |       |                |

| Input Voltage Range               | V <sub>IN1</sub>             | $C_n - C_{n-1} (n=1 \sim 17)$                                           | 0          | _      | 5   | V     | *4             |

| Voltage Resolution                | V <sub>RES1</sub>            | 14bits<br>V <sub>RES1</sub> = 5 / 2 <sup>14</sup>                       |            | 0.3    | _   | mV    | *4             |

| Voltage Accuracy1                 | V <sub>ACC_VC1</sub>         | $\Delta$ Cn = 2.0V $\sim$ 4.3 V                                         | <b>–</b> 5 | _      | 5   | mV    | *1<br>tc<br>*3 |

| Voltage Accuracy2                 | V <sub>ACC_VC2</sub>         | $\Delta$ Cn = 2.0V ~ 4.3 V<br>Ta = -30°C ~ 75°C                         | -10        | _      | 10  | mV    | *4             |

| Voltage Accuracy3                 | V <sub>ACC_VC3</sub>         | $\Delta$ Cn = 2.0V ~ 4.3 V<br>Ta = -40°C ~ 85°C                         | -15        |        | 15  | mV    | *4             |

| Conversion Time                   | t <sub>conv</sub>            | time/cell                                                               | _          | 50     | _   | μS    | *4             |

| Cell Measurement Input<br>Current | I <sub>IN</sub>              | Active mode                                                             | <b>–</b> 5 | _      | 5   | μΑ    |                |

| Input Leakage Current             | I <sub>LK</sub>              | Shutdown mode                                                           | -1         | _      | 1   | μΑ    |                |

| VER / UNDER VOLTAGE DE            | TECTOR (C                    | OV / UV)                                                                |            |        |     |       |                |

| OV detection threshold step       | V <sub>ACC_OV</sub>          | 2.0~4.5V@6bit                                                           | _          | 50     | _   | mV    | *              |

| UV detection threshold step       | V <sub>ACC_UV</sub>          | 0.5~3.0V@6bit                                                           | _          | 50     | _   | mV    | *,             |

| PACK CELL VOLTAGE MON             | •                            |                                                                         |            | •      | •   |       |                |

| Input Voltage Range               | V <sub>IN2</sub>             |                                                                         | 0          | _      | 110 | V     | *,             |

| Voltage Resolution                | V <sub>RES2</sub>            | 14bits                                                                  | _          | 6.7    | _   | mV    | *,             |

| Voltage Accuracy1                 | V <sub>ACC</sub> _           | V <sub>VPACK</sub> = 12.5V ~ 76.5V                                      | -1         | _      | 1   | V     | *<br>te        |

| Voltage Accuracy2                 | V <sub>ACC</sub> _<br>VPACK2 | $V_{VPACK} = 12.5V \sim 76.5V$<br>$T_a = -30^{\circ}C \sim 75^{\circ}C$ | -1         | _      | 1   | V     | *              |

<sup>\*1 :</sup> The  $C_n$  -  $C_{n-1}$  voltage measurement accuracy is not guaranteed if input is less than 2.0 V or more than 4.3 V. Moreover, the measurement accuracy is not guaranteed unless the following conditions are fulfilled. C2 > 2.0 V, C17 > 12 V, VBAT - C17 > -2 V, VBAT - C16 > 1 V

- \*3: Measurement accuracy value including consideration of input average current and input leakage current.

- \*4 : Design reference value not tested during final production inspection.

- \*5 : Voltage resolution Typ. value is an approximate value derived from the Input voltage range Max. value and the number of bits.

Cell (Monitoring) voltage resolution,  $V_{RES1} = V_{IN1} / 2^{14} = 5 / 2^{14} = 0.3 \text{mV}$  approx. Vpack voltage resolution,  $V_{RES2} = V_{IN2} / 2^{14} = 110 / 2^{14} = 6.7 \text{mV}$  approx

<sup>\*</sup> Cn (n = 1 to 17) and VBAT voltage in this conditions are in reference to GND.

<sup>\*2 :</sup> This is the final inspection value before shipping out. The value does not include variations caused by stress applied during board mounting or after board mounting. The value in the parenthesis is the accuracy after soldering and aging.

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0 V, ambient temperature.  $T_0 = 25^{\circ}\text{C} \pm 2^{\circ}\text{C}$  and test circuit reference.

| Parameter                                        | Symbol             | Condition                                                                                     |      | Limits |     | Unit | Note           |

|--------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|------|--------|-----|------|----------------|

| Parameter                                        | Symbol             | Condition                                                                                     | Min  | Тур    | Max | Unit | INOLE          |

| MONI1-5 VOLTAGE MONI                             | TOR                |                                                                                               |      |        |     |      |                |

| Input Voltage Range                              | V <sub>IN3</sub>   |                                                                                               | 0    | _      | 5   | V    | *1             |

| Voltage Resolution                               | $V_{RES3}$         | 14bits                                                                                        | _    | 0.3    | _   | mV   | *1             |

| Voltage Accuracy1                                | V <sub>ACC</sub> _ | VIN = 0.4V~4.7V<br>Not use Pull-up Resistance                                                 | -10  | _      | 10  | mV   | *2<br>to<br>*3 |

| Voltage Accuracy2                                | V <sub>ACC</sub> _ | VIN = $0.4V \sim 4.7V$<br>Not use Pull-up Resistance<br>$T_a = -30^{\circ}C \sim 75^{\circ}C$ | -10  | _      | 10  | mV   | *1             |

| Voltage Accuracy3                                | V <sub>ACC</sub> _ | VIN = $0.4V \sim 4.7V$<br>Not use Pull-up Resistance<br>$T_a = -40^{\circ}C \sim 85^{\circ}C$ | -15  |        | 15  | mV   | *1             |

| Input Pull-up Resistance                         | $R_{PU}$           |                                                                                               | 7    | 10     | 13  | kΩ   |                |

| Input Pull-up Resistance Temperature coefficient | RT <sub>PU</sub>   | $T_a = -30^{\circ}C \sim 75^{\circ}C$<br>(with reference to 25°C)                             | -1.0 | _      | 1.0 | %    | *1             |

| PIO1-2 VOLTAGE MONIT                             | OR                 |                                                                                               |      |        |     |      |                |

| Input Voltage Range                              | $V_{IN4}$          |                                                                                               | 0    | _      | 5   | V    | *1             |

| Voltage Resolution                               | $V_{RES4}$         | 14bits                                                                                        |      | 0.3    | _   | mV   | *1             |

| Voltage Accuracy1                                | V <sub>ACC</sub> _ | VIN = 0.4V~4.7V                                                                               | -10  | _      | 10  | mV   | *2<br>to<br>*3 |

| Voltage Accuracy2                                | V <sub>ACC</sub> _ | VIN = $0.4V \sim 4.7V$<br>$T_a = -30^{\circ}C \sim 75^{\circ}C$                               | -15  | _      | 15  | mV   | *1             |

| Voltage Accuracy3                                | V <sub>ACC</sub> _ | $VIN = 0.4V \sim 4.7V$<br>$T_a = -40^{\circ}C \sim 85^{\circ}C$                               | -20  | _      | 20  | mV   | *1             |

<sup>\*1 :</sup>Design reference value not tested during final production inspection.

Voltage resolution Typ. value is an approximate value derived from the Input voltage range Max. value and the number of bits.

TMONI voltage resolution,  $V_{RES3} = V_{IN3}(Max.) / 2^{14} = 5 / 2^{14} = 0.3 \text{mV}$  approx.

GPIO voltage resolution,  $V_{RES4} = V_{IN4}(Max.) / 2^{14} = 5 / 2^{14} = 0.3 \text{mV}$  approx.

<sup>\*2 :</sup>This is the final inspection value before shipping out. The value does not include variations caused by stress applied during board mounting or after board mounting.

<sup>\*3 :</sup> Measurement accuracy value including consideration of input average current and input leakage current.

Unless otherwise noted, the characteristics are specified under the recommended operating condition:

| VBAT | $\Gamma$ = 62.9 V, CVDD = 5.0V, ambient to | emperature                    | , $T_a = 25^{\circ}C \pm 2^{\circ}C$ and test circuit refe | rence. |        |     |       |                |  |

|------|--------------------------------------------|-------------------------------|------------------------------------------------------------|--------|--------|-----|-------|----------------|--|

|      | Parameter                                  | Symbol                        | Condition                                                  |        | Limits |     | Linit | Note           |  |

|      | i alametei                                 | Symbol                        | Condition                                                  | Min    | Тур    | Max | Offic | NOIC           |  |

| \    | VDD55 VOLTAGE MONITOR                      |                               |                                                            |        |        |     |       |                |  |

|      | Input Voltage Range                        | $V_{IN5}$                     |                                                            | 0      | _      | 7.5 | V     | *1             |  |

|      | Voltage Resolution                         | $V_{RES5}$                    | 14bits                                                     | _      | 0.5    | _   | mV    | *1             |  |

|      | Voltage Accuracy1                          | V <sub>ACC</sub> _            | VIN = 5.5V                                                 | -10    | _      | 10  | mV    | *2<br>to<br>*3 |  |

|      | Voltage Accuracy2                          | V <sub>ACC</sub> _<br>VDD552  | VIN = 5.5V<br>$T_a = -30^{\circ}C \sim 75^{\circ}C$        | -15    | _      | 15  | mV    | *1             |  |

|      | Voltage Accuracy3                          | V <sub>ACC</sub> _<br>VDD553  | $VIN = 5.5V$ $T_a = -40^{\circ}C \sim 85^{\circ}C$         | -20    | _      | 20  | mV    | *1             |  |

| R    | EGEXT VOLTAGE MONITO                       | R                             |                                                            |        |        |     |       |                |  |

|      | Input Voltage Range                        | $V_{IN6}$                     |                                                            | 0      |        | 7.5 | V     | *1             |  |

|      | Voltage Resolution                         | $V_{RES6}$                    | 14bits                                                     | _      | 0.5    | _   | mV    | *1             |  |

|      | Voltage Accuracy1                          | V <sub>ACC</sub> _            | VIN = 5V                                                   | -10    |        | 10  | mV    | *2<br>to<br>*3 |  |

|      | Voltage Accuracy2                          | V <sub>ACC</sub> _<br>REGEXT2 | $VIN = 5V$ $T_a = -30^{\circ}C \sim 75^{\circ}C$           | -15    |        | 15  | mV    | *1             |  |

|      | Voltage Accuracy3                          | V <sub>ACC</sub> _            | $VIN = 5V$ $T_a = -40^{\circ}C \sim 85^{\circ}C$           | -20    | _      | 20  | mV    | *1             |  |

<sup>\*1 :</sup>Design reference value not tested during final production inspection.

Voltage resolution Typ. value is an approximate value derived from the Input voltage range Max. value and the number of bits.

$$\begin{split} &\text{VDD55 voltage resolution, V}_{\text{RES5}} = \text{V}_{\text{IN5}}(\text{Max.}) \ / \ 2^{14} = \\ &\text{REGEXT voltage resolution, V}_{\text{RES6}} = \text{V}_{\text{IN6}}(\text{Max.}) \ / \ 2^{14} = \\ &\text{7.5} \ / \ 2^{14} = 0.5 \text{mV approx.} \end{split}$$

<sup>\*2 :</sup>This is the final inspection value before shipping out. The value does not include variations caused by stress applied during board mounting or after board mounting.

<sup>\*3 :</sup> Measurement accuracy value including consideration of input average current and input leakage current.

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a = 25^{\circ}C \pm 2^{\circ}C$  and test circuit reference.

|   | Doromotor             | Cy made al                   | Condition                                            |     | Limits |     | Linit | Niete          |  |  |  |

|---|-----------------------|------------------------------|------------------------------------------------------|-----|--------|-----|-------|----------------|--|--|--|

|   | Parameter             | Symbol                       | Condition                                            | Min | Тур    | Max | Unit  | Note           |  |  |  |

| ' | VDD18 VOLTAGE MONITOR |                              |                                                      |     |        |     |       |                |  |  |  |

|   | Input Voltage Range   | V <sub>IN7</sub>             |                                                      | 0   | _      | 5   | V     | *1             |  |  |  |

|   | Voltage Resolution    | V <sub>RES7</sub>            | 14bits                                               | _   | 0.3    | _   | mV    | *1             |  |  |  |

|   | Voltage Accuracy1     | V <sub>ACC</sub> _           | VIN = 1.85V                                          | -10 | _      | 10  | mV    | *2<br>to<br>*3 |  |  |  |

|   | Voltage Accuracy2     | V <sub>ACC</sub> _<br>VDD182 | $VIN = 1.85V$ $T_a = -30^{\circ}C \sim 75^{\circ}C$  | -15 | _      | 15  | mV    | *1             |  |  |  |

|   | Voltage Accuracy3     | V <sub>ACC</sub> _<br>VDD183 | VIN = 1.85V<br>$T_a = -40^{\circ}C \sim 85^{\circ}C$ | -20 |        | 20  | mV    | *1             |  |  |  |

| ( | CELL BALANCING CONTRO | DL OUTP                      | UT (CBn)                                             |     |        |     |       |                |  |  |  |

|   | Output Impedance      | Z <sub>CB</sub>              | △Cn = 3.0V ~ 5.0V                                    |     | 12.5   | 20  | Ω     |                |  |  |  |

|   | THERMAL SHUTDOWN      |                              |                                                      |     |        |     |       |                |  |  |  |

|   | Shutdown Threshold    | T <sub>SD2</sub>             | Тј                                                   | 150 | 175    | 200 | °C    | *1             |  |  |  |

<sup>\*1 :</sup>Design reference value not tested during final production inspection.

Voltage resolution Typ. value is an approximate value derived from the Input voltage range Max. value and the number of bits.

VDD18 voltage resolution,  $V_{RES7} = V_{IN7}(Max.) / 2^{14} = 5 / 2^{14} = 0.3 mV$  approx.

<sup>\*2 :</sup>This is the final inspection value before shipping out. The value does not include variations caused by stress applied during board mounting or after board mounting.

<sup>\*3 :</sup> Measurement accuracy value including consideration of input average current and input leakage current.

Unless otherwise noted, the characteristics are specified under the recommended operating condition:

| Parameter                                         | Symbol                    | Condition                               |       | Limits |      | Unit  | Note     |

|---------------------------------------------------|---------------------------|-----------------------------------------|-------|--------|------|-------|----------|

| Farameter                                         | Symbol                    | Condition                               | Min   | Тур    | Max  | Offic | NOLE     |

| OW SPEED CURRENT MO                               | NITOR (S                  | SRP,SRN)                                |       |        |      |       |          |

| Input Voltage Range                               | V <sub>IN8</sub>          |                                         | -180  | _      | 180  | mV    | *1       |

| Voltage Resolution                                | V <sub>RES8</sub>         | 16bits                                  | _     | 5.493  |      | μV    | '        |

| Voltage Accuracy1                                 | V <sub>ACC</sub>          | VIN = 100mV                             | -1000 | _      | 1000 | μV    | *2       |

| Voltage Accuracy2                                 | V <sub>ACC</sub><br>IMONI | VIN = 10mV                              | -150  | _      | 150  | μV    | *1       |

| Voltage Accuracy3                                 | V <sub>ACC</sub>          | VIN = 1mV                               | -25   | _      | 25   | μV    | '        |

| IGH SPEED CURRENT MC                              | NITOR (S                  | SRP,SRN)                                |       |        |      |       |          |

| Input Voltage Range                               | V <sub>IN9</sub>          |                                         | -180  | _      | 180  | mV    | *1       |

| Voltage Resolution                                | V <sub>RES9</sub>         | 15bits                                  | -     | 10.99  | _    | μV    | *3       |

| Voltage Accuracy1                                 | V <sub>ACC</sub> _        | VIN = 100mV                             | -1000 | _      | 1000 | μV    | *2<br>*3 |

| Voltage Accuracy2                                 | V <sub>ACC</sub>          | VIN = 10mV                              | -150  | _      | 150  | μV    | *1       |

| Voltage Accuracy3                                 | V <sub>ACC</sub>          | VIN = 1mV                               | -50   | _      | 50   | μV    | *3       |

| URRENT PROTECTION (S                              | RP,SRN)                   |                                         |       |        |      |       |          |

| Over Current in Charge<br>Detection Accuracy1     | V <sub>CP_OCC</sub>       | Detection Threshold<br>5mV & 10mV       | -4    |        | 4    | mV    |          |

| Over Current in Charge Detection Accuracy2        | V <sub>CP_OCC</sub>       | Detection Threshold from 15mV to 120mV  | -10   | _      | 10   | mV    |          |

| Over Current in Discharge Detection Accuracy1     | V <sub>CP_OCD</sub>       | Detection Threshold from 10mV to 100mV  | -10   | _      | 10   | mV    |          |

| Over Current in Discharge Detection Accuracy2     | V <sub>CP_OCD</sub>       | Detection Threshold from 100mV to 320mV | -10   | _      | 10   | %     | *1       |

| Short Circuit in Discharge Detection Accuracy1    | V <sub>CP_SCD</sub>       | Detection Threshold from 20mV to 100mV  | -10   | _      | 10   | mV    | -        |

| Short Circuit in Discharge<br>Detection Accuracy2 | V <sub>CP_SCD</sub>       | Detection Threshold from 100mV to 640mV | -10   | _      | 10   | %     | -        |

<sup>\*1 :</sup> Design reference value not tested during final production inspection.

Voltage resolution Typ. value is an approximate value derived from the Input voltage range Max. value and the number of bits.  $V_{RES8} = V_{IN8}(max.) / 2^{16} = 360 mV / 2^{16} = 5.493 \mu V \text{ approx.}; V_{RES9} = V_{IN9}(max.) / 2^{15} = 360 mV / 2^{15} = 10.99 \mu V \text{ approx.}$ \*2 : This is the final inspection value before shipping out. The value does not include variations caused by stress applied during

board mounting or after board mounting.

<sup>\*3:</sup> Values are for normal measurement mode only (not in V-I sync mode)

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a = 25^{\circ}C \pm 2^{\circ}C$  and test circuit reference.

| Parameter                | Symbol             | Condition                                          |                           | Limits |                           | Unit  | Not  |

|--------------------------|--------------------|----------------------------------------------------|---------------------------|--------|---------------------------|-------|------|

| raiailletei              | Symbol             | Condition                                          | Min                       | Тур    | Max                       | Offic | INOI |

| ENERAL PURPOSE INP       | UT/OUTP            | UT (GPIO)                                          |                           |        |                           |       |      |

| Input Voltage "H"        | V <sub>IH1</sub>   |                                                    | V <sub>CVDD</sub> × 0.8   | _      | V <sub>CVDD</sub>         | V     |      |

| Input Voltage "L"        | $V_{IL1}$          |                                                    | 0                         | _      | V <sub>CVDD</sub> × 0.2   | V     |      |

| Output Voltage "H"       | V <sub>OH1</sub>   | I <sub>OH</sub> = -1mA                             | V <sub>CVDD</sub><br>-0.6 | _      | V <sub>CVDD</sub><br>+0.3 | V     |      |

| Output Voltage "L"       | V <sub>OL1</sub>   | I <sub>OL</sub> = +1mA                             | -0.3                      | _      | 0.4                       | V     |      |

| ENERAL PURPOSE HV        | OUTPUT (           | (GPO)                                              |                           |        |                           |       |      |

| Output Voltage "L"       | V <sub>HVOL1</sub> | I <sub>OL</sub> = +1mA                             | -0.3                      | _      | 7.0                       | V     |      |

| IGITAL INPUT(1) VPC      |                    |                                                    |                           |        | ,                         |       |      |

| Input Voltage "H"        | V <sub>IH2</sub>   |                                                    | 4.0                       | _      | _                         | V     |      |

| Input Voltage "L"        | V <sub>IL2</sub>   |                                                    | _                         | _      | 0.3                       | V     |      |

| Pull-down resistance     | R <sub>IL2</sub>   |                                                    | 6                         | 28     | 55                        | ΜΩ    |      |

| DIGITAL INPUT(2) LDM     |                    |                                                    |                           |        |                           |       |      |

| Input Voltage "H"        | V <sub>IH3</sub>   | LDM pin voltage rising for load release detection  | _                         | 2.2    | 2.3                       | V     |      |

| Input Voltage "L"        | V <sub>IL3</sub>   | LDM pin voltage falling for load current detection | 1.9                       | 2      | _                         | V     |      |

| Pull-Up current source 1 | I <sub>IL3_1</sub> | LDM pin=2V<br>ILDM setting=50uA                    | 30                        | 50     | 70                        | μА    |      |

| Pull-Up current source 2 | I <sub>IL3_2</sub> | LDM pin=2.2V<br>ILDM setting =400uA                | 200                       | 400    | 600                       | μА    |      |

| DIGITAL INPUT(3) SHDN    |                    |                                                    |                           |        | •                         |       | •    |

| Input Voltage "H"        | $V_{IH4}$          |                                                    | 3.0                       | _      | _                         | V     |      |

| Input Voltage "L"        | $V_{IL4}$          |                                                    | _                         | _      | 0.1                       | V     |      |

| Pull-down resistance     | R <sub>IL4</sub>   |                                                    | 200                       | 820    | 1500                      | kΩ    |      |

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a = 25^{\circ}C \pm 2^{\circ}C$  and test circuit reference.

|   | Parameter                           | Symbol            | Condition                                        |                            | Limits |                           | Lloit | Note |  |  |

|---|-------------------------------------|-------------------|--------------------------------------------------|----------------------------|--------|---------------------------|-------|------|--|--|

|   | raiaiiielei                         | Symbol            | Condition                                        | Min                        | Тур    | Max                       | Offic | NOLE |  |  |

| [ | DIGITAL INPUT(4) SDI,SCL,SEN,FETOFF |                   |                                                  |                            |        |                           |       |      |  |  |

|   | Input Voltage "H"                   | V <sub>IH5</sub>  |                                                  | V <sub>CVDD</sub> × 0.8    |        | V <sub>CVDD</sub>         | V     |      |  |  |

|   | Input Voltage "L"                   | V <sub>IL5</sub>  |                                                  | 0                          |        | V <sub>CVDD</sub> × 0.2   | V     |      |  |  |

|   | Input Leakage Current               | I <sub>LK5</sub>  |                                                  | -1                         | 0      | 1                         | μΑ    |      |  |  |

|   | DIGITAL INPUT(5) REGS               | EL                |                                                  |                            |        |                           |       |      |  |  |

|   | Input Voltage "H"                   | V <sub>IH6</sub>  | REGSEL pin=H For REGEXT=3.3V output settings     | V <sub>VDD55</sub><br>-0.3 |        | _                         | V     |      |  |  |

|   | Input Voltage "L"                   | V <sub>IL6</sub>  | REGSEL pin=L For REGEXT=5V output settings       | _                          | _      | 0.3                       | V     |      |  |  |

|   | Input Voltage Float                 | V <sub>FLT6</sub> | REGSEL pin=Float For REGEXT=2.5V output settings | 2                          | 2.75   | 3.5                       | V     |      |  |  |

|   | DIGITAL OUTPUT(1) ALA               | ARM1,SDC          |                                                  |                            |        |                           |       |      |  |  |

|   | Output Voltage "H"                  | V <sub>OH7</sub>  | I <sub>OH</sub> = -1mA                           | V <sub>CVDD</sub><br>-0.6  | _      | V <sub>CVDD</sub><br>+0.3 | V     |      |  |  |

|   | Output Voltage "L"                  | V <sub>OL7</sub>  | I <sub>OL</sub> = +1mA                           | -0.3                       | _      | 0.4                       | ٧     |      |  |  |

|   | DIGITAL OUTPUT(2) NR                | ST                |                                                  | _                          | _      |                           |       |      |  |  |

|   | Output voltage "L"                  | V <sub>OL8</sub>  | I <sub>OL</sub> = 0 mA                           | -0.3                       | _      | 0.5                       | V     |      |  |  |

|   | Pull-up resistance                  | R <sub>IL8</sub>  | _                                                | 50                         | 100    | 200                       | kΩ    |      |  |  |

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a = 25^{\circ}C \pm 2^{\circ}C$  and test circuit reference.

|            | VBAT = 62.9 V, CVDD = 5.0V, ambient tem |                      |                                                                 |     | Limits |     |      |      |

|------------|-----------------------------------------|----------------------|-----------------------------------------------------------------|-----|--------|-----|------|------|

|            | Parameter                               | Symbol Condition     |                                                                 | Min | Тур    | Max | Unit | Note |

| F          | REGEXT UVLO                             |                      |                                                                 |     |        |     |      |      |

|            | UV detection voltage                    | V <sub>IL_UV1</sub>  | REGSEL pin=L                                                    |     | 4      | _   | V    | *1   |

|            | UV release voltage                      | V <sub>IH_UV1</sub>  | REGSEL pin=L                                                    |     | 4.2    | _   | V    | *1   |

| VDD55 UVLO |                                         |                      |                                                                 |     |        |     |      |      |

|            | UVLO detection voltage                  | $V_{IL\_UV2}$        |                                                                 |     | 4.5    | _   | V    | *1   |

|            | UVLO release voltage                    | V <sub>IH_UV2</sub>  |                                                                 |     | 4.75   |     | V    | *1   |

| ı          | Nch. FET DRIVER                         |                      |                                                                 |     |        |     |      |      |

|            | Drive voltage (DIS="H")                 | V <sub>ON_DIS</sub>  | $V_{ON\_DIS} = V_{DIS} - V_{VPACK}$<br>VGS connect 10M $\Omega$ | 9   | 11     | 13  | V    |      |

|            | Drive voltage (CHG="H")                 | V <sub>ON_CHG</sub>  | $V_{ON\_CHG} = V_{CHG} - V_{VBAT}$ VGS connect 10M $\Omega$     | 9   | 11     | 13  | V    |      |

|            | Drive voltage (DIS="L")                 | V <sub>OFF_DIS</sub> | $V_{OFF\_DIS} = V_{DIS} - V_{VPACK}$ VGS connect 10M $\Omega$   | _   | _      | 0.2 | V    |      |

|            | Drive voltage (CHG="L")                 | V <sub>OFF_CHG</sub> | $V_{OFF\_CHG} = V_{CHG} - V_{VBAT}$ VGS connect 10M $\Omega$    | _   | _      | 0.2 | V    |      |

|            | Rise time (DIS="L" to "H")              | tr                   | $V_{DIS} = 0 \text{ to } 4V$ $C_L = 20 \text{nF}$               | _   | 20     | 50  | μЅ   | *1   |

|            | Rise time (CHG="L" to "H")              | tr                   | $V_{CHG} = 0 \text{ to } 4V$ $C_L = 20 \text{nF}$               | _   | 20     | 50  | μS   | *1   |

|            | Fall time (DIS ="H" to "L")             | tf                   | V <sub>DIS</sub> = 90% to 10%<br>C <sub>L</sub> = 20nF          | _   | 20     | 30  | μЅ   | *1   |

|            | Fall time (CHG="H" to "L")              | tf                   | V <sub>CHG</sub> = 90% to 10%<br>C <sub>L</sub> = 20nF          | _   | 20     | 30  | μS   | *1   |

<sup>\*1 :</sup>Design reference value not tested during final production inspection.

Unless otherwise noted, the characteristics are specified under the recommended operating condition: VBAT = 62.9 V, CVDD = 5.0V, ambient temperature,  $T_a$  = 25°C±2°C and test circuit reference.

| Parameter                    | Symbol                                    | Condition                                       | Limits |     |     | Linit | Note |

|------------------------------|-------------------------------------------|-------------------------------------------------|--------|-----|-----|-------|------|

| Farameter                    | Symbol                                    | Condition                                       | Min    | Тур | Max | Offic | Note |

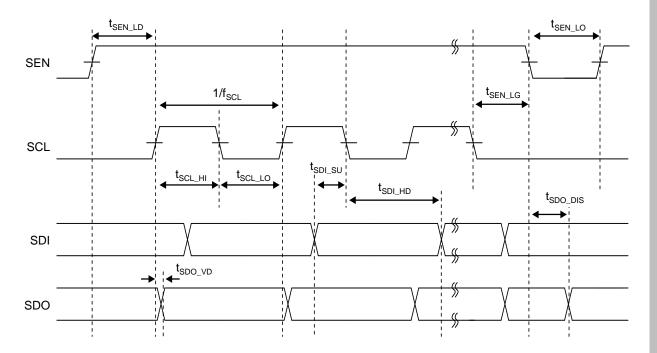

| SPI Interface Timing (SEN, S | SPI Interface Timing (SEN, SDI, SCL, SDO) |                                                 |        |     |     |       |      |

| SCL Frequency                | f <sub>SCL</sub>                          | _                                               |        | _   | 1   | MHz   |      |

| SCL Duty Cycle               | t <sub>DUTY</sub>                         | _                                               | 45     | 50  | 55  | %     |      |

| SEN Rising to SCL Rising     | t <sub>SEN_LD</sub>                       | _                                               | 100    | _   | _   | ns    |      |

| SCL Falling to SEN Falling   | t <sub>SEN_LG</sub>                       | _                                               | 100    |     | _   | ns    |      |

| SEN "L" Width                | t <sub>SEN_LO</sub>                       | _                                               | 500    | _   | _   | ns    |      |

| SDI Setup Time               | t <sub>SDI_SU</sub>                       | SDI valid to SCL falling                        | 100    | _   | _   | ns    |      |

| SDI Hold Time                | t <sub>SDI_HD</sub>                       | SCL falling to SDI valid                        | 100    |     | _   | ns    |      |

| SDO Valid Time               | t <sub>SDO_VD</sub>                       | SCL rising to SDO valid $C_L \le 50 \text{ pF}$ |        | _   | 400 | ns    |      |

| SDO Disable Time             | t <sub>SDO_DIS</sub>                      | SEN falling to SDO disable                      | _      | _   | 400 | ns    |      |

Fig.2.4.1 SPI Timing

■Test Circuit

Electrical characteristics are tested under our recommended 17cell RC filter condition below.

\*1: REGEXT voltage setting can only be set to 5V or 3.3V when using as direct connection with CVDD. There is a requirement for the usage of REGEXT and CVDD total capacitor value.

Please refer to page 23 bottom note (\*3) for more detail.

nuvoton

# **Pin Description**

| Pin | Pin name | Туре          | Description                                                             |

|-----|----------|---------------|-------------------------------------------------------------------------|

| 1   | NRST     | 0             | Power Reset Output Pin (Open Drain)                                     |

| 2   | CVDD     | l<br>(Supply) | Digital Voltage Supply                                                  |

| 3   | TMONI1   | I             | Analog Input Pin                                                        |

| 4   | TMONI2   | I             | Analog Input Pin                                                        |

| 5   | TMONI3   | I             | Analog Input Pin                                                        |

| 6   | TMONI4   | I             | Analog Input Pin                                                        |

| 7   | TMONI5   | I             | Analog Input Pin                                                        |

| 8   | SHDN     | I             | Shutdown Control "L": Active / "H": Shutdown                            |

| 9   | MODE     | I             | Test Mode pin for Manufacturer Use Only (Connect to DVSS always) *1     |

| 10  | AVSS1    | GND           | Analog Ground                                                           |

| 11  | VDD18    | 0             | 1.85V LDO Output Pin for Internal Use                                   |

| 12  | REGSEL   | I             | External 5V/3.3V/2.5V REGEXT output selection Pin                       |

| 13  | REGEXT   | 0             | External 5V/3.3V/2.5V LDO Output Pin                                    |

| 14  | VDD55    | 0             | 5.5V Regulator Output Pin                                               |

| 15  | REGB     | 0             | Base Pin for 5.5V Pre-regulator                                         |

| 16  | AVSS2    | GND           | Analog Ground                                                           |

| 17  | LDM      | I             | Load Detect Pin                                                         |

| 18  | VPC      | I             | Wake Up Signal Pin - "L" Active / "H" Wake Up. Also for Charger Detect. |

| 19  | GPOH2    | 0             | High Voltage General Purpose Output Pin 2 (Open Drain)                  |

| 20  | GPOH1    | 0             | High Voltage General Purpose Output Pin 1 (Open Drain)                  |

<sup>\*1</sup> An external pull-down resistor should be connected to MODE pin and it is internally connected to GND through a 1  $k\Omega$  resistor.

# **Pin Description (continued)**

| Pin | Pin name | Туре          | Description                                             |  |  |

|-----|----------|---------------|---------------------------------------------------------|--|--|

| 21  | CP1      | 0             | Charge Pump Capacitor Pin (Positive Terminal for VPACK) |  |  |

| 22  | CN1      | 0             | Charge Pump Capacitor Pin (Negative Terminal for VPACK) |  |  |

| 23  | CN2      | 0             | harge Pump Capacitor Pin (Negative Terminal for VBAT)   |  |  |

| 24  | CP2      | 0             | Charge Pump Capacitor Pin (Positive Terminal for VBAT)  |  |  |

| 25  | VPACK    | l<br>(Supply) | Positive Terminal of Battery Pack to load or charger.   |  |  |

| 26  | DIS      | 0             | Discharge NMOSFET Gate Drive Pin                        |  |  |

| 27  | CHG      | 0             | Charge NMOSFET Gate Drive Pin                           |  |  |

| 28  | VBAT     | l<br>(Supply) | Stacked Cells Highest Voltage Pin                       |  |  |

| 29  | C17      | I             | Cell 17 Input Pin (+ve)                                 |  |  |

| 30  | C16      | I             | Cell 16 Input Pin (+ve) / Cell 17 Input Pin (-ve)       |  |  |

| 31  | C16M     | I             | Cell 16 Input Pin (-ve)                                 |  |  |

| 32  | NC       | I             | N.C. Pin                                                |  |  |

| 33  | NC       | I             | N.C. Pin                                                |  |  |

| 34  | NC       | I             | N.C. Pin                                                |  |  |

| 35  | NC       | I             | N.C. Pin                                                |  |  |

| 36  | C15      | I             | Cell 15 Input Pin (+ve) / Cell 16 Input Pin (-ve)       |  |  |

| 37  | C14      | I             | Cell 14 Input Pin (+ve) / Cell 15 Input Pin (-ve)       |  |  |

| 38  | C13      | I             | Cell 13 Input Pin (+ve) / Cell 14 Input Pin (-ve)       |  |  |

| 39  | C12      | I             | Cell 12 Input Pin (+ve) / Cell 13 Input Pin (-ve)       |  |  |

| 40  | C11      | I             | Cell 11 Input Pin (+ve) / Cell 12 Input Pin (-ve)       |  |  |

# **Pin Description (continued)**

| Pin | Pin name | Туре | Description                                               |

|-----|----------|------|-----------------------------------------------------------|

| 41  | C10      | I    | Cell 10 Input Pin (+ve) / Cell 11 Input Pin (-ve)         |

| 42  | C9       | I    | Cell 9 Input Pin (+ve) / Cell 10 Input Pin (-ve)          |

| 43  | C8       | I    | Cell 8 Input Pin (+ve) / Cell 9 Input Pin (-ve)           |

| 44  | C7       | I    | Cell 7 Input Pin (+ve) / Cell 8 Input Pin (-ve)           |

| 45  | C6       | I    | Cell 6 Input Pin (+ve) / Cell 7 Input Pin (-ve)           |

| 46  | C5       | I    | Cell 5 Input Pin (+ve) / Cell 6 Input Pin (-ve)           |

| 47  | C4       | I    | Cell 4 Input Pin (+ve) / Cell 5 Input Pin (-ve)           |

| 48  | C3       | I    | Cell 3 Input Pin (+ve) / Cell 4 Input Pin (-ve)           |

| 49  | C2       | I    | Cell 2 Input Pin (+ve) / Cell 3 Input Pin (-ve)           |

| 50  | C1       | I    | Cell 1 Input Pin (+ve) / Cell 2 Input Pin (-ve)           |

| 51  | C0       | I    | Cell 1 Input Pin (-ve)                                    |

| 52  | GND      | GND  | Analog Ground                                             |

| 53  | SRP      | I    | Shunt Resistor Positive Pin                               |

| 54  | NC       | -    | N.C. Pin                                                  |

| 55  | SRN      | I    | Shunt Resistor Negative Pin                               |

| 56  | GPIO1    | I/O  | General Purpose I/O Pin 1                                 |

| 57  | GPIO2    | I/O  | General Purpose I/O Pin 2                                 |

| 58  | GPIO3    | I/O  | General Purpose I/O Pin 3                                 |

| 59  | ALARM1   | 0    | ALARM1 Pin                                                |

| 60  | FETOFF   | ı    | CHG/DIS FET Control Pin - "L" Normal / "H" FET Forced OFF |

| 61  | SDO      | 0    | SPI Interface Pin – Data Out *1                           |

| 62  | SDI      | ı    | SPI Interface Pin – Data In *1                            |

| 63  | SCL      | ı    | SPI Interface Pin – Clock *1                              |

| 64  | SEN      | ı    | SPI Interface Pin – Enable *1                             |

<sup>\*1:</sup> An external capacitor may be required near the unused open pin to increase noise immunity.

# **Block Diagram**

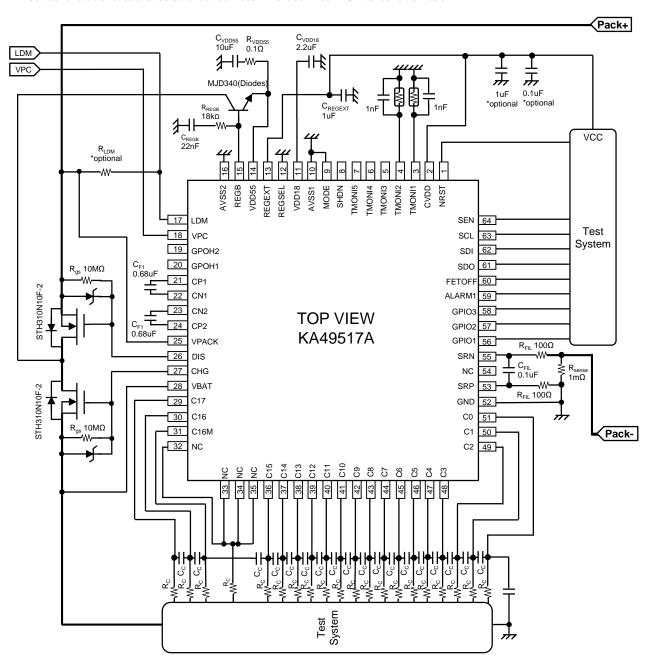

# **B. Application Circuit Example**

\*1: REGEXT voltage setting can only be set to 5V or 3.3V when using as direct connection with CVDD. There is a requirement for the usage of REGEXT and CVDD total capacitor value.

Please refer to page 23 bottom note (\*3) for more detail.

# **Recommended Constant of External Component**

| ltana                                    | Cumple of           |      | Const | ant  |      | Note   |

|------------------------------------------|---------------------|------|-------|------|------|--------|

| Item                                     | Symbol              | Min. | Тур.  | Max. | Unit | Note   |

|                                          | $C_REGB$            | _    | 22    | _    | nF   | *1, *2 |

|                                          | R <sub>REGB</sub>   | _    | 18    | _    | kΩ   | *2     |

|                                          | C <sub>VDD55</sub>  | _    | 10    | _    | μF   | *1, *2 |

|                                          | R <sub>VDD55</sub>  | _    | 0.1   | _    | Ω    | *2     |

|                                          | C <sub>VDD18</sub>  | _    | 2.2   | _    | μF   | *1     |

|                                          | C <sub>REGEXT</sub> | _    | 1     | _    | μF   | *1,*3  |

|                                          | R <sub>GS</sub>     | _    | 10    | _    | ΜΩ   | *2     |

| Constant of components connected to pins | C <sub>F1</sub>     | _    | 0.68  | _    | μF   | *1     |

|                                          | C <sub>F2</sub>     | _    | 0.68  | _    | μF   | *1     |

|                                          | R <sub>C</sub>      | _    | 1     | _    | kΩ   | *5     |

|                                          | C <sub>c</sub>      | _    | 1     | _    | μF   | *1,*4  |

|                                          | R <sub>sense</sub>  | _    | 100   | _    | mΩ   | *6     |

|                                          | R <sub>FIL</sub>    | _    | 100   | _    | Ω    |        |

|                                          | C <sub>FIL</sub>    | _    | 0.1   | _    | μF   | *1     |

|                                          | R <sub>LDM</sub>    | _    | 32.4  | _    | kΩ   | *7     |

- \*1: Use of a ceramic capacitor is recommended.

- \*2: The parameters are applicable for system using an external NPN BJT (Diodes Inc MJD340), as shown in the recommended circuit.

- \*3: REGEXT can be used for as power supply for CVDD pin and external circuit. 1uF capacitor (C<sub>REGEXT</sub>) is necessary at REGEXT output. It is recommended to connect a maximum of 1uF capacitor for CVDD pin and external circuit, which is compatible with default C<sub>VDD55</sub> and VDD55 NPN device (Diodes Inc MJD340)

If it is necessary to increase these total capacitor value at CVDD pin and external circuit, the capacitor C<sub>VDD55</sub> must be increased proportionally with about 5 times ratio to ensure stability. Please note start-up time of VDD55 and REGEXT would increase proportionally by doing this.

- \*4: Usage of C<sub>n</sub> pin input filter Capacitor or Resistor of different value other than the recommended values, or, RC filter connection other than the 17 cells testing circuitry indicated in the Electrical Characteristics, will cause a shift in voltage accuracy.

- \*5: R<sub>C</sub> can be selected based on the required internal MOS Cell Balance function. It is important to maintain the current below its rated value.

- \*6: R<sub>sense</sub> resistor design is based on actual load current needed. This value should not cause SRP and SRN pin to generate voltage out of the sensing range which will affect measurement accuracy.

- \*7: R<sub>LDM</sub> allow user to adjust Load detector threshold based on system requirement.

By using R<sub>LDM</sub> of 32.4k, it is possible to detect LDM threshold of 0.4V when load current of minimum 70uA is drawn at the pin in the case FET is open case.

# **Description of Functions**

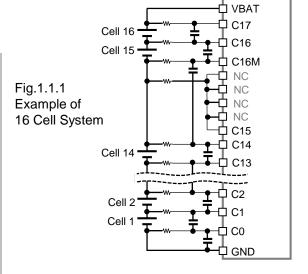

### 1. Battery Connection

The minimum required VBAT pin voltage is 12.5V to guarantee normal operation.

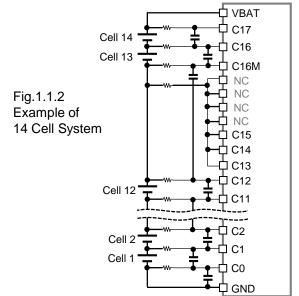

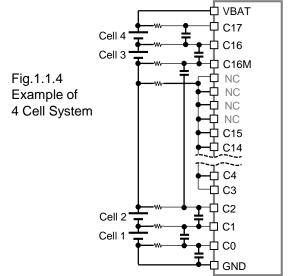

For application using less than 17 cells, all unused cells Cn pins should be connected as shown in figure below, user shall use cells connect to C17, C16, C1 and C2 pins first and followed by battery from lower cell. Please also note that although pin 32 ~ pin 35 are NC pins, they are to be connected as shown in the diagram below to ensure the best measurement performance of other cell pins Battery cells connection sequence:

Connect the GND pin followed by VBAT pin. After that, it should be connected from the lower cell in turn.

$\mathsf{GND} \to \mathsf{VBAT} \to \mathsf{Cell} \ \text{between C0-C1} \to \mathsf{Cell} \ \text{between C1-C2} \to \mathsf{incrementally}$

ט ע א

Figures below are some system example. Minimum VBAT for 4 cells system must be higher than 12.5V.

C17 Cell 12 Cell 11 C16M . ⊐ NС NC Fig.1.1.3 NC Example of NC C15 12 Cell System C11 🗅 C10 Cell 10 □ C2 Cell 2 C1 Cell 1 **GND**

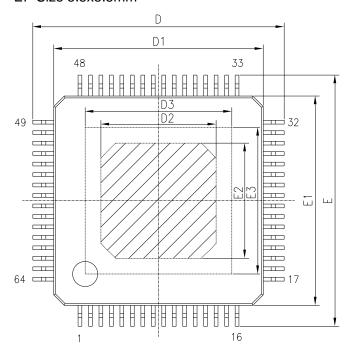

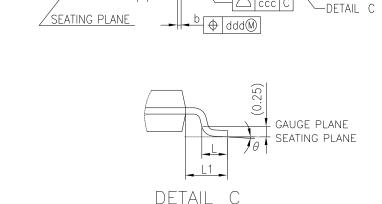

Unit: mm

# **Dimensions**

C

• TQFP 64L 10x10mm<sup>2</sup>, Thickness 1mm, Lead Pitch 0.5mm, Lead Length 1mm, EP Size 5.5x5.5mm

VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

□ ccc C

е

| SYMBOLS | MIN.    | NOM.    | MAX.  |  |

|---------|---------|---------|-------|--|

| А       | _       | _       | 1.20  |  |

| A1      | 0.05    | 0.10    | 0.20  |  |

| A2      | 1.00REF |         |       |  |

| D       | 11.80   | 12.00   | 12.20 |  |

| D1      | 9.90    | 10.00   | 10.10 |  |

| D2      | 5.50    | _       | _     |  |

| D3      | -       | -       | 7.00  |  |

| E       | 11.80   | 12.00   | 12.20 |  |

| E1      | 9.90    | 10.00   | 10.10 |  |

| E2      | 5.50    | _       | -     |  |

| E3      | _       | _       | 7.00  |  |

| L       | 0.45    | 0.60    | 0.75  |  |

| L1      |         | 1.00REF |       |  |

| b       | 0.15    | 0.20    | 0.25  |  |

| С       | 0.10    | 0.15    | 0.20  |  |

| е       | 0.50BSC |         |       |  |

| ddd     | 0.10    |         |       |  |

| ССС     | 0.10    |         |       |  |

| θ       | 0.0°    | _       | 8.0°  |  |

#### **IMPORTANT NOTICE**

- 1. When using the IC for new models, verify the safety including the long-term reliability for each product.

- 2. When the application system is designed by using this IC, please confirm the notes in this book. Please read the notes to descriptions and the usage notes in the book.

- 3. This IC is intended to be used for measuring battery cell voltage in automotive application.

Consult our sales staff in advance for information on the following applications: Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body.

Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as for automotive, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others: Applications of which reliability equivalent to (1) to (7) is required

Our company shall not be held responsible for any damage incurred as a result of or in connection with the IC being used for any special application, unless our company agrees to the use of such special application.

However, for the IC which we designate as products for automotive use, it is possible to be used for automotive.

- 4. This IC is neither designed nor intended for use in automotive applications or environments unless the IC is designated by our company to be used in automotive applications.

- Our company shall not be held responsible for any damage incurred by customers or any third party as a result of or in connection with the IC being used in automotive application, unless our company agrees to such application in this book.

- 5. Please use this IC in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Our company shall not be held responsible for any damage incurred as a result of our IC being used by our customers, not complying with the applicable laws and regulations.

- 6. Pay attention to the direction of the IC. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might be damaged.

- 7. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 8. Perform visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as solder-bridge between the pins of the IC. Also, perform full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the IC during transportation.

- Take notice in the use of this IC that it might be damaged when an abnormal state occurs such as output pin VBAT short, output pin CVDD fault (Power supply fault), output pin-GND short (Ground fault), output-to-output-pin short (load short), or leakage current between pins. Safety measures such as installation of fuses are recommended because the extent of the above-mentioned damage will depend on the current capability of the power supply.

- 10. The protection circuit is for maintaining safety against abnormal operation. Therefore, the protection circuit should not work during normal operation.

- Especially for the thermal protection circuit, if the area of safe operation or the absolute maximum rating is momentarily exceeded due to output pin to VBAT short, output pin to CVDD short (Power supply fault), or output pin to GND short (Ground fault), the IC might be damaged before the thermal protection circuit could operate.

- 11. Verify the risks which might be caused by the malfunctions of external components.

# **Revision History**

# **Control Number Rev 1.00**

| Date | Page | Item            | Before | After |

|------|------|-----------------|--------|-------|

| 25   | _    | Initial Release | _      | _     |

| Dec  |      |                 |        |       |

| 2020 |      |                 |        |       |

#### **Control Number Rev 1.01**

| Date               | Page  | Item                                                                        | Before                       | After                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------|-----------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 16,22 | Bottom note                                                                 |                              | Added note *1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Jan<br>Feb<br>2021 | 23    | Bottom note *3 updated                                                      |                              | REGEXT can be used for as power supply for CVDD pin and external circuit. 1uF capacitor (CREGEXT) is necessary at REGEXT output. It is recommended to connect a maximum of 1uF capacitor for CVDD pin and external circuit, which is compatible with default CVDD55 and VDD55 NPN device (Diodes Inc MJD340) If it is necessary to increase these total capacitor value, the capacitor CVDD55 must be increased proportionally with about 5 times ratio to ensure stability. Please note start-up time of VDD55 and REGEXT would increase proportionally by doing this. |

|                    | 6     | Specs for I <sub>BAT5</sub>                                                 | Min: 0uA<br>Typ:<br>Max: 1uA | Min:<br>Typ: 0uA<br>Max: 1uA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 7     | Specs for V <sub>ACC_VC1</sub><br>Added voltage accuracy<br>room temp value |                              | Added +-5mV specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Control Number Rev 1.03**

| Date               | Page   | Item                                              | Before                                                                                                                                        | After                                                                                                                                                                                                                                        |

|--------------------|--------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>May          | 6 ~ 15 | Added Ambient Temp Ta value in the header portion |                                                                                                                                               | $T_a = 25^{\circ}C \pm 2^{\circ}C$                                                                                                                                                                                                           |