# Battery Monitoring IC For Industry

# KA49503A Product Brief

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation Japan and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing document only for reference purposes of KA49503A Battery Monitoring IC (BM-IC) based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

# **Battery Monitoring IC for Industry**

#### **Features**

KA49503A is a battery monitoring IC with protection function. With high resolution ADC built-in, KA49503A is capable to measure battery cell voltage and current level accurately.

Through SPI serial interface, microcontroller unit (MCU) is able to read the status and measured result by KA49503A. The ALARM pins alert the MCU with the abnormal condition such as over voltage (OV), under voltage (UV), over current (OC) and short circuit (SC).

KA49503A can support an application with up to 16 batteries cells in series or a maximum voltage of 85V, it is suitable for application with high input voltage such as E-bike, UPS etc.

- Maximum support 16 battery cells in series

- 10mV measurement accuracy with 14 bits voltage ADC for cell voltage, and 5 channels analog input measurement

- Built-in 16 bits low speed current measurement ADC (Coulomb Counter) and high speed current measurement ADC

- Low-side shunt sense resistor for current measurement and monitoring

- 2 interrupt pins ADIRQ1, ADIRQ2 for voltage measurement and current measurement

- Operation mode Active, Standby and Shutdown Mode

- SPI serial communication interface up to 1MHz clock with CRC code correction and watchdog timer

- Built-in ALARM pins for overvoltage, undervoltage, overcurrent and short circuit detection and protection feature

- Built-in cell balancing MOSFET, with support of external cell balance MOSFET operation.

- 6 channels General GPIO and 2 channels high voltage output

- High-side Charge (CHG) & Discharge (DIS) N-ch FET driver with built-in charge pump and FETOFF control pin

- 50mA 5V LDO

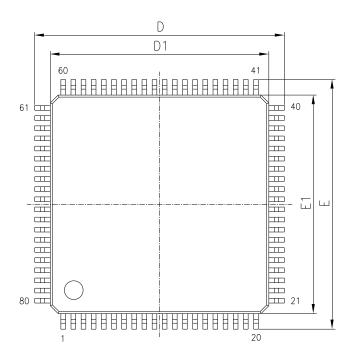

- Package: LQFP 80L (14x14x1.4mm³, Lead Pitch 0.65mm)

# **Application**

Pedelec, e-Bike, UPS, Server Backup System, Power Tool, Energy Storage Systems etc

Note: This IC may not be able to fulfill the functional safety requirements when Automotive grade Laws or Regulations are applied to Electric Bicycles. In this case, please consider using our Automotive Grade ICs.

Rev 1.00

### Table of Contents

| Chapter 1   | Overview           | 4  |

|-------------|--------------------|----|

| Chapter 2   | Battery Connection | 19 |

| Package Inf | ormation           | 20 |

| Important N | otice              | 21 |

# Chapter 1 Overview

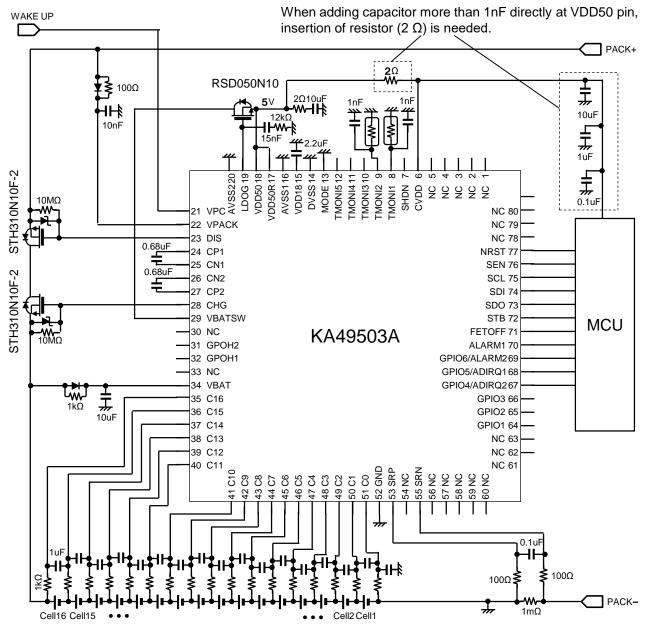

#### 1.1 Recommended Circuit

When connecting a circuit to VDD50, please be careful about below.

- Adding capacitor more than 1nF to VDD50 pin directly is prohibited.

- •When needing capacitor more than 1nF, please use through  $2\Omega$  resistor. Please design as the total capacitor is from 6uF to 16uF.

Note: The recommended circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. Customer is fully responsible for the incorporation of the above illustrated application circuit in the production.

#### 1.2 Electrical Characteristics

#### 1.2.1 ABSOLUTE MAXIMUM RATINGS

| Parameter                      | Symbol                                      | Rating                         | Unit | Notes |

|--------------------------------|---------------------------------------------|--------------------------------|------|-------|

| Cumply voltage                 | $V_{VBAT}$                                  | -0.3 <b>~</b> 99               | V    | *1    |

| Supply voltage                 | $V_{CVDD}$                                  | -0.3 <b>~</b> 6.5              | V    | *1    |

| Operating junction temperature | T <sub>i</sub>                              | -40 <b>~</b> 125               | °C   | *2    |

| Storage temperature            | $T_{stg}$                                   | -55 <b>~</b> 125               | °C   | *2    |

|                                | C16                                         | -0.3 ~ VBAT+1.2                | V    | *3    |

|                                | Cn (n=1~15)                                 | -0.3 ~ VBAT+0.3                | V    | *3    |

|                                | C0                                          | -0.3 <b>~</b> 6.5              | V    |       |

|                                | SEN, SCL, SDI, FETOFF<br>STB, GPIOn (n=1~6) | -0.3 ~ V <sub>CVDD</sub> +0.3  | V    | *4    |

| Input Voltage Range            | TMONIn (n=1∼5),                             | -0.3 ~ V <sub>VDD50</sub> +0.3 | V    | *4    |

|                                | SRP.SRN                                     | -0.5 <b>~</b> 2.0              | V    |       |

|                                | VPC                                         | -0.3 <b>~</b> 99               | V    |       |

|                                | SHDN                                        | -0.3 <b>~</b> 6.5              | V    |       |

|                                | ALARM1,SDO,NRST                             | -0.3 ~ V <sub>CVDD</sub> +0.3  | V    |       |

| Output Voltage Range           | VDD50                                       | -0.3 <b>~</b> 6.5              | V    |       |

|                                | GPOHn (n=1~2)                               | -0.3 <b>~</b> 99               | V    |       |

| Output Current Dange           | ALARM1,SDO,NRST                             | -6.0 <b>~</b> +6.0             | A    | *5    |

| Output Current Range           | GPIOn (n=1∼6)                               | (-12.0 <b>~</b> +12.0)         | mA   | *6    |

| Allowable Voltage Between Pins | $C_n - C_{n-1} (n=1 \sim 16)$               | -0.3 <b>~</b> 11               | V    |       |

Note) This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteed as it is higher than our stated recommended operating range.

When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected. Do not apply external currents and voltages to any pin not specifically mentioned.

- \*1 : The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

- \*2 : Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25  $^{\circ}$ C

- \*3: (VBAT+0.3) & (VBAT+1.2) shall not over 99V.

- \*4 : ( VCVDD + 0.3 ), ( VVDD50 + 0.3 ) must not exceed 6.5V.

- \*5: + Polarity is the direction that flows from the pin to the outside, polarity is the direction that flows from the outside to the pin.

- \*6: This is the rated current at the I / O output drivability setting 2mA. The value of () is the rated current when increasing the I / O output drivability by register settings.

### 1.2.2 POWER DISSIPATION RATING

| Package                                       | θј-а      | θј-с     | P <sub>D</sub> (Ta=25°C) | P <sub>D</sub> (Ta=105°C) |

|-----------------------------------------------|-----------|----------|--------------------------|---------------------------|

| LQFP 80L (14x14x1.4mm³,<br>Lead Pitch 0.65mm) | 55.5 °C/W | 7.2 °C/W | 1.80 W                   | 0.36 W                    |

Note) For the actual usage, please refer to the P<sub>D</sub>-T<sub>a</sub> characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

#### **CAUTION**

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

#### 1.2.3 RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Pin Name                      | Min.  | Тур. | Max.               | Unit | Notes |

|----------------------------------|-------------------------------|-------|------|--------------------|------|-------|

| Cupply voltage range             | $V_{VBAT}$                    | 12.5  | 59.2 | 85                 | V    |       |

| Supply voltage range             | V <sub>CVDD</sub>             | 3.0   | 5.0  | 5.5                | V    |       |

|                                  | $C_n - C_{n-1} (n=1 \sim 16)$ | 0     | _    | 5.0                | V    |       |

|                                  | SEN, SCL, SDI                 | 0     | _    | V <sub>CVDD</sub>  | V    |       |

|                                  | TMONIn (n=1∼5)                | 0     | _    | 5.0                | V    |       |

| Input Voltage Range              | GPIOn (n=1∼6)                 | 0     | _    | V <sub>CVDD</sub>  | V    |       |

|                                  | SRP,SRN                       | -0.18 | _    | 0.18               | V    |       |

|                                  | VPC                           | 0     | _    | 85                 | V    |       |

|                                  | SHDN                          | 0     | _    | V <sub>VDD50</sub> | V    |       |

| Operating Ambient<br>Temperature | Ta <sub>opr</sub>             | -40   | 25   | 105                | °C   |       |

### 1.2.4 ELECTRICAL CHARACTERISTICS

|   | Parameter                           |                   | Condition                                                                         |      | Limits |      | Unit | Noto |  |

|---|-------------------------------------|-------------------|-----------------------------------------------------------------------------------|------|--------|------|------|------|--|

|   |                                     |                   | Condition                                                                         | Min  | Тур    | Max  |      | note |  |

| s | SUPPLY CURRENT                      |                   |                                                                                   |      |        |      |      |      |  |

|   | VBAT Active Mode                    | I <sub>BAT1</sub> |                                                                                   | _    | 3.1    | 3.9  | mA   |      |  |

|   | VBAT Standby Mode                   | I <sub>BAT2</sub> | 5VLDO:Low Power,<br>Coulomb Counter:off<br>FDRV:Intermittent<br>Communication:off | _    | 0.15   | 0.30 | mA   |      |  |

|   | VBAT Shutdown Mode                  | I <sub>BAT3</sub> |                                                                                   | 0    | _      | 1    | μΑ   |      |  |

| 5 | VLDO                                |                   |                                                                                   |      |        |      |      |      |  |

|   | VDD50 Output Voltage                | V <sub>VDD</sub>  |                                                                                   | 4.75 | 5.0    | 5.25 | V    |      |  |

|   | VDD50 Drive Current                 | I <sub>VDD1</sub> | Normal mode                                                                       | 0    | _      | 50   | mA   |      |  |

|   | VDD50 Drive Current                 | I <sub>VDD2</sub> | Low Power mode                                                                    | 0    |        | 5    | mA   |      |  |

| С | CELL BALANCING CONTROL OUTPUT (CBn) |                   |                                                                                   |      |        |      |      |      |  |

|   | Output Impedance                    | Z <sub>CB</sub>   | ⊿Cn = 3.0V ~ 5.0V                                                                 | _    | 12.5   | 20   | Ω    |      |  |

| Dovometer                         | Cymahal                      | Condition                                                             |            | Limits |     | Unit | Niete |

|-----------------------------------|------------------------------|-----------------------------------------------------------------------|------------|--------|-----|------|-------|

| Parameter                         | Symbol Condition             |                                                                       | Min        | Тур    | Max | Unit | Note  |

| CELL VOLTAGE MONITOR              |                              |                                                                       |            |        |     |      |       |

| Input Voltage Range               | ΔCn                          | $C_n - C_{n-1} (n=1 \sim 16)$                                         | 0          | _      | 5   | V    |       |

| Voltage Resolution                | $V_{RES}$                    | 14bits                                                                |            | 0.3    | _   | mV   | *1    |

| Voltage Accuracy1                 | V <sub>ACC_VC1</sub>         | $\Delta$ Cn = 2.0V $\sim$ 4.3 V                                       | -10        | _      | 10  | mV   |       |

| Voltage Accuracy2                 | V <sub>ACC_VC2</sub>         | $\Delta$ Cn = 2.0V ~ 4.3 V<br>Ta = -30°C ~ 65°C                       | -10        |        | 10  | mV   | *2    |

| Conversion Time                   | t <sub>conv</sub>            | time/cell                                                             |            | 50     | _   | μS   | *1    |

| Cell Measurement Input<br>Current | I <sub>IN</sub>              | Active mode                                                           | <b>–</b> 5 |        | 5   | μА   |       |

| Input Leakage Current             | I <sub>LK</sub>              | Shutdown mode                                                         | -1         |        | 1   | μА   |       |

| OVER / UNDER VOLTAGE DET          | ECTOR (                      | OV / UV)                                                              |            |        |     |      |       |

| OV detection threshold step       | V <sub>ACC_OV</sub>          | 2.0~4.5V@6bit                                                         | _          | 50     | _   | mV   | *1    |

| UV detection threshold step       | V <sub>ACC_UV</sub>          | 0.5~3.0V@6bit                                                         |            | 50     |     | mV   | *1    |

| VPACK CELL VOLTAGE MONI           | TOR                          |                                                                       |            |        |     | -    |       |

| Input Voltage Range               | V <sub>IN</sub>              |                                                                       | 0          |        | 85  | V    |       |

| Voltage Resolution                | V <sub>RES</sub>             | 14bits                                                                |            | 6.1    | _   | mV   | *1    |

| Voltage Accuracy1                 | V <sub>ACC</sub> _<br>VPACK1 | V <sub>VPACK</sub> = 12.5V ∼ 72V                                      | -1         |        | 1   | V    |       |

| Voltage Accuracy2                 | V <sub>ACC</sub> _<br>VPACK2 | $V_{VPACK} = 12.5V \sim 72V$<br>$T_a = -30^{\circ}C \sim 65^{\circ}C$ | -1         | _      | 1   | V    | *2    |

<sup>\*1 :</sup> It is a design center value.

<sup>\*2</sup> It is design value. The inspection is not done.

at  $V_{VBAT}$  =  $V_{VPACK}$  = 59.2 V ,  $V_{CVDD}$  = 5.0V Note: unless otherwise noted, Operating Ambient Temperature is  $T_a$  = 25°C±2°C

|                  | Parameter                                        |                    | Condition                                                                                     | Limits |     |     | Unit | Note     |

|------------------|--------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|--------|-----|-----|------|----------|

|                  | Parameter                                        | Condition          |                                                                                               | Min    | Тур | Max | Unit | note     |

| -                | ΓΜΟΝΙ1-5 VOLTAGE MONITOR                         |                    |                                                                                               |        |     |     |      |          |

|                  | Input Voltage Range                              | V <sub>IN</sub>    |                                                                                               | 0      |     | 5   | V    |          |

|                  | Voltage Resolution                               | V <sub>RES</sub>   | 14bits                                                                                        | _      | 0.3 | _   | mV   | *1       |

|                  | Voltage Accuracy1                                | V <sub>ACC</sub> _ | VIN = 0.4V~4.7V<br>Not use Pull-up Resistance                                                 | -10    | _   | 10  | mV   |          |

|                  | Voltage Accuracy2                                | V <sub>ACC</sub> _ | VIN = $0.4V \sim 4.7V$<br>Not use Pull-up Resistance<br>$T_a = -30^{\circ}C \sim 65^{\circ}C$ | -10    |     | 10  | mV   | *3       |

|                  | Input Pull-up Resistance                         | R <sub>PU</sub>    |                                                                                               | 7      | 10  | 13  | kΩ   |          |

|                  | Input Pull-up Resistance Temperature coefficient | RT <sub>PU</sub>   | $T_a = -30^{\circ}C \sim 65^{\circ}C$                                                         | -1.0   | _   | 1.0 | %    | *3       |

| THERMAL SHUTDOWN |                                                  |                    |                                                                                               |        |     |     |      |          |

|                  | Shutdown Threshold                               | T <sub>SD2</sub>   | Тј                                                                                            | 150    | 175 | 200 | °C   | *2<br>*3 |

<sup>\*1:</sup> It is a design center value.

<sup>\*2 :</sup> When thermal shutdown occurs, all circuitry is shutdown. Following wake up (to active mode) sequence in order to restart.

<sup>\*3:</sup> It is design value. The inspection is not done.

| Parameter                                         | Symbo               | Symbo Condition                         |       | Limits |      |      | Not  |  |  |  |

|---------------------------------------------------|---------------------|-----------------------------------------|-------|--------|------|------|------|--|--|--|

| Parameter                                         | I                   |                                         |       | Тур    | Max  | Unit | INOI |  |  |  |

| OW SPEED CURRENT MONIT                            | TOR (SRF            | P,SRN)                                  |       |        |      |      |      |  |  |  |

| Input Voltage Range                               | $V_{IN}$            |                                         | -180  | _      | 180  | mV   |      |  |  |  |

| Voltage Resolution                                | V <sub>RES</sub>    | 16bits                                  | _     | 5.493  |      | μV   | */   |  |  |  |

| Voltage Accuracy1                                 | V <sub>ACC</sub> _  | VIN = 100mV                             | -1000 | _      | 1000 | μV   |      |  |  |  |

| Voltage Accuracy2                                 | V <sub>ACC</sub> _  | VIN = 10mV                              | -150  | _      | 150  | μV   | **   |  |  |  |

| Voltage Accuracy3                                 | V <sub>ACC</sub> _  | VIN = 1mV                               | -25   | _      | 25   | μV   | **   |  |  |  |

| HIGH SPEED CURRENT MONITOR (SRP,SRN)              |                     |                                         |       |        |      |      |      |  |  |  |

| Input Voltage Range                               | $V_{IN}$            |                                         | -180  | _      | 180  | mV   |      |  |  |  |

| Voltage Resolution                                | V <sub>RES</sub>    | 15bits                                  | _     | 10.99  | _    | μV   | *    |  |  |  |

| Voltage Accuracy1                                 | V <sub>ACC</sub>    | VIN = 100mV                             | -1000 | _      | 1000 | μV   |      |  |  |  |

| Voltage Accuracy2                                 | V <sub>ACC</sub>    | VIN = 10mV                              | -150  | _      | 150  | μV   | *    |  |  |  |

| Voltage Accuracy3                                 | V <sub>ACC</sub>    | VIN = 1mV                               | -50   | _      | 50   | μV   | *    |  |  |  |

| CURRENT PROTECTION (SRP                           | ,SRN)               |                                         |       |        |      |      |      |  |  |  |

| Over Current in Charge<br>Detection Accuracy1     | V <sub>CP_OCC</sub> | Detection Threshold<br>10mV             | -5    | _      | 5    | mV   | *2   |  |  |  |

| Over Current in Charge Detection Accuracy2        | V <sub>CP_OCC</sub> | Detection Threshold from 20mV to 100mV  | -10   | _      | 10   | mV   | *2   |  |  |  |

| Over Current in Charge<br>Detection Accuracy3     | V <sub>CP_OCC</sub> | Detection Threshold from 100mV to 200mV | -10   | _      | 10   | %    | *2   |  |  |  |

| Over Current in Discharge<br>Detection Accuracy1  | V <sub>CP_OCD</sub> | Detection Threshold from 25mV to 100mV  | -10   | _      | 10   | mV   | *2   |  |  |  |

| Over Current in Discharge<br>Detection Accuracy2  | V <sub>CP_OCD</sub> | Detection Threshold from 100mV to 800mV | -10   | _      | 10   | %    | *2   |  |  |  |

| Short Circuit in Discharge<br>Detection Accuracy1 | V <sub>CP_SCD</sub> | Detection Threshold from 50mV to 100mV  | -10   | _      | 10   | mV   | *2   |  |  |  |

| Short Circuit in Discharge Detection Accuracy2    | V <sub>CP_SCD</sub> | Detection Threshold from 100mV to 800mV | -10   | _      | 10   | %    | *2   |  |  |  |

<sup>\*1 :</sup> It is a design center value.

<sup>\*2 :</sup> It is a design verification value. The inspection is not done.

| Darameter                   | Symbol                          | Condition              | Limits                    |          | Unit                    | Note |      |  |  |

|-----------------------------|---------------------------------|------------------------|---------------------------|----------|-------------------------|------|------|--|--|

| Parameter                   | Symbol                          | Condition              | Min                       | Тур      | Max                     | Unit | note |  |  |

| GENERAL PURPOSE INPUT/O     | UTPUT (G                        | PIO)                   |                           |          |                         |      |      |  |  |

| Input Voltage "H"           | V <sub>IH</sub>                 |                        | V <sub>CVDD</sub> × 0.8   | <u>—</u> | V <sub>CVDD</sub>       | V    |      |  |  |

| Input Voltage "L"           | V <sub>IL</sub>                 |                        | 0                         | _        | V <sub>CVDD</sub> × 0.2 | V    |      |  |  |

| Output Voltage "H"          | V <sub>OH</sub>                 | I <sub>OH</sub> = -1mA | V <sub>CVDD</sub><br>-0.6 | _        | V <sub>CVDD</sub> +0.3  | V    |      |  |  |

| Output Voltage "L"          | V <sub>OL</sub>                 | I <sub>OL</sub> = +1mA | -0.3                      |          | 0.4                     | V    |      |  |  |

| GENERAL PURPOSE HV OUTF     | GENERAL PURPOSE HV OUTPUT (GPO) |                        |                           |          |                         |      |      |  |  |

| Output Voltage "L"          | V <sub>OL</sub>                 | I <sub>OL</sub> = +1mA | -0.3                      |          | 7.0                     | V    |      |  |  |

| DIGITAL INPUT(1) VPC        |                                 | •                      | '                         |          | •                       |      |      |  |  |

| Input Voltage "H"           | V <sub>IH</sub>                 |                        | 4.0                       | _        | _                       | V    |      |  |  |

| Input Voltage "L"           | V <sub>IL</sub>                 |                        | _                         |          | 0.3                     | V    |      |  |  |

| Pull-down resistance        | R <sub>IL</sub>                 |                        | 6                         | 28       | 55                      | МΩ   |      |  |  |

| DIGITAL INPUT(2) SHDN       |                                 |                        |                           |          | •                       |      |      |  |  |

| Input Voltage "H"           | V <sub>IH</sub>                 |                        | 3.0                       | _        | _                       | V    |      |  |  |

| Input Voltage "L"           | V <sub>IL</sub>                 |                        | _                         |          | 0.1                     | V    |      |  |  |

| Pull-down resistance        | R <sub>IL</sub>                 |                        | 200                       | 820      | 1500                    | kΩ   |      |  |  |

| DIGITAL INPUT(3) SDI,SCL,SE | N,FETOFF                        | ,STB                   |                           |          |                         |      |      |  |  |

| Input Voltage "H"           | V <sub>IH</sub>                 |                        | V <sub>CVDD</sub> × 0.8   | _        | V <sub>CVDD</sub>       | V    |      |  |  |

| Input Voltage "L"           | V <sub>IL</sub>                 |                        | 0                         | _        | V <sub>CVDD</sub> × 0.2 | V    |      |  |  |

| Input Leakage Current       | I <sub>LK</sub>                 |                        | -1                        | 0        | 1                       | μΑ   |      |  |  |

| DIGITAL OUTPUT(1) ALARM1,   | SDO                             |                        |                           |          |                         |      |      |  |  |

| Output Voltage "H"          | V <sub>OH</sub>                 | I <sub>OH</sub> = -1mA | V <sub>CVDD</sub><br>-0.6 | _        | V <sub>CVDD</sub> +0.3  | V    |      |  |  |

| Output Voltage "L"          | V <sub>OL</sub>                 | I <sub>OL</sub> = +1mA | -0.3                      |          | 0.4                     | V    |      |  |  |

| DIGITAL OUTPUT(2) NRST      |                                 |                        |                           |          |                         | 1    |      |  |  |

| Output voltage "L"          | V <sub>OL</sub>                 | I <sub>OL</sub> = 0 mA | -0.3                      |          | 0.5                     | V    |      |  |  |

| Pull-up resistance          | R <sub>IL</sub>                 | _                      | 50                        | 100      | 200                     | kΩ   |      |  |  |

at V<sub>VBAT</sub> = V<sub>VPACK</sub> = 59.2 V , V<sub>CVDD</sub> = 5.0V Note: unless otherwise noted, Operating Ambient Temperature is T<sub>a</sub> = 25°C  $\pm$ 2°C

| Devemates                   | Currele el           | Condition                                                        | Limits |      |     | Unit I | Nata     |  |

|-----------------------------|----------------------|------------------------------------------------------------------|--------|------|-----|--------|----------|--|

| Parameter                   | Symbol Condition     |                                                                  | Min    | Тур  | Max | Unit   | Note     |  |

| CVDD UV                     |                      |                                                                  |        |      |     |        |          |  |

| UV detection voltage        | V <sub>IL_UV</sub>   | _                                                                | _      | 2.45 | _   | V      | *1<br>*2 |  |

| UV release voltage          | V <sub>IH_UV</sub>   | _                                                                | _      | 2.80 | _   | ٧      | *1       |  |

| Hysteresis voltage          | V <sub>HYS_UV</sub>  |                                                                  | _      | 0.35 | _   | ٧      | *1       |  |

| VDD50 UVLO                  |                      |                                                                  |        |      |     | •      |          |  |

| UVLO detection voltage      | V <sub>IL_UVLO</sub> |                                                                  | _      | 4.00 | _   | V      | *1<br>*3 |  |

| Nch. FET DRIVER             | Nch. FET DRIVER      |                                                                  |        |      |     |        |          |  |

| Drive voltage (DIS="H")     | V <sub>ON_DIS</sub>  | $V_{ON\_DIS} = V_{DIS} - V_{VPACK}$<br>VGS connect 10M $\Omega$  | 9      | 11   | 13  | V      |          |  |

| Drive voltage (CHG="H")     | V <sub>ON_CHG</sub>  | $V_{ON\_CHG} = V_{CHG} - V_{VBAT}$ VGS connect 10M $\Omega$      | 9      | 11   | 13  | V      |          |  |

| Drive voltage (DIS="L")     | V <sub>OFF_DIS</sub> | $V_{OFF\_DIS} = V_{DIS} - V_{VPACK}$<br>VGS connect 10M $\Omega$ | _      | _    | 0.2 | V      |          |  |

| Drive voltage (CHG="L")     | V <sub>OFF_CHG</sub> | $V_{OFF\_CHG} = V_{CHG} - V_{VBAT}$ VGS connect 10M $\Omega$     | _      | _    | 0.2 | V      |          |  |

| Rise time (DIS="L" to "H")  | tr                   | $V_{DIS} = 10\% \text{ to } 90\%$<br>$C_{L} = 47 \text{nF}$      | _      | 0.8  | 1.6 | ms     |          |  |

| Rise time (CHG="L" to "H")  | tr                   | $V_{CHG} = 10\% \text{ to } 90\%$<br>$C_{L} = 47 \text{nF}$      | _      | 0.8  | 1.6 | ms     |          |  |

| Fall time (DIS ="H" to "L") | tf                   | $V_{DIS} = 90\% \text{ to } 10\%$<br>$C_{L} = 47 \text{nF}$      | _      | 0.5  | 1.0 | ms     |          |  |

| Fall time (CHG="H" to "L")  | tf                   | $V_{CHG} = 90\% \text{ to } 10\%$ $C_{L} = 47 \text{nF}$         | _      | 0.5  | 1.0 | ms     |          |  |

<sup>\*1 :</sup> It is a design center value.

<sup>\*2 :</sup> When detecting the CVDD UV, CVDD\_UV flag (CVDD\_STAT: bp2) is set to "0".

<sup>\*3:</sup> When detecting the VDD50 UVLO, it will be switched to the Shutdown mode. (if VPC pin is "L")

| Parameter                       | Cymbal               | Symbol Condition —                              |     | Limits |     |       | Note |

|---------------------------------|----------------------|-------------------------------------------------|-----|--------|-----|-------|------|

| Parameter                       | Symbol               | Condition                                       | Min | Тур    | Max | Uniii | note |

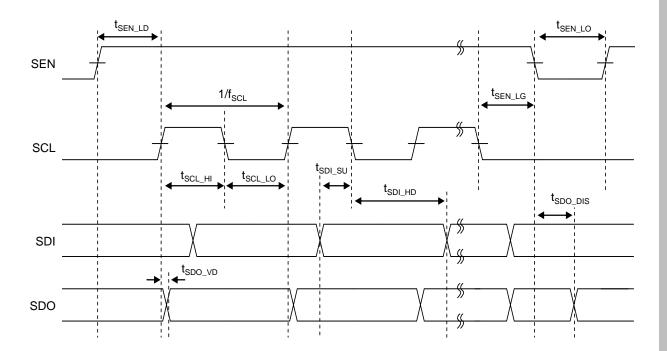

| SPI Interface Timing (SEN, SDI, | SCL, SD              | 00)                                             |     |        |     |       |      |

| SCL Frequency                   | f <sub>SCL</sub>     | _                                               | _   | _      | 1   | MHz   |      |

| SCL Duty Cycle                  | t <sub>DUTY</sub>    | _                                               | 45  | 50     | 55  | %     |      |

| SEN Rising to SCL Rising        | t <sub>SEN_LD</sub>  | _                                               | 100 | _      | _   | ns    |      |

| SCL Falling to SEN Falling      | t <sub>SEN_LG</sub>  | _                                               | 100 | _      | _   | ns    |      |

| SEN "L" Width                   | t <sub>SEN_LO</sub>  | _                                               | 500 | _      | _   | ns    |      |

| SDI Setup Time                  | t <sub>SDI_SU</sub>  | SDI valid to SCL falling                        | 100 | _      | _   | ns    |      |

| SDI Hold Time                   | t <sub>SDI_HD</sub>  | SCL falling to SDI valid                        | 100 | _      |     | ns    |      |

| SDO Valid Time                  | t <sub>SDO_VD</sub>  | SCL rising to SDO valid $C_L \le 50 \text{ pF}$ | _   | _      | 400 | ns    |      |

| SDO Disable Time                | t <sub>SDO_DIS</sub> | SEN falling to SDO disable                      |     | _      | 400 | ns    |      |

Fig.2.4.1 SPI Timing

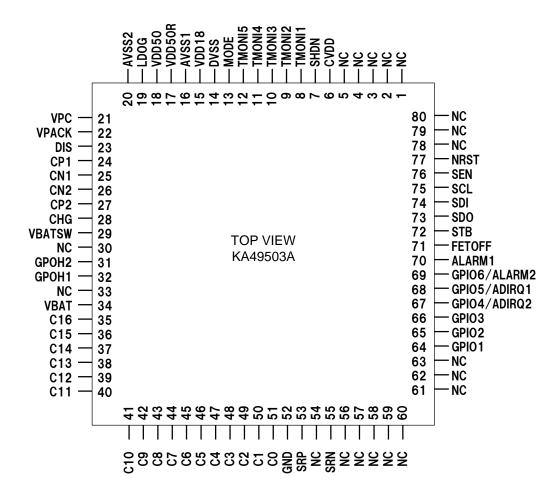

#### 1.3 PIN CONFIGURATION

# 1.4 PIN FUNCTIONS

| Pin No. | Pin name | Туре               | Description                                                                     |

|---------|----------|--------------------|---------------------------------------------------------------------------------|

| 1       | NC       | -                  | N.C. Pin                                                                        |

| 2       | NC       | -                  | N.C. Pin                                                                        |

| 3       | NC       | -                  | N.C. Pin                                                                        |

| 4       | NC       | -                  | N.C. Pin                                                                        |

| 5       | NC       | -                  | N.C. Pin                                                                        |

| 6       | CVDD     | I(Supply)          | Digital Voltage Supply                                                          |

| 7       | SHDN     | I                  | Shutdown Control "L": Active mode / "H": Shutdown mode                          |

| 8       | TMONI1   | I                  | Analog Input Pin 1                                                              |

| 9       | TMONI2   | I                  | Analog Input Pin 2                                                              |

| 10      | TMONI3   | I                  | Analog Input Pin 3                                                              |

| 11      | TMONI4   | I                  | Analog Input Pin 4                                                              |

| 12      | TMONI5   | I                  | Analog Input Pin 5                                                              |

| 13      | MODE     | I                  | Test Mode Pin for Manufacturer Use Only (Connect to DVSS always)                |

| 14      | DVSS     | GND                | Digital Ground                                                                  |

| 15      | VDD18    | 0                  | 1.85V LDO Output Pin for Internal Use                                           |

| 16      | AVSS1    | GND                | Analog Ground                                                                   |

| 17      | VDD50R   | I                  | (To be connected to VDD50 pin)                                                  |

| 18      | VDD50    | 0                  | 5V Output Pin                                                                   |

| 19      | LDOG     | 0                  | Gate Control Pin for 5V LDO NMOS Gate Pin                                       |

| 20      | AVSS2    | GND                | Analog Ground                                                                   |

| 21      | VPC      | I                  | Wake Up Signal Pin<br>"H" Wake Up, Please be always fixed to "L" after Wake Up. |

| 22      | VPACK    | I(Power<br>Supply) | Positive Pin for Battery Pack                                                   |

| 23      | DIS      | 0                  | Discharge NMOSFET Gate Drive Pin                                                |

| 24      | CP1      | 0                  | Charge Pump Capacitor Pin (Positive Pin for VPACK)                              |

| 25      | CN1      | 0                  | Charge Pump Capacitor Pin (Negative Pin for VPACK)                              |

| 26      | CN2      | 0                  | Charge Pump Capacitor Pin (Negative Pin for VBAT)                               |

| 27      | CP2      | 0                  | Charge Pump Capacitor Pin (Positive Pin for VBAT)                               |

| 28      | CHG      | 0                  | Charge NMOSFET Gate Drive Pin                                                   |

| 29      | VBATSW   | 0                  | Power Pin for 5V LDO NMOS Drain Pin                                             |

| 30      | NC       | -                  | N.C. Pin                                                                        |

nuvoTon

| Pin No. | Pin name             | Туре | Description                                            |  |

|---------|----------------------|------|--------------------------------------------------------|--|

| 31      | GPOH2                | 0    | High Voltage General Purpose Output Pin 2 (Open Drain) |  |

| 32      | GPOH1                | 0    | High Voltage General Purpose Output Pin 1 (Open Drain) |  |

| 33      | NC                   | -    | N.C. Pin                                               |  |

| 34      | VBAT I(Power Supply) |      | Battery Top Most Pin                                   |  |

| 35      | C16                  | I    | Cell 16 Input Pin (+ve)                                |  |

| 36      | C15                  | I    | Cell 15 Input Pin (+ve) / Cell 16 Input Pin (-ve)      |  |

| 37      | C14                  | I    | Cell 14 Input Pin (+ve) / Cell 15 Input Pin (-ve)      |  |

| 38      | C13                  | I    | Cell 13 Input Pin (+ve) / Cell 14 Input Pin (-ve)      |  |

| 39      | C12                  | I    | Cell 12 Input Pin (+ve) / Cell 13 Input Pin (-ve)      |  |

| 40      | C11                  | I    | Cell 11 Input Pin (+ve) / Cell 12 Input Pin (-ve)      |  |

| 41      | C10                  | I    | Cell 10 Input Pin (+ve) / Cell 11 Input Pin (-ve)      |  |

| 42      | C9                   | I    | Cell 9 Input Pin (+ve) / Cell 10 Input Pin (-ve)       |  |

| 43      | C8                   | I    | Cell 8 Input Pin (+ve) / Cell 9 Input Pin (-ve)        |  |

| 44      | C7                   | I    | Cell 7 Input Pin (+ve) / Cell 8 Input Pin (-ve)        |  |

| 45      | C6                   | I    | Cell 6 Input Pin (+ve) / Cell 7 Input Pin (-ve)        |  |

| 46      | C5                   | I    | Cell 5 Input Pin (+ve) / Cell 6 Input Pin (-ve)        |  |

| 47      | C4                   | I    | Cell 4 Input Pin (+ve) / Cell 5 Input Pin (-ve)        |  |

| 48      | C3                   | I    | Cell 3 Input Pin (+ve) / Cell 4 Input Pin (-ve)        |  |

| 49      | C2                   | I    | Cell 2 Input Pin (+ve) / Cell 3 Input Pin (-ve)        |  |

| 50      | C1                   | I    | Cell 1 Input Pin (+ve) / Cell 2 Input Pin (-ve)        |  |

| 51      | C0                   | I    | Cell 1 Input Pin (-ve)                                 |  |

| 52      | GND                  | GND  | Analog Ground                                          |  |

| 53      | SRP                  | I    | Shunt Resistor Positive Pin                            |  |

| 54      | NC                   | -    | N.C. Pin                                               |  |

| 55      | SRN                  | I    | Shunt Resistor Negative Pin                            |  |

| 56      | NC                   | -    | N.C. Pin                                               |  |

| 57      | NC                   | -    | N.C. Pin                                               |  |

| 58      | NC                   | -    | N.C. Pin                                               |  |

| 59      | NC                   | -    | N.C. Pin                                               |  |

| 60      | NC                   | -    | N.C. Pin                                               |  |

| Pin<br>No. | Pin name     | Туре | Description                                                   |  |

|------------|--------------|------|---------------------------------------------------------------|--|

| 61         | NC           | -    | N.C. Pin                                                      |  |

| 62         | NC           | -    | N.C. Pin                                                      |  |

| 63         | NC           | -    | N.C. Pin                                                      |  |

| 64         | GPIO1        | I/O  | General Purpose I/O Pin 1                                     |  |

| 65         | GPIO2        | I/O  | General Purpose I/O Pin 2                                     |  |

| 66         | GPIO3        | I/O  | General Purpose I/O Pin 3                                     |  |

| 67         | GPIO4/ADIRQ2 | I/O  | General Purpose I/O Pin 4 / ADIRQ2 Pin                        |  |

| 68         | GPIO5/ADIRQ1 | I/O  | General Purpose I/O Pin 5 / ADIRQ1 Pin                        |  |

| 69         | GPIO6/ALARM2 | I/O  | General Purpose I/O Pin 6 / ALARM2 Pin                        |  |

| 70         | ALARM1       | 0    | ALARM1 Pin                                                    |  |

| 71         | FETOFF       | I    | CHG/DIS FET Control Pin - "L" Normal / "H" FET Forced OFF     |  |

| 72         | STB          | I    | Standby Mode Control Pin - "L" Active mode / "H" Standby mode |  |

| 73         | SDO          | 0    | SPI Interface Pin – Data Out                                  |  |

| 74         | SDI          | I    | SPI Interface Pin – Data In                                   |  |

| 75         | SCL          | I    | SPI Interface Pin – Clock                                     |  |

| 76         | SEN          | I    | SPI Interface Pin – Enable                                    |  |

| 77         | NRST         | 0    | Power Reset Output Pin (Open Drain)                           |  |

| 78         | NC           |      | N.C. Pin                                                      |  |

| 79         | NC           | -    | N.C. Pin                                                      |  |

| 80         | NC           | -    | N.C. Pin                                                      |  |

nuvoTon

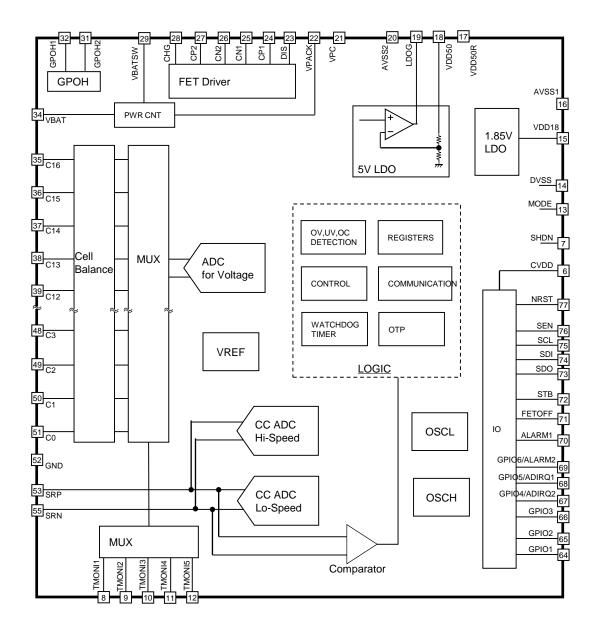

### 1.5 FUNCTIONAL BLOCK DIAGRAM

## **Chapter 2 Battery Connection**

The minimum required VBAT pin voltage is 12.5V to guarantee normal operation.

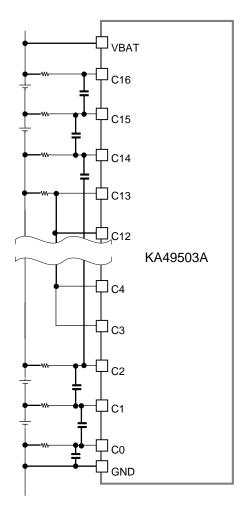

For application using less than 16 cells, all unused cells Cn pins should be connected as shown in figure below, user shall use cells connect to C16, C15, C1 and C2 pins first and follow by battery from lower cell.

#### Battery cells connection sequence:

Connect the GND pin followed by VBAT pin. After that, it should be connected from the lower cell in turn. GND -> VBAT -> Cell between C0-C1 -> Cell between C1-C2 -> •••

Figures below show example connection for 15 battery cells and 4 battery cells, please note, it is possible to be connected for 4 battery cells only when the minimum VBAT is higher then 12.5V.

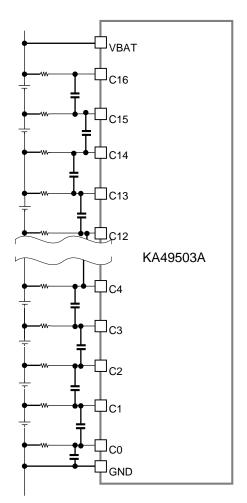

Fig.2.1.1 KA49503A Cell Connection example with 15 cell connected

Fig.2.1.2 KA49503A Cell Connection Example with only 4 cell connected

# Package Information

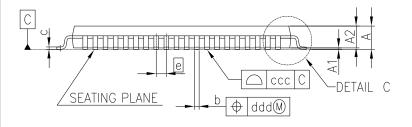

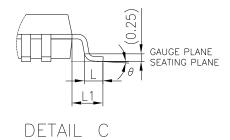

LQFP080 14x14mm<sup>2</sup>, Thickness 1.4mm, Lead\_Pitch 0.65mm, Lead\_Length 1.00mm

#### VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

|         |       | I       |       |

|---------|-------|---------|-------|

| SYMBOLS | MIN.  | NOM.    | MAX.  |

| А       | -     | _       | 1.70  |

| A1      | 0.00  | 0.10    | 0.20  |

| A2      |       | 1.40REF |       |

| D       | 15.80 | 16.00   | 16.20 |

| D1      | 13.90 | 14.00   | 14.10 |

| Е       | 15.80 | 16.00   | 16.20 |

| E1      | 13.90 | 14.00   | 14.10 |

| L       | 0.45  | 0.60    | 0.75  |

| L1      |       | 1.00REF |       |

| b       | 0.25  | 0.30    | 0.35  |

| С       | 0.10  | 0.15    | 0.20  |

| е       |       | 0.65BSC |       |

| ССС     |       | 0.10    |       |

| ddd     |       | 0.13    |       |

| θ       | 0.0°  | _       | 8.0°  |

### Important Notice

- 1. When using the IC for new models, verify the safety including the long-term reliability for each product.

- 2. When the application system is designed by using this IC, please confirm the notes in this book. Please read the notes to descriptions and the usage notes in the book.

- 3. This IC is intended to be used for general electronic equipment.

Consult our sales staff in advance for information on the following applications: Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body.

Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as automobile, transportation vehicle such as automobile, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others: Applications of which reliability equivalent to (1) to (7) is required

Our company shall not be held responsible for any damage incurred as a result of or in connection with the IC being used for any special application, unless our company agrees to the use of such special application. However, for the IC which we designate as products for automotive use, it is possible to be used for automotive.

- 4. This IC is neither designed nor intended for use in automotive applications or environments unless the IC is designated by our company to be used in automotive applications.

- Our company shall not be held responsible for any damage incurred by customers or any third party as a result of or in connection with the IC being used in automotive application, unless our company agrees to such application in this book.

- 5. Please use this IC in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Our company shall not be held responsible for any damage incurred as a result of our IC being used by our customers, not complying with the applicable laws and regulations.

- 6. Pay attention to the direction of the IC. When mounting it in the wrong direction onto the PCB (printed-circuit-board),

- it might be damaged.

- 7. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins.

- In addition, refer to the Pin Description for the pin configuration.

- 8. Perform visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as solder-bridge between the pins of the IC. Also, perform full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the IC during transportation.

- 9. Take notice in the use of this IC that it might be damaged when an abnormal state occurs such as output pin-VCC short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short). Safety measures such as installation of fuses are recommended because the extent of the above-mentioned damage will depend on the current capability of the power supply.

- 10. This IC may be changed in order to improve the performance without notice, please make sure the latest specification is used before your final design.

# **Revision History**

| Date      | Revision | Description          |

|-----------|----------|----------------------|

| 2021.1.28 | 1.00     | 1. initially issued. |

|           |          |                      |

#### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.