## Multicell Battery Stack Monitor IC

# KA49511A Product Brief

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation Japan and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing document only for reference purposes of KA49511A Battery Monitoring IC(BM-IC) based system design. Nuvoton assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

For additional information or question, please contact Nuvoton Technology Corporation Japan. www.nuvoton.co.jp

#### ■ IMPORTANT NOTICE

Regarding the specifications of this product, it is considered that you have agreed to the quality level and disclaimer described below.

Support for industry standards and quality standards

| Functional safety standards for<br>automobiles ISO26262 | Νο    |

|---------------------------------------------------------|-------|

| AECQ-100                                                | Νο    |

| Market failure rate                                     | 50Fit |

#### **Disclaimer**

- When the application system is designed using this IC, please design the system at your own risk. Please read, consider, and apply appropriate usage notes and description in this standard.

When designing your application system, please take into the consideration of break down and failure mode occurrence and possibility in semiconductor products. Measures on the systems such as, but not limited to, redundant design, mitigating the spread of fire, or preventing glitch, are recommended in order to prevent physical injury, fire, social damages, etc. in using the Nuvoton Technology Japan Corporation (hereinafter referred to as NTCJ) products.

- 3. When using this IC, for each actual application systems, verify the systems and the all functionality of this IC as intended in application systems and the safety including the long-term reliability at your own risk

- 4. Please use this IC in compliance with all applicable laws, regulations and safety-related requirements that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. NTCJ shall not be held responsible for any damage incurred as a result of this IC being used not in compliance with the applicable laws, regulations and safety-related requirements.

- 5. This IC does not have any security functions using cryptographic algorithms, such as authentication, encryption, tampering detection.

- 6. Unless this IC is indicated by NTCJ to be used in applications as meeting the requirements of a particular industry standard (e.g., ISO 9001, IATF 16949, ISO 26262, etc.), this IC is neither designed nor intended for use in such environments for that applications. NTCJ shall not be held responsible for not meeting the requirements of a particular industry standard.

- 7. Using IC that have been indicated as compliant with industry functional safety standards does not warrant that the application meets the requirements of industry functional safety standards. NTCJ shall not be held responsible for the application compliance with requirements of the particular industry functional safety standard.

- 8. Unless this IC is indicated by NTCJ to be used in applications as meeting the requirements of a particular quality standard (e.g., AECQ-100, etc.), this IC is neither designed nor intended for use in such the environments for that applications. NTCJ shall not be held responsible for not meeting the requirements of a particular quality standard.

- 9. In case of damages, costs, losses, and/or liabilities incurred by NTCJ arising from customer's noncompliance with above from 1 to 8, customer will indemnify NTCJ against every damages, costs, losses and responsibility.

### Table of Contents

| Important Notice                                  | <br>2  |

|---------------------------------------------------|--------|

| Overview                                          | <br>4  |

| Features                                          | <br>4  |

| Applications                                      | <br>4  |

| Package                                           | <br>4  |

| Туре                                              | <br>4  |

| Block Diagram                                     | <br>5  |

| Application Circuit Example                       | <br>6  |

| Pin Description                                   | <br>7  |

| Absolute Maximum Ratings                          | <br>9  |

| Operating Supply Voltage Range                    | <br>9  |

| Allowable Current and Voltage Range               | <br>10 |

| Electrical Characteristics                        | <br>11 |

| Test Circuit Diagram                              | <br>19 |

| Usage Notes                                       | <br>20 |

| Special Attention and Precautions in Using the IC | <br>20 |

| Notes for Power IC                                | <br>20 |

# Multicell Battery Stack Monitor IC

## Overview

KA49511A is a multicell battery stack monitor IC.

This IC, capable of voltage measurement of up to 10 battery cells connected in series with maximum 45-V input common mode voltage, is optimized for applications such as batteries for electrical bicycles requiring high-voltage operation.

The IC has the control of the cell balancing switches, the control of the high-side N-channel MOSFET for charge and discharge and a built-in regulator necessary for the peripheral circuits.

#### Features

- Voltage measurement of up to 10 battery cells

- High accuracy voltage detection (total 10 cells)

- Control signal output for cell balance switch

- Built-in 14-bit delta-sigma ADC

- High-side N-channel MOSFET control for charge and discharge

- Serial control with microcomputer interface

#### Applications

• Voltage measurement for lithium-ion battery. (electrical bicycle, power tool, UPS, etc.)

#### Package

• TQFP 56L (10x10x1mm<sup>3</sup>, Lead Pitch 0.65mm)

#### Туре

Bi-CMOS IC

Measurement accuracy: ±10 mV

## nuvoTon

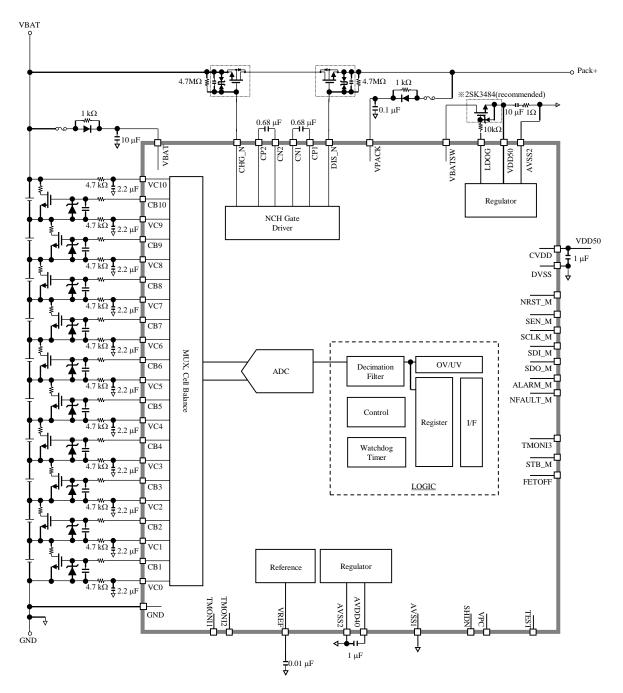

Block Diagram

Note) This block diagram is for explaining functions. Some circuit blocks may be omitted, or simplified.

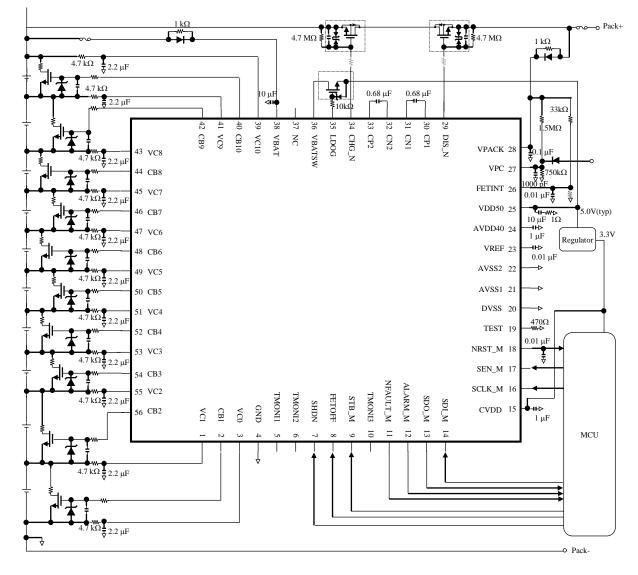

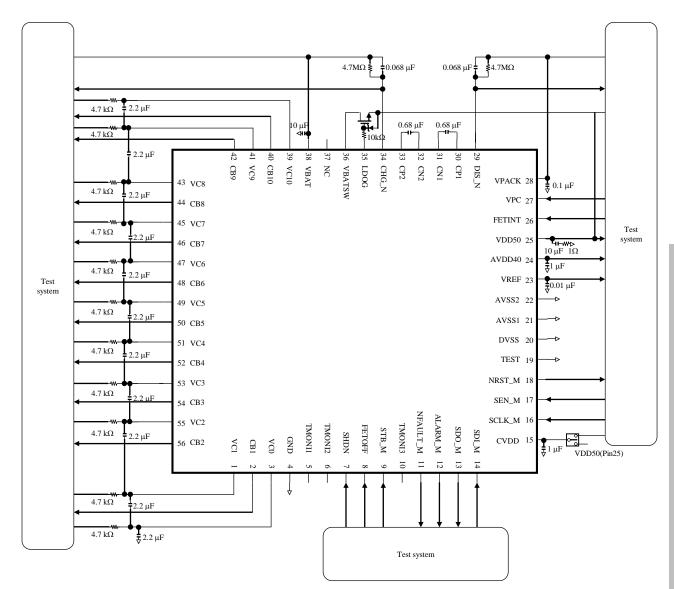

Application Circuit Example

#### Notes)

- This application circuit is an example. Operation of mass production set is not guaranteed. Perform enough evaluation and verification on the design of mass production set in customer's responsibility.

- $\cdot$  Use external resistors with accuracy of less than ±5%.

- $\cdot$  Use external capacitors with accuracy of less than  $\pm 10\%.$

# nuvoTon

## Pin Description

| Pin No. | Name     | Туре         | Description                                                              |

|---------|----------|--------------|--------------------------------------------------------------------------|

| 1       | VC1      | Input        | Cell 2 voltage input (-)/ cell 1 voltage input (+)                       |

| 2       | CB1      | Output       | Control pin for the transistor of cell balance                           |

| 3       | VC0      | Input        | Cell 1voltage input (-)                                                  |

| 4       | GND      | Ground       | Ground for analog circuit                                                |

| 5       | TMONI1   |              | Test pin 1                                                               |

| 6       | TMONI2   | _            | Test pin 2                                                               |

| 7       | SHDN     | Input        | Shutdown control signal input ("L": active, "H": shutdown)               |

| 8       | FETOFF   | Input        | External FET ON/OFF select ("L": normal, "H": forced OFF)                |

| 9       | STB_M    | Input        | Standby control signal input ("L": active, "H": standby)                 |

| 10      | TMONI3   | _            | Test pin 3                                                               |

| 11      | NFAULT_M | Output       | FAULT output for microcomputer interface                                 |

| 12      | ALARM_M  | Output       | ALARM signal output                                                      |

| 13      | SDO_M    | Output       | Serial data output for microcomputer interface                           |

| 14      | SDI_M    | Input        | Serial data input for microcomputer interface                            |

| 15      | CVDD     | Power supply | Supply voltage for digital I/O                                           |

| 16      | SCLK_M   | Input        | Serial clock input for microcomputer interface                           |

| 17      | SEN_M    | Input        | SPI for microcomputer interface enable ("H": enable)                     |

| 18      | NRST_M   | Output       | Power-on reset output for microcomputer                                  |

| 19      | TEST     | Input        | Test mode select (* Connect to DVSS fixed.)                              |

| 20      | DVSS     | Ground       | Ground for digital circuit                                               |

| 21      | AVSS1    | Ground       | Ground for analog circuit                                                |

| 22      | AVSS2    | Ground       | Ground for analog circuit                                                |

| 23      | VREF     | Output       | Reference voltage for ADC: 2.0 V (typ)                                   |

| 24      | AVDD40   | Output       | Internal regulator pin for analog circuit: 4.0 V (typ)                   |

| 25      | VDD50    | Output       | Sense pin for external high withstand voltage regulator: 5.0 V (typ)     |

| 26      | FETINT   | Input        | Internal switch for pre-charge ("L": pre-charge OFF, "H": pre-charge ON) |

| 27      | VPC      | Input        | Wake up control signal input ("L": active, "H": wake up)                 |

| 28      | VPACK    | Power supply | Positive voltage of battery pack                                         |

| 29      | DIS_N    | Output       | N-channel FET gate drive (for discharge)                                 |

| 30      | CP1      | Output       | Connection to charge pump capacitor (V <sub>PACK</sub> -side, positive)  |

| 31      | CN1      | Output       | Connection to charge pump capacitor (V <sub>PACK</sub> -side, negative)  |

| 32      | CN2      | Output       | Connection to charge pump capacitor (V <sub>BAT</sub> -side, negative)   |

| 33      | CP2      | Output       | Connection to charge pump capacitor (V <sub>BAT</sub> -side, positive)   |

| 34      | CHG_N    | Output       | N-channel FET gate drive (for charge)                                    |

### ■ Pin Description (continued)

| Pin No. | Name   | Туре         | Description                                         |

|---------|--------|--------------|-----------------------------------------------------|

| 35      | LDOG   | Output       | Connection to external power transistor (gate)      |

| 36      | VBATSW | Output       | Connection to external power transistor (drain)     |

| 37      | NC     |              | N.C.                                                |

| 38      | VBAT   | Power supply | Maximum voltage                                     |

| 39      | VC10   | Input        | Cell 10 voltage input (+)                           |

| 40      | CB10   | Output       | Control pin for the transistor of cell balance      |

| 41      | VC9    | Input        | Cell 10 voltage input (-)/ cell 9 voltage input (+) |

| 42      | CB9    | Output       | Control pin for the transistor of cell balance      |

| 43      | VC8    | Input        | Cell 9 voltage input (-)/ cell 8 voltage input (+)  |

| 44      | CB8    | Output       | Control pin for the transistor of cell balance      |

| 45      | VC7    | Input        | Cell 8 voltage input (-)/ cell 7 voltage input (+)  |

| 46      | CB7    | Output       | Control pin for the transistor of cell balance      |

| 47      | VC6    | Input        | Cell 7 voltage input (-)/ cell 6 voltage input (+)  |

| 48      | CB6    | Output       | Control pin for the transistor of cell balance      |

| 49      | VC5    | Input        | Cell 6 voltage input (-)/ cell 5 voltage input (+)  |

| 50      | CB5    | Output       | Control pin for the transistor of cell balance      |

| 51      | VC4    | Input        | Cell 5 voltage input (-)/ cell 4 voltage input (+)  |

| 52      | CB4    | Output       | Control pin for the transistor of cell balance      |

| 53      | VC3    | Input        | Cell 4 voltage input (-)/ cell 3 voltage input (+)  |

| 54      | CB3    | Output       | Control pin for the transistor of cell balance      |

| 55      | VC2    | Input        | Cell 3 voltage input (-)/ cell 2 voltage input (+)  |

| 56      | CB2    | Output       | Control pin for the transistor of cell balance      |

#### Absolute Maximum Ratings

Note) The absolute maximum ratings are the limit values beyond which the IC may be damaged. Operation is not guaranteed under these conditions.

| A No. | Parameter                     | Symbol            | Rating      | Unit | Notes  |

|-------|-------------------------------|-------------------|-------------|------|--------|

|       |                               | V <sub>PACK</sub> | 46          | V    | *1, *2 |

| 1     | 1 Supply voltage              | V <sub>BAT</sub>  | 46          | V    | *1, *2 |

|       |                               | V <sub>CVDD</sub> | 6.5         | V    | *1     |

| 2     | Supply current                | I <sub>CC</sub>   | _           | А    | _      |

| 3     | Power dissipation             | P <sub>D</sub>    | 127         | mW   | *3     |

| 4     | Operating ambient temperature | T <sub>opr</sub>  | -40 to +105 | °C   | *4     |

| 5     | Storage temperature           | T <sub>stg</sub>  | -55 to +125 | °C   | *4     |

Notes)

- \*1: The values are defined, provided that the IC is used within all of the above absolute maximum ratings including the power dissipation.

- \*2: When not using FET driver control functions, supply voltage (absolute maximum rating) is 58 V. In this case, set NPD\_FDRV, FET\_CHG, FET\_CHG (0x01) = [0, 0, 0].

- \*3: The power dissipation shown is the value at Ta = 105°C for the independent (unmounted) IC package without a heat sink.

When using this IC, refer to the PD-Ta diagram of the package standard and design the heat radiation with sufficient margin not to exceed the

allowable value based on the conditions of power supply voltage, load, and ambient temperature.

\*4: All ratings are at T<sub>a</sub> = 25°C, except the power dissipation, operating ambient temperature, and storage temperature.

#### Operating Supply Voltage Range

| Parameter            | Symbol            | Range           | Unit | Notes  |

|----------------------|-------------------|-----------------|------|--------|

| Supply voltage range | V <sub>BAT</sub>  | 12.5 to 45      | V    | *1, *2 |

|                      | V <sub>PACK</sub> | 12.5 to 45      | V    | *1, *2 |

|                      | V <sub>CVDD</sub> | 3.2 to $V_{DD}$ | V    | *1,*3  |

Notes)

- \*1: The value is defined, provided that the IC is used within all of the above absolute maximum ratings including the power dissipation.

- \*2: When not using FET driver control functions, supply voltage range is 12.5 V to 53 V.

In this case, set NPD\_FDRV, FET\_CHG, FET\_CHG (0x01) = [0, 0, 0].

\*3: V<sub>DD</sub> is the voltage of VDD50 pin (No.25 pin). CVDD pin can directly be connected with VDD50 pin.

#### Allowable Current and Voltage Range

Notes)

- The allowable current and voltage ranges are the limit values beyond which the IC may be damaged. Operation is not guaranteed under these conditions.

- •Rating voltages are voltages on each pin, with respect to the GND. GND is voltage of GND, AVSS1, AVSS2, and DVSS. (GND = AVSS1 = AVSS2 = DVSS)

- Do not apply external current or voltages to any pins except mentioned below.

- •For the circuit currents, "+" denotes current flowing into the IC, and "-" denotes current flowing out from the IC.

| Pin<br>No. | Pin Name | Rating Voltage                    | Unit | Notes |

|------------|----------|-----------------------------------|------|-------|

| 1          | VC1      | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |

| 2          | CB1      | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |

| 3          | VC0      | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |

| 7          | SHDN     | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2    |

| 8          | FETOFF   | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2    |

| 9          | STB_M    | -0.3 to 6.5                       | v    |       |

| 11         | NFAULT_M | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2,4  |

| 12         | ALARM_M  | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2,4  |

| 13         | SDO_M    | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2,4  |

| 14         | SDI_M    | -0.3 to 6.5                       | v    |       |

| 16         | SCLK_M   | -0.3 to 6.5                       | v    |       |

| 17         | SEN_M    | -0.3 to 6.5                       | v    |       |

| 18         | NRST_M   | -0.3 to 6.5                       | v    | *4    |

| 19         | TEST     | -0.3 to (V <sub>CVDD</sub> + 0.3) | v    | *2    |

| 25         | VDD50    | -0.3 to 6.5                       | V    | *4    |

| 26         | FETINT   | -0.3 to (V <sub>PACK</sub> + 0.3) | V    | *1    |

| 27         | VPC      | -0.3 to (V <sub>PACK</sub> + 0.3) | v    | *1    |

| e IC, and "-" denotes current flowing out from the IC. |                                      |                                   |      |       |  |  |  |  |  |

|--------------------------------------------------------|--------------------------------------|-----------------------------------|------|-------|--|--|--|--|--|

| Pin<br>No.                                             | Pin Name                             | Rating Voltage                    | Unit | Notes |  |  |  |  |  |

| 29                                                     | DIS_N                                | -0.3 to 58V                       | V    | *1,4  |  |  |  |  |  |

| 30                                                     | CP1                                  | -0.3 to 58V                       | v    | *1,4  |  |  |  |  |  |

| 31                                                     | CN1                                  | -0.3 to (V <sub>PACK</sub> + 0.3) | v    | *1,4  |  |  |  |  |  |

| 32                                                     | CN2                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1,4  |  |  |  |  |  |

| 33                                                     | CP2                                  | -0.3 to 58V                       | v    | *1,4  |  |  |  |  |  |

| 34                                                     | CHG_N                                | -0.3 to 58V                       | v    | *1,4  |  |  |  |  |  |

| 39                                                     | VC10                                 | -0.3 to (V <sub>BAT</sub> + 1.2)  | v    | *1    |  |  |  |  |  |

| 40                                                     | CB10                                 | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 41                                                     | VC9                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 42                                                     | CB9                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 43                                                     | VC8                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 44                                                     | CB8                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 45                                                     | VC7                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 46                                                     | CB7                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 47                                                     | VC6                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 48                                                     | CB6                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 49                                                     | VC5                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 50                                                     | CB5                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 51                                                     | VC4                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 52                                                     | CB4                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | v    | *1    |  |  |  |  |  |

| 53                                                     | VC3                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | V    | *1    |  |  |  |  |  |

| 54                                                     | CB3                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | V    | *1    |  |  |  |  |  |

| 55                                                     | VC2                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | V    | *1    |  |  |  |  |  |

| 56                                                     | CB2                                  | -0.3 to (V <sub>BAT</sub> + 0.3)  | V    | *1    |  |  |  |  |  |

| _                                                      | VC <sub>n+1</sub> to VC <sub>n</sub> | -0.3 to 11                        | V    | *3    |  |  |  |  |  |

|                                                        | CB <sub>n</sub> to VC <sub>n-1</sub> | -0.3 to 11                        | V    | *3    |  |  |  |  |  |

| _                                                      | VC <sub>n</sub> to CB <sub>n</sub>   | -0.3 to 11                        | V    | *3    |  |  |  |  |  |

Notes) \*1:  $(V_{BAT} + 0.3) V$ ,  $(V_{BAT} + 1.2) V$ , (VBAT + 16) V,  $(V_{PACK} + 0.3) V$  and  $(V_{PACK} + 13) V$  must not exceed 58 V. \*2:  $(V_{CVDD} + 0.3) V$  must not exceed 6.5 V

\*3: n = 1 to 10

\*4: These pins are output, so you don't apply external voltage.

### Electrical Characteristics at $V_{BAT} = V_{PACK} = 37 \text{ V}$ Note) $T_a = 25^{\circ}C \pm 3^{\circ}C$ , unless otherwise specified.

| В    | Deveneter                                                            | Cump al              | Test    | Conditions                                   |     | Limits |     | Unit | Natas |

|------|----------------------------------------------------------------------|----------------------|---------|----------------------------------------------|-----|--------|-----|------|-------|

| No.  | Parameter                                                            | Symbol               | Circuit | it Conditions                                | Min | Тур    | Max | Unit | Notes |

| Supp | Ny Current (V <sub>BAT</sub> + V <sub>PACK</sub> + V <sub>CVDD</sub> | )                    |         |                                              |     |        |     |      |       |

| A1   | Active mode                                                          | I <sub>BAT1</sub>    | 1       | $V_{CVDD} = 5.0V$                            |     | 9      | 11  | mA   | —     |

| A2   | Standby mode                                                         | I <sub>BAT2</sub>    | 1       | $V_{CVDD} = 5.0V$                            | _   | 250    | 500 | μA   | *1    |

| A4   | Shutdown (2)                                                         | I <sub>BAT4</sub>    | 1       | $V_{CVDD} = 5.0V$                            | 0   |        | 1   | μΑ   |       |

| LDO  |                                                                      |                      |         |                                              |     |        |     |      |       |

| B1   | VDD50 output voltage                                                 | V <sub>DD</sub>      | 1       |                                              | 4.5 | 5.0    | 5.5 | v    | _     |

| B2   | VDD drive current (1)                                                | I <sub>REG1</sub>    | 1       | Active mode                                  | 0   |        | 25  | mA   | —     |

| B3   | VDD drive current (2)                                                | I <sub>REG2</sub>    | 1       | Standby mode                                 | 0   |        | 5   | mA   | —     |

| DC E | lias                                                                 |                      |         |                                              |     |        |     |      |       |

| B4   | AVDD40 pin voltage                                                   | V <sub>AVDD</sub>    | 1       |                                              | 3.8 | 4.0    | 4.2 | v    |       |

| B5   | VREF pin voltage                                                     | V <sub>REF</sub>     | 1       |                                              | 1.8 | 2.0    | 2.2 | V    | _     |

| Cell | Voltage Monitor                                                      |                      |         |                                              |     |        |     |      |       |

| D1   | Input voltage range                                                  | $\Delta VC_n$        | 1       |                                              | 0   |        | 5   | V    | *3    |

| D3   | Voltage accuracy (1)<br>Average                                      | V <sub>ACC_VC1</sub> | 1       | $\Delta VC_n = 2.5 \text{ V}, 4.5 \text{ V}$ | -10 | 0      | 10  | mV   | *4    |

| D4   | Voltage accuracy (2)<br>Average                                      | V <sub>ACC_VC2</sub> | 1       | $\Delta VC_n = 1.3 V$                        | -50 | 0      | 50  | mV   | *4    |

| D6   | Conversion time                                                      | t <sub>CONV</sub>    | 1       |                                              | 7   | 8      | 9   | ms   | *5    |

| D7   | Effective input current                                              | I <sub>IN</sub>      | 1       | Active mode<br>$\Delta VC_n = 5.0 V$         | -5  | 0      | 5   | μΑ   |       |

| D8   | Input leakage current                                                | I <sub>LK</sub>      | 1       | Shutdown mode<br>$\Delta VC_n = 5.0 V$       | -1  | 0      | 1   | μA   |       |

Notes) \*1: The value is defined in low power consumption mode. (see page 22)

\*3: Exceeding the voltage described above might generate rush current due to the clamp in the internal circuit.

\*4:  $V_{BAT} \geq$  12.5 V, or  $V_{BAT} \geq$  6.5 V and  $V_{PACK} \geq$  12.5 V

\*5: The value is required time for voltage measurement of 10 cells.

#### ■ Electrical Characteristics at V<sub>BAT</sub> = V<sub>PACK</sub> = 12.5 V to 45 V (reference value for design) Note) Ta= -40°C to 105°C, unless otherwise specified.

Note) These characteristics are reference values for design, and all ICs have not been guaranteed through inspections. If, by any chance, the problem caused by these characteristics occurs, we will respond in good faith to user concerns.

|        |                                              | 1                    | 1       |                                                                                         |      |         |       |      |       |

|--------|----------------------------------------------|----------------------|---------|-----------------------------------------------------------------------------------------|------|---------|-------|------|-------|

| В      | Parameter                                    | Symbol               | Test    | Conditions                                                                              | Refe | rence v | alues | Unit | Notes |

| No.    |                                              | Cynhoer              | Circuit | Conditions                                                                              | Min  | Тур     | Max   |      |       |

| Supp   | ly Current ( $V_{BAT} + V_{PACK} + V_{CVDI}$ | <sub>D</sub> )       |         |                                                                                         |      |         |       |      |       |

| A1     | Active mode                                  | I <sub>BAT1</sub>    |         | $V_{CVDD} = 5.0V$                                                                       | _    | 9       | 11    | mA   | _     |

| A2     | Standby mode                                 | I <sub>BAT2</sub>    |         | $V_{CVDD} = 5.0V$                                                                       | _    | 250     | 500   | μΑ   | *1    |

| A3     | Shutdown (1)                                 | I <sub>BAT3</sub>    | _       | $V_{CVDD} = 5.0V$<br>$T_a = -40^{\circ}C$ to 105°C                                      | 0    |         | 5     | μA   |       |

| A4     | Shutdown (2)                                 | I <sub>BAT4</sub>    | _       | $V_{CVDD} = 5.0V$<br>$T_a = -40^{\circ}C$ to $65^{\circ}C$                              | 0    |         | 1     | μA   | _     |

| LDO    |                                              |                      |         |                                                                                         |      |         |       |      |       |

| B1     | VDD50 output voltage                         | V <sub>DD</sub>      |         |                                                                                         | 4.5  | 5.0     | 5.5   | v    | _     |

| B2     | VDD drive current (1)                        | I <sub>REG1</sub>    |         | Active mode                                                                             | 0    | _       | 25    | mA   |       |

| B3     | VDD drive current (2)                        | I <sub>REG2</sub>    |         | Standby mode                                                                            | 0    |         | 5     | mA   | _     |

| DC B   | ias                                          | ·                    |         |                                                                                         |      |         |       |      |       |

| B4     | AVDD40 pin voltage                           | V <sub>AVDD</sub>    |         |                                                                                         | 3.8  | 4.0     | 4.2   | v    |       |

| B5     | VREF pin voltage                             | V <sub>REF</sub>     |         |                                                                                         | 1.8  | 2.0     | 2.2   | v    | _     |

| Therr  | nal Shutdown                                 |                      |         | 1                                                                                       |      | 1       | 1     |      |       |

| C1     | Shutdown threshold                           | T <sub>THUT</sub>    |         | Тј                                                                                      | _    | 170     | _     | °C   | *2    |

| Cell \ | /oltage Monitor                              |                      |         |                                                                                         | 1    | 1       | 1     |      |       |

| D1     | Input voltage range                          | ΔVC <sub>n</sub>     | _       |                                                                                         | 0    |         | 5     | v    | *3    |

| D2     | Voltage resolution                           | V <sub>RES</sub>     | _       | 0.3  mV/LSB<br>T <sub>a</sub> = -30°C to 65°C                                           | _    | 14      |       | Bits | _     |

| D3     | Voltage accuracy (1)<br>Average              | V <sub>ACC_VC1</sub> | _       | $\Delta VC_n = 2.5 V \text{ to } 4.5 V$<br>T <sub>a</sub> = -30°C to 65°C               | -10  | 0       | 10    | mV   | *4    |

| D4     | Voltage accuracy (2)<br>Average              | V <sub>ACC_VC2</sub> | _       | $\Delta VC_n = 1.3 V \text{ to } 2.5 V$<br>$T_a = -30^{\circ}C \text{ to } 65^{\circ}C$ | -50  | 0       | 50    | mV   | *4    |

| D5     | Voltage accuracy (3)<br>Standard deviation   | V <sub>ACC_VC3</sub> | _       | $\Delta VC_n = 2.5 V \text{ to } 4.5 V$<br>$T_a = -30^{\circ}C \text{ to } 65^{\circ}C$ | _    |         | 3     | mV   | *4    |

| D6     | Conversion time                              | t <sub>CONV</sub>    |         | _                                                                                       | 7    | 8       | 9     | ms   | *5    |

| D7     | Effective input current                      | I <sub>IN</sub>      | _       | Active mode<br>$\Delta VC_n = 0 V \text{ to } 5.0 V$                                    | -5   | 0       | 5     | μA   | _     |

| D8     | Input leakage current                        | I <sub>LK</sub>      | _       | Shutdown mode<br>$\Delta VC_n = 0 V$ to 5.0 V                                           | -1   | 0       | 1     | μA   | _     |

Notes) \*1: The value is defined in low power consumption mode. (see page 22)

\*2: When Thermal Shutdown is activated, all circuits are shut down. Therefore, run the wake up sequence again.

\*3: Exceeding the voltage described above might generate rush current due to the clamp in the internal circuit.

\*4:  $V_{BAT} \geq$  12.5 V, or  $V_{BAT} \geq$  6.5 V and  $V_{PACK} \geq$  12.5 V

\*5: The value is required time for voltage measurement of 10 cells.

# Electrical Characteristics at $V_{BAT} = V_{PACK} = 37 \text{ V}$ (continued) Note) $T_a = 25^{\circ}C \pm 3^{\circ}C$ , unless otherwise specified.

| в      | Descention                                | Ourseland            | Test        | O a stitle s a                                                        |                            | Limits            |                            | Unit |       |  |  |

|--------|-------------------------------------------|----------------------|-------------|-----------------------------------------------------------------------|----------------------------|-------------------|----------------------------|------|-------|--|--|

| No.    | Parameter                                 | Symbol               | Circui<br>t | Conditions                                                            | Min                        | Тур               | Max                        | Unit | Notes |  |  |

| Cell I | Cell Balancing Control Output             |                      |             |                                                                       |                            |                   |                            |      |       |  |  |

| G1     | Output voltage (High)                     | V <sub>CB1</sub>     |             |                                                                       | VC <sub>n</sub><br>- 0.2   | VC <sub>n</sub>   | VC <sub>n</sub><br>+ 0.2   | v    | _     |  |  |

| G2     | Output voltage (Low)                      | V <sub>CB2</sub>     |             |                                                                       | VC <sub>n-1</sub><br>- 0.2 | VC <sub>n-1</sub> | VC <sub>n-1</sub><br>+ 0.2 | V    |       |  |  |

| G3     | Discharge Switch-On Resistance<br>(CB1-9) | R <sub>CB1</sub>     |             | $\Delta VC_n \gamma 3V$                                               | _                          | 5                 | 6.5                        | kΩ   | _     |  |  |

| G4     | Discharge Switch-On Resistance<br>(CB10)  | R <sub>CB2</sub>     |             | $\Delta VC_n \gamma 3V$                                               | _                          | 12.5              | 16.3                       | kΩ   | _     |  |  |

| N-ch   | annel FET Drive                           |                      |             | ·                                                                     |                            |                   |                            |      |       |  |  |

| E1     | Drive voltage (DIS_N = "H")               | V <sub>ON_DIS</sub>  | 1           | $V_{ON\_DIS} = V_{DIS\_N} - V_{PACK}$<br>VGS connect 4.7MΩ            | 8                          |                   | 13                         | V    | *6    |  |  |

| E2     | Drive voltage (CHG_N = "H")               | V <sub>ON_CHG</sub>  | 1           | $V_{ON\_CHG} = V_{CHG\_N} - V_{BAT}$<br>VGS connect 4.7MΩ             | 8                          | _                 | 13                         | V    | *6    |  |  |

| E3     | Drive voltage (DIS_N = "L")               | V <sub>OFF_DIS</sub> | 1           | $V_{OFF_{DIS}} = V_{DIS_{N}} - V_{PACK}$<br>VGS connect 4.7M $\Omega$ | _                          |                   | 0.2                        | V    | _     |  |  |

| E4     | Drive voltage (CHG_N = "L")               | V <sub>OFF_CHG</sub> | 1           | $V_{OFF\_CHG} = V_{CHG\_N} - V_{BAT}$<br>VGS connect 4.7M $\Omega$    | _                          | _                 | 0.2                        | V    | _     |  |  |

| E5     | Rise time (DIS_N = "L" to "H")            | tr                   | 1           | $V_{DIS} = 10\%$ to 90%<br>$C_L = 68nF$                               | _                          | 1                 | 2                          | ms   | _     |  |  |

| E6     | Rise time (CHG_N = "L" to<br>"H")         | tr                   | 1           | $V_{CHG} = 10\%$ to 90%<br>$C_L = 68nF$                               |                            | 1                 | 2                          | ms   | _     |  |  |

| E7     | Fall time (DIS_N = "H" to "L")            | tf                   | 1           | $V_{DIS} = 90\%$ to 10%<br>$C_L = 68nF$                               |                            | 1                 | 2                          | ms   | _     |  |  |

| E8     | Fall time (CHG_N = "H" to "L")            | tf                   | 1           | $V_{CHG} = 90\%$ to 10%<br>$C_L = 68nF$                               |                            | 1                 | 2                          | ms   | _     |  |  |

Note) \*6: The voltage can be changed by FET\_V register setting. (see page 34)

### Electrical Characteristics at $V_{BAT} = V_{PACK} = 12.5 \text{ V}$ to 45 V (reference value for design) Note) Ta= -40°C to 105°C, unless otherwise specified.

Note) These characteristics are reference values for design, and all ICs have not been guaranteed through inspections. If, by any chance, the problem caused by these characteristics occurs, we will respond in good faith to user concerns.

| В      | Deremeter                                 | Symbol               | Test    | Conditions                                                                                                                                | Refe                       | rence va          | alues                      | Unit | Nata  |

|--------|-------------------------------------------|----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|----------------------------|------|-------|

| No.    | Parameter                                 | Symbol               | Circuit | Conditions                                                                                                                                | Min                        | Тур               | Max                        | Unit | Notes |

| Cell I | Balancing Control Output                  |                      |         |                                                                                                                                           |                            |                   |                            |      |       |

| G1     | Output voltage (High)                     | $V_{CB1}$            |         |                                                                                                                                           | VC <sub>n</sub><br>- 0.2   | VC <sub>n</sub>   | VC <sub>n</sub><br>+ 0.2   | V    | _     |

| G2     | Output voltage (Low)                      | V <sub>CB2</sub>     |         |                                                                                                                                           | VC <sub>n-1</sub><br>- 0.2 | VC <sub>n-1</sub> | VC <sub>n-1</sub><br>+ 0.2 | V    | _     |

| G3     | Discharge Switch-On Resistance<br>(CB1-9) | R <sub>CB1</sub>     |         | $\Delta VC_n \gamma 3V$                                                                                                                   | _                          | 5                 | 6.5                        | kΩ   | _     |

| G4     | Discharge Switch-On Resistance<br>(CB10)  | R <sub>CB2</sub>     |         | $\Delta VC_n \gamma 3V$                                                                                                                   | _                          | 12.5              | 16.3                       | kΩ   | _     |

| N-ch   | annel FET Drive                           |                      |         |                                                                                                                                           |                            |                   |                            |      |       |

| E1     | Drive voltage (DIS_N = "H")               | V <sub>ON_DIS</sub>  |         | $\begin{split} & V_{ON\_DIS} = V_{DIS\_N} - V_{PACK} \\ & VGS \ connect \ 4.7 M\Omega \\ & V_{BAT} = V_{PACK} \ \geqq \ 15 V \end{split}$ | 8                          |                   | 13                         | V    | *6    |

| E2     | Drive voltage (CHG_N = "H")               | V <sub>ON_CHG</sub>  |         | $\begin{split} & V_{ON\_CHG} = V_{CHG\_N} - V_{BAT} \\ & VGS \ connect \ 4.7 M\Omega \\ & V_{BAT} = V_{PACK} \geqq \ 15 V \end{split}$    | 8                          | _                 | 13                         | V    | *6    |

| E9     | Drive voltage (DIS_N = "H")               | V <sub>ON_DIS</sub>  |         | $\begin{split} & V_{ON\_DIS} = V_{DIS\_N} - V_{PACK} \\ & VGS \ connect \ 4.7M\Omega \\ & V_{BAT} = V_{PACK} \geqq 12.5V \end{split}$     | 7                          |                   | 13                         | V    | *6    |

| E10    | Drive voltage (CHG_N = "H")               | V <sub>ON_CHG</sub>  |         | $\begin{split} V_{ON\_CHG} &= V_{CHG\_N} - V_{BAT} \\ VGS \text{ connect } 4.7M\Omega \\ V_{BAT} &= V_{PACK} \geqq 12.5V \end{split}$     | 7                          |                   | 13                         | V    | *6    |

| E3     | Drive voltage (DIS_N = "L")               | V <sub>OFF_DIS</sub> |         | $\label{eq:V_OFF_DIS} \begin{split} V_{OFF\_DIS} &= V_{DIS\_N} - V_{PACK} \\ VGS \ connect \ 4.7 M\Omega \end{split}$                     | _                          |                   | 0.2                        | V    |       |

| E4     | Drive voltage (CHG_N = "L")               | V <sub>OFF_CHG</sub> |         | $V_{OFF\_CHG} = V_{CHG\_N} - V_{BAT}$<br>VGS connect 4.7MΩ                                                                                |                            |                   | 0.2                        | V    | _     |

| E5     | Rise time (DIS_N = "L" to "H")            | tr                   |         | $V_{DIS} = 10\%$ to 90%<br>$C_L = 68nF$                                                                                                   | _                          | 1                 | 2                          | ms   | _     |

| E6     | Rise time (CHG_N = "L" to<br>"H")         | tr                   |         | $V_{CHG} = 10\%$ to 90%<br>$C_L = 68nF$                                                                                                   |                            | 1                 | 2                          | ms   |       |

| E7     | Fall time (DIS_N = "H" to "L")            | tf                   |         | $V_{DIS} = 90\%$ to 10%<br>$C_L = 68nF$                                                                                                   |                            | 1                 | 2                          | ms   |       |

| E8     | Fall time (CHG_N = "H" to "L")            | tf                   | _       | $V_{CHG} = 90\%$ to 10%<br>$C_L = 68nF$                                                                                                   | _                          | 1                 | 2                          | ms   | _     |

Note) \*6: The voltage can be changed by FET\_V register setting. (see page 34)

# Electrical Characteristics at $V_{BAT} = V_{PACK} = 37 \text{ V}$ (continued) Note) $T_a = 25^{\circ}C \pm 3^{\circ}C$ , unless otherwise specified.

| В       | Parameter                     | Symbol              | Test     |                          |                            | Limits |                                                           |      | Natas    |

|---------|-------------------------------|---------------------|----------|--------------------------|----------------------------|--------|-----------------------------------------------------------|------|----------|

| No.     |                               |                     | Circuit  | Conditions               | Min                        | Тур    | Max                                                       | Unit | Notes    |

| Digital | Input (1) (VPC)               |                     |          |                          |                            |        |                                                           |      |          |

| F1      | High-level input voltage      | V <sub>IH</sub>     | 1        |                          | 4.0                        |        | _                                                         | v    | _        |

| F2      | Low-level input voltage       | V <sub>IL</sub>     | 1        |                          | _                          | _      | 0.3                                                       | V    | -        |

| F3      | Pull-down resistance          | R <sub>IL</sub>     | 1        |                          | 2.5                        | 7      | 20                                                        | MΩ   | _        |

| Digital | I Input (2) (FETINT)          |                     |          |                          |                            |        |                                                           |      |          |

| F4      | High-level input voltage      | V <sub>IH</sub>     | 1        | _                        | 3                          |        | _                                                         | V    | _        |

| F5      | Low-level input voltage       | V <sub>IL</sub>     | 1        | _                        |                            |        | 0.1                                                       | V    | _        |

| Digital | Input (3) (SHDN)              |                     |          |                          |                            |        |                                                           |      |          |

| F6      | High-level input voltage      | V <sub>IH</sub>     | 1        | _                        | 3                          | _      | _                                                         | V    | —        |

| F7      | Low-level input voltage       | V <sub>IL</sub>     | 1        |                          | _                          |        | 0.1                                                       | V    | _        |

| F8      | Pull-down resistance          | R <sub>IL</sub>     | 1        |                          | 300                        | 820    | 2300                                                      | kΩ   | -        |

| Digital | l Input (4) (SDI_M, SCLK_M, S |                     |          |                          |                            |        | 1                                                         | I    |          |

| F9      | High-level input voltage      | V <sub>IH</sub>     | 1        | _                        | $0.8 \times V_{CVDD}$      |        | V <sub>CVDD</sub>                                         | v    |          |

| F10     | Low-level input voltage       | V <sub>IL</sub>     | 1        |                          | 0                          |        | $\begin{array}{c} 0.2 \times \\ V_{CVDD} \end{array}$     | V    |          |

| F11     | Input leakage current         | I <sub>LK</sub>     | 1        | _                        | -1                         | 0      | 1                                                         | μΑ   | _        |

| Digital | Input (5) (STB_M)             |                     |          |                          |                            |        |                                                           |      |          |

| F12     | High-level input voltage      | V <sub>IH</sub>     | 1        |                          | $0.8 \times V_{CVDD}$      |        | V <sub>CVDD</sub>                                         | V    | _        |

| F13     | Low-level input voltage       | V <sub>IL</sub>     | 1        |                          | 0                          |        | $\begin{array}{c} 0.2 \times \\ V_{\rm CVDD} \end{array}$ | V    |          |

| F14     | Pull-up resistance            | R <sub>IL</sub>     | 1        | _                        | 50                         | 100    | 200                                                       | kΩ   | _        |

| Digital | Output (1) (NAULT_M, SDO      | _M, ALARN           | /I_M) *7 |                          |                            |        |                                                           |      |          |

| F15     | High-level output voltage     | V <sub>OH</sub>     | 1        | $I_{OH} = -1 \text{ mA}$ | V <sub>CVDD</sub><br>- 0.6 |        | V <sub>CVDD</sub><br>+0.3                                 | V    |          |

| F16     | Low-level output voltage      | V <sub>OL</sub>     | 1        | $I_{OL} = +1 \text{ mA}$ | - 0.3                      |        | 0.4                                                       | V    | —        |

| Digital | Output (2) (NRST_M)           |                     |          |                          |                            |        |                                                           |      |          |

| F17     | Low-level output voltage      | I <sub>OL</sub>     | 1        | $I_{OL} = 0 \text{ mA}$  | 0                          |        | 0.5                                                       | V    | *8       |

| F18     | Pull-up resistance            | R <sub>IL</sub>     | 1        | _                        | 50                         | 100    | 200                                                       | kΩ   | -        |

| CVDD    | POR (POWER-ON RESET)          |                     | 1        |                          |                            |        |                                                           |      |          |

| F19     | Positive-going input voltage  | V <sub>IH_POR</sub> | 1        |                          | 2.7                        | 2.95   |                                                           | V    |          |

| F20     | Negative-going input voltage  | V <sub>IL_POR</sub> | 1        | _                        | 2.2                        | 2.45   |                                                           | V    | <u> </u> |

Notes) \*7: In shutdown mode, each digital pin is set to Hi-Z, and connected to pull-down resistor of 100 kΩ (typ) simultaneously.

\*8: Output voltage is divided by the pull-down resistor (10 k $\Omega$ ) connected to GND and the pull-up resister (100 k $\Omega$ , F18) connected to CVDD.

#### Electrical Characteristics at $V_{BAT} = V_{PACK} = 12.5$ V to 45 V (reference value for design) Note) Ta= -40°C to 105°C, unless otherwise specified.

Note) These characteristics are reference values for design, and all ICs have not been guaranteed through inspections. If, by any chance, the problem caused by these characteristics occurs, we will respond in good faith to user concerns.

| В                        | Parameter                     | Symbol              | Test<br>Circuit | Conditions               | Refe                                                      | Unit | Notes                                                   |      |       |

|--------------------------|-------------------------------|---------------------|-----------------|--------------------------|-----------------------------------------------------------|------|---------------------------------------------------------|------|-------|

| No.                      |                               |                     |                 | Conditions               | Min                                                       | Тур  | Max                                                     | Unit | Notes |

| Digital                  | I Input (1) (VPC)             |                     |                 |                          |                                                           |      |                                                         |      |       |

| F1                       | High-level input voltage      | V <sub>IH</sub>     | _               |                          | 4.0                                                       |      | _                                                       | v    | _     |

| F2                       | Low-level input voltage       | V <sub>IL</sub>     | _               |                          |                                                           |      | 0.3                                                     | v    | _     |

| F3                       | Pull-down resistance          | R <sub>IL</sub>     | _               |                          | 2.5                                                       | 7    | 20                                                      | MΩ   | _     |

| Digital                  | l Input (2) (FETINT)          |                     |                 |                          |                                                           |      |                                                         |      |       |

| F4                       | High-level input voltage      | V <sub>IH</sub>     |                 |                          | 3                                                         |      | _                                                       | v    | _     |

| F5                       | Low-level input voltage       | V <sub>IL</sub>     | _               | _                        |                                                           |      | 0.1                                                     | v    | _     |

| Digital Input (3) (SHDN) |                               |                     |                 |                          |                                                           |      |                                                         |      |       |

| F6                       | High-level input voltage      | V <sub>IH</sub>     |                 |                          | 3                                                         |      | _                                                       | V    | _     |

| F7                       | Low-level input voltage       | V <sub>IL</sub>     | _               |                          |                                                           |      | 0.1                                                     | V    | _     |

| F8                       | Pull-down resistance          | R <sub>IL</sub>     | _               |                          | 300                                                       | 820  | 2300                                                    | kΩ   | _     |

| Digital                  | I Input (4) (SDI_M, SCLK_M, S | SEN_M) *7           |                 |                          |                                                           |      |                                                         |      |       |

| F9                       | High-level input voltage      | V <sub>IH</sub>     |                 | _                        | $0.8 \times V_{CVDD}$                                     |      | V <sub>CVDD</sub>                                       | v    |       |

| F10                      | Low-level input voltage       | V <sub>IL</sub>     |                 | _                        | 0                                                         |      | $\begin{array}{c c} 0.2 \times \\ V_{CVDD} \end{array}$ | v    | _     |

| F11                      | Input leakage current         | I <sub>LK</sub>     | _               | _                        | -1                                                        | 0    | 1                                                       | μΑ   | _     |

| Digital                  | I Input (5) (STB_M)           |                     |                 |                          |                                                           |      |                                                         |      |       |

| F12                      | High-level input voltage      | $V_{\rm IH}$        | _               | _                        | $\begin{array}{c} 0.8 \times \\ V_{\rm CVDD} \end{array}$ |      | V <sub>CVDD</sub>                                       | v    | _     |

| F13                      | Low-level input voltage       | V <sub>IL</sub>     | _               |                          | 0                                                         |      | $egin{array}{c} 0.2 \times \\ V_{CVDD} \end{array}$     | v    | _     |

| F14                      | Pull-up resistance            | R <sub>IL</sub>     | _               |                          | 50                                                        | 100  | 200                                                     | kΩ   | _     |

| Digital                  | Output (1) (NAULT_M, SDO      | M, ALARN            | <b>∕I_M)</b> *7 | 1                        |                                                           |      |                                                         |      |       |

| F15                      | High-level output voltage     | V <sub>OH</sub>     | _               | $I_{OH} = -1 \text{ mA}$ | $\begin{array}{c} V_{CVDD} \\ -  0.6 \end{array}$         | —    | V <sub>CVDD</sub><br>+0.3                               | v    | _     |

| F16                      | Low-level output voltage      | V <sub>OL</sub>     | _               | $I_{OL} = +1 \text{ mA}$ | - 0.3                                                     |      | 0.4                                                     | V    | _     |

| Digital                  | Output (2) (NRST_M)           |                     |                 |                          |                                                           |      |                                                         |      |       |

| F17                      | Low-level output voltage      | I <sub>OL</sub>     | _               | $I_{OL} = 0 \text{ mA}$  | 0                                                         |      | 0.5                                                     | v    | *8    |

| F18                      | Pull-up resistance            | R <sub>IL</sub>     |                 |                          | 50                                                        | 100  | 200                                                     | kΩ   | _     |

| CVDD                     | POR (POWER-ON RESET)          |                     |                 |                          | · · ·                                                     |      | •                                                       |      |       |

| F19                      | Positive-going input voltage  | V <sub>IH_POR</sub> | _               |                          | 2.7                                                       | 2.95 | _                                                       | v    | _     |

| F20                      | Negative-going input voltage  | V <sub>IL_POR</sub> | _               | _                        | 2.2                                                       | 2.45 | _                                                       | V    | _     |

Notes) \*7: In shutdown mode, each digital pin is set to Hi-Z, and connected to pull-down resistor of 100 kΩ (typ) simultaneously.

\*8: Output voltage is divided by the pull-down resistor (10 k $\Omega$ ) connected to GND and the pull-up resister (100 k $\Omega$ , F18) connected to CVDD.

# Electrical Characteristics at $V_{BAT} = V_{PACK} = 37 \text{ V}$ (continued) Note) $T_a = 25^{\circ}C \pm 3^{\circ}C$ , unless otherwise specified.

| в     | Parameter                          | Symphol              | Test        | Que d'élana                                          | Limits |     |     | 1.1  |       |

|-------|------------------------------------|----------------------|-------------|------------------------------------------------------|--------|-----|-----|------|-------|

| No.   | Parameter                          | Symbol               | Circui<br>t | Conditions                                           | Min    | Тур | Max | Unit | Notes |

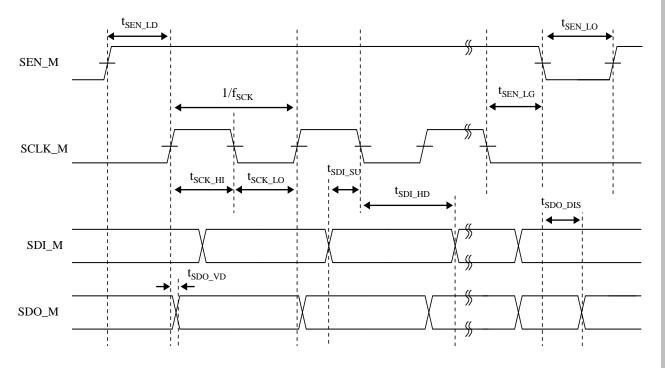

| Micro | Microcomputer SPI Data Interface   |                      |             |                                                      |        |     |     |      |       |

| I1    | SCLK_M frequency                   | f <sub>SCK</sub>     | 1           |                                                      | _      |     | 500 | kHz  |       |

| I2    | SCLK_M duty cycle                  | t <sub>DUTY</sub>    | 1           |                                                      | 45     | 50  | 55  | %    |       |

| 13    | SEN_M rising<br>to SCLK_M rising   | t <sub>SEN_LD</sub>  | 1           | _                                                    | 100    |     |     | ns   |       |

| I4    | SCLK_M falling<br>to SEN_M falling | t <sub>SEN_LG</sub>  | 1           |                                                      | 100    | _   | _   | ns   | _     |

| 15    | SEN_M "Low" width                  | t <sub>SEN_LO</sub>  | 1           |                                                      | 500    |     |     | ns   |       |

| I6    | SDI_M setup time                   | t <sub>SDI_SU</sub>  | 1           | SDI_M valid to SCLK_M falling                        | 100    |     |     | ns   |       |

| I7    | SDI_M hold time                    | t <sub>SDI_HD</sub>  | 1           | SCLK_M falling to SDI_M valid                        | 100    |     |     | ns   |       |

| 18    | SDO_M valid time                   | t <sub>SDO_VD</sub>  | 1           | SCLK_M rising to SDO_M valid $C_L \le 50 \text{ pF}$ |        |     | 400 | ns   | _     |

| 19    | SDO_M disable time                 | t <sub>SDO_DIS</sub> | 1           | SEN_M falling to SDO_M disable                       |        |     | 400 | ns   |       |

| I10   | WDT                                | t <sub>WDT</sub>     | 1           | default = 22 min. (typ)                              | -10    | 0   | 10  | %    |       |

SPI Timing Diagram

# Electrical Characteristics at $V_{BAT} = V_{PACK} = 12.5 \text{ V}$ to 45 V (reference value for design) (continued)

Note) Ta= -40°C to 105°C, unless otherwise specified.

Note) These characteristics are reference values for design, and all ICs have not been guaranteed through inspections. If, by any chance, the problem caused by these characteristics occurs, we will respond in good faith to user concerns.

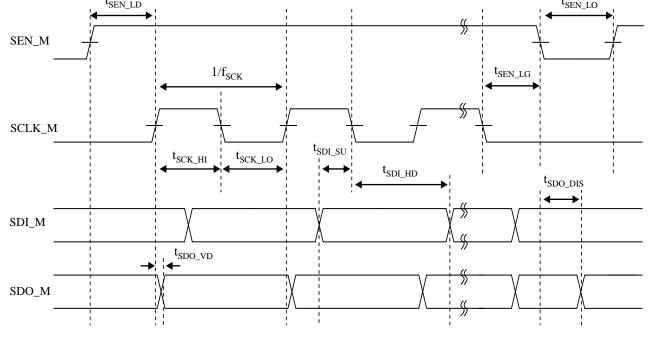

| В     | Parameter                          | Symbol               | Test<br>Circuit |                                                      | Reference values |     |     |      |                  |  |

|-------|------------------------------------|----------------------|-----------------|------------------------------------------------------|------------------|-----|-----|------|------------------|--|

| No.   |                                    |                      |                 | Conditions                                           | Min              | Тур | Max | Unit | Notes            |  |

| Micro | Microcomputer SPI Data Interface   |                      |                 |                                                      |                  |     |     |      |                  |  |

| I1    | SCLK_M frequency                   | f <sub>SCK</sub>     | _               |                                                      |                  |     | 500 | kHz  |                  |  |

| I2    | SCLK_M duty cycle                  | t <sub>DUTY</sub>    | _               |                                                      | 45               | 50  | 55  | %    |                  |  |

| I3    | SEN_M rising<br>to SCLK_M rising   | t <sub>SEN_LD</sub>  |                 | _                                                    | 100              | _   | _   | ns   | _                |  |

| I4    | SCLK_M falling<br>to SEN_M falling | t <sub>SEN_LG</sub>  |                 | _                                                    | 100              |     | _   | ns   | _                |  |

| I5    | SEN_M "Low" width                  | t <sub>SEN_LO</sub>  |                 | _                                                    | 500              | _   | —   | ns   |                  |  |

| I6    | SDI_M setup time                   | t <sub>SDI_SU</sub>  |                 | SDI_M valid to SCLK_M falling                        | 100              | _   | _   | ns   | _                |  |

| I7    | SDI_M hold time                    | t <sub>SDI_HD</sub>  |                 | SCLK_M falling to SDI_M valid                        | 100              | _   | _   | ns   | _                |  |

| 18    | SDO_M valid time                   | t <sub>SDO_VD</sub>  |                 | SCLK_M rising to SDO_M valid $C_L \le 50 \text{ pF}$ |                  |     | 400 | ns   | _                |  |

| I9    | SDO_M disable time                 | t <sub>SDO_DIS</sub> |                 | SEN_M falling to SDO_M disable                       |                  |     | 400 | ns   | _                |  |

| I10   | WDT                                | t <sub>WDT</sub>     |                 | default = 22 min. (typ)                              | -10              | 0   | 10  | %    |                  |  |

|       | t <sub>SEN_LD</sub>                |                      |                 |                                                      | "                | ((  |     |      | <sup>1</sup> _LO |  |

SPI Timing Diagram

## nuvoTon

KA49511A

Test Circuit Diagram

Test Circuit Diagram

#### Usage Notes

- Special Attention and Precaution in Using the IC

- 1. This IC might smoke or ignite if it is mounted in the wrong direction onto the PCB (printed circuit board). Pay attention to the direction of it.

- 2. Pay attention to the pattern layout of PCB in order to prevent damage due to pin-to-pin short. For pin configuration, see the Pin Descriptions.

- Conduct a visual inspection on PCBs sufficiently prior to supplying power to the IC, to prevent damage due to pinto-pin solder-bridge. Also, conduct a technical verification to the mounting quality sufficiently, to prevent damage due to adhering conductive foreign substance such as solder scrap during transportation.

- 4. Since this IC might be damaged or occasionally smoke if abnormal state occurs, such as output-VCC short (power supply fault), output-GND short (ground fault), output-to-output short (load short), or pin-to-pin leakage, care must be taken in the use of the IC. Safety measures, such as fuse installation, are recommended in order to avoid such risks.

- 5. When designing your equipment, comply with the range of absolute maximum ratings and the guaranteed operating conditions (operating power supply voltage and environment, etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off, and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the IC is used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire, or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the IC.

- Notes for Power IC

- The protection circuit is built in to ensure the safety in abnormal operation. Therefore, when designing your equipment, be careful the protection circuit should not work in normal operation. Especially for thermal protection circuit, the IC might be damaged before it works, in case the temperature of IC exceeds the ASO (Area of Safe Operation) or absolute maximum rating in an instant by short circuit, such as Output-VM (Power Supply Fault) or Output-GND (Ground Fault).

- 2. Verify risks caused by the malfunction of external components.

### **Revision History**

| Date      | Revision | Description                                |

|-----------|----------|--------------------------------------------|

| 2021.1.28 | 1.00     | 1. initially issued.                       |

| 2022 1 26 | 1.02     | 1. Added important notice on page2         |

| 2022.1.26 | 1.02     | 2. Changed the description of usage notes. |