0.6um CDMOS / UHV Process

0.6 um CDMOS- / UHV-Verfahren

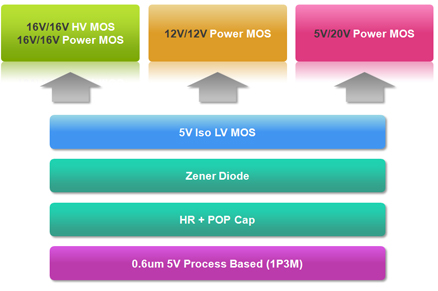

0.6 um 5-Volt-/40-Volt-Dual-Vgs-CDMOS-Verfahren

Bei diesem Verfahren handelt sich um ein a Dual GOX-Verfahren mit Vgs = 5 Volt und maximalem Vgs = 40 Volt, Vds-Spannungen von 5 V/18 V/25 V/40 V, das Geräte mit niedrigem on-Widerstand für Stromwandlungs- und LED-Bedarf sowie hochohmige Poly2-, PIP-Kondensatoren und Bipolargeräte zur Implementierung von analogen Designs verfügbar macht. Es sind auch weitere Spezialgeräte für speziellen Bedarf verfügbar, einschließlich Verarmungsgeräte, Nativgeräte, Zenerdioden usw. Es gibt auch ein Poly e-Fuse-IP für Produkte, die OTP erfordern. Dieses Verfahren unterstützt 3 um Obermetall, um Kupferdrahtbonden zu ermöglichen. Zur Nutzung eines digitalen Schaltkreisdesigns gibt es eine 5-Volt-Standardzellenbibliothek.

| Device | Vth(V) | Idsat(uA / um) | Rds,on(mohm-mm2) | Bvdss(V) |

|---|---|---|---|---|

| 5V / 18V LDNMOS | 0.85 | 330 | 18 | >25 |

| 5V / 25V LDNMOS | 0.77 | 380 | 25 | >30 |

| 5V / 40V LDNMOS | 0.77 | 340 | 55 | >48 |

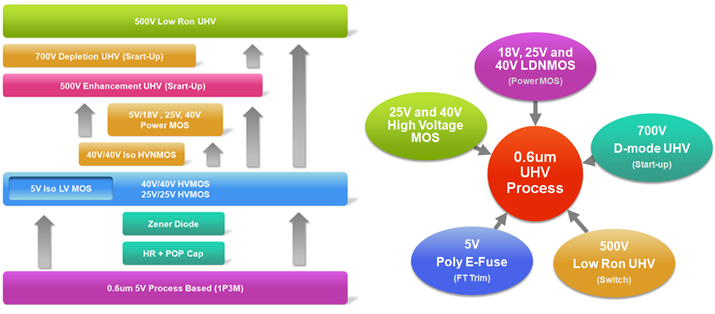

0.6 um 5-Volt-/40-Volt-/UHV-Verfahren

Dieses einzigartige Verfahren bedient sich der Modularverarbeitungstechnologie von Nuvoton, die auf 0.6 um 5-Volt-/40-Volt-Dual-Vgs-CDMOS-Verfahren basiert. Neben den Geräten, die im 0.6 um 5-Volt-/40-Volt-Dual-Vgs-CDMOS-Verfahren eingesetzt werden, gibt es Zusatzgeräte in diesem einzigartige Verfahren, einschließlich 700-Volt-Ultrahochspannungsgeräte, wie z. B. Verarmungs-UHV, UHV mit niedrigem Ron und UHV JFET, zur Unterstützung von Anwendungen in den Bereichen von allgemeinen DC/DC- bis hin zu AC/DC-Stromanlagen. Da es sich hier um ein vollständig modularisiertes und angepasstes Fertigungsverfahren handelt, können beliebige Geräte zur Realisierung von speziellen Anwendungsbedürfnissen gewählt werden. Mit Hilfe dieser Verarbeitungsplattform sind Kunden in der Lage, einen breiten Bereich des Marktbedarfs mit einem einzigen, anpassbaren Verfahren zu bedienen.

0.6 um 5-Volt-/20-Volt-CDMOS-Verfahren

Für die nachstehend dargestellten 20-Volt-Verfahren bietet Nuvoton eine andere Option des 0.6 um 5-Volt-/20-Volt-CDMOS-Verfahrens. Bei diesem Verfahren handelt sich um ein a Dual GOX-Verfahren mit Vgs = 5 Volt und maximalem Vgs = 16 Volt, Vds-Spannungen = 5 V/12 V/16 V/20 V, das Geräte mit niedrigem on-Widerstand für Stromwandlungs- und LED-Bedarf sowie hochohmige Poly2-, PIP-Kondensatoren und Bipolargeräte für analoge Designs verfügbar macht. Weitere Spezialgeräte sind zusätzlich zur Deckung von speziellen Bedürfnissen vorhanden, z. B. als Verarmungsgeräte mit Zenerdioden. Zudem ist das Poly e-Fuse-IP von Nuvoton zur Erfüllung von OTP-Anforderungen vorhanden. Dieses Verfahren unterstützt auch 3 um Obermetall für Kupferdrahtbonden. Zur Nutzung eines digitalen Schaltkreisdesigns gibt es eine 5-Volt-Standardzellenbibliothek.

| Device | Vth(V) | Idsat(uA / um) | Rds,on(mohm-mm2) | Bvdss(V) |

|---|---|---|---|---|

| 12V / 12V LDNMOS | 1.9 | 550 | 7.8 | >18 |

| 16V / 16V LDNMOS | 1.9 | 760 | 12 | >20 |

| 5V / 20V LDNMOS | 1.1 | 365 | 25 | >24 |