ISD2360 Design Guide

# ISD ChipCorder ISD2360 Design Guide

Publication Release Date: Aug 3, 2016 Revision V1.15

### ISD2360 Design Guide

© 2012 by Nuvoton Technology Corporation.

All trademarks and registered trademarks of products and companies mentioned in this document belong to their respective owners.

The information contained in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton provides this document for reference purposes only in the design of ISD ChipCorder<sup>®</sup> microcontroller-based systems. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information, please contact: Nuvoton Technology Corporation at <u>www.nuvoton.com</u>.

#### **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Furthermore, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result in or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

### Table of Contents-

| LIST OF TABLES                                                                       | VII |

|--------------------------------------------------------------------------------------|-----|

| 1. GENERAL DESCRIPTION                                                               | 1   |

| Overview                                                                             | 1   |

| Overview<br>Features                                                                 |     |

|                                                                                      |     |

| 2. PIN CONFIGURATIONS                                                                | 3   |

| 2.1 PIN DIAGRAMS                                                                     |     |

| 2.2 PIN DESCRIPTIONS                                                                 | 4   |

| 3. BLOCK DIAGRAM                                                                     | 7   |

| 4. DEVICE STATUS                                                                     | 8   |

| 4.1 Device Status Register                                                           | 0   |

| 4.1 Device Status Register                                                           | -   |

|                                                                                      |     |

| 5. DEVICE CONFIGURATION                                                              | 10  |

| 5.1 DEVICE ID                                                                        | -   |

| 5.2 CLOCK CONFIGURATION                                                              |     |

| 5.3 GPIO CONFIGURATION                                                               |     |

| 5.3.1 GPIO Pin Function Definition                                                   |     |

| 5.3.2 Special 3 V Registers                                                          |     |

| 5.3.3 GPIO Pin Structure                                                             |     |

| <ul> <li>5.4 SIGNAL PATH CONFIGURATION</li> <li>5.5 DEVICE CHECKSUM</li> </ul>       |     |

| 5.5 DEVICE CHECKSOM                                                                  |     |

| 5.7 GPIO4 CONFIGURATION FOR DIGITAL READ/WRITE                                       |     |

| 5.8 Fast De-Bounce for GPIO Trigger                                                  |     |

| 5.9 Thermal Shutdown                                                                 |     |

| 6. OPERATIONAL DESCRIPTION                                                           |     |

|                                                                                      |     |

| 6.1 OVERVIEW                                                                         |     |

| 6.2 AUDIO STORAGE                                                                    |     |

| 6.3 SAMPLE RATES     6.4 AUDIO COMPRESSION AND DE-COMPRESSION                        | -   |

| 6.5 System Voice Macro Flow Chart                                                    |     |

| 6.6 GPIO TRIGGER                                                                     |     |

| 6.6.1 GPIO Trigger Basics                                                            |     |

| 6.6.2 SPI or GPIO Trigger                                                            |     |

| 6.6.2.1 Pulling SSB low automatically claims the SPI interface                       |     |

| 6.6.2.2 Pulling SSB Low does not affect the triggering capability                    |     |

| 6.6.2.3 GPIO Trigger Execution is preemptive                                         |     |

| 6.6.2.4 SPI vs. GPIO Triggering Reliability<br>6.6.3 Volume Control via GPIO Trigger |     |

| 6.7 MULTI-CHANNEL FEATURE                                                            |     |

| 6.7.1 SPI Multi Channel                                                              |     |

| 6.7.2 Multi Channel GPIO Trigger                                                     |     |

| 6.8 VM JUMP AND CHANNEL COUNTER COMMANDS                                             |     |

| 6.8.1 VM Branch Commands                                                             |     |

| 6.8.2 Channel Counter Command                                                        |     |

| 7. MEMORY MANAGEMENT                                                                 | 23  |

| 7.1 MEMORY HEADER                                                                    |     |

|                                                                                      |     |

| 7.1.    |                                                                        |    |

|---------|------------------------------------------------------------------------|----|

| 7.1.2   | 2 Memory Protection                                                    | 25 |

| 7.2     | VOICE PROMPT                                                           |    |

| 7.3     | VOICE MACRO                                                            | 26 |

| 7.3.    |                                                                        | -  |

| 7.3.2   |                                                                        |    |

|         |                                                                        |    |

| 7.3.3   |                                                                        |    |

|         | 3.3.1 Sample_1: A Simple Trigger-To-Play Project                       |    |

|         | 3.3.2 Sample_2: Channel Mixing with Volume Control                     |    |

|         | 3.3.3 Sample_3: Driving GPIO Using the Channel Counter                 |    |

| 7.4     | USER DATA                                                              | 34 |

| 8. SER  | IAL PERIPHERAL INTERFACE                                               |    |

| 8.1     | SPI FEATURES                                                           | 35 |

|         | SPI COMMANDS                                                           |    |

|         | SPI COMMAND VS. STATUS                                                 |    |

|         |                                                                        |    |

|         | SPI COMMAND DESCRIPTIONS                                               |    |

| 8.4.    |                                                                        |    |

|         | 4.1.1 PLAY_VP – Play Voice Prompt                                      |    |

|         | 1.1.2 PLAY_VP@Rn – Play Voice Prompt @ Rn                              |    |

| 8.4     | 1.1.3 PLAY_VP_LP – Play Voice Prompt Loop                              |    |

| 8.4     | 1.1.4 PLAY_VP@Rn_LP – Loop Play Voice Prompt Referenced by RnCnt Times |    |

| 8.4     | 1.1.5 EXE_VM – Execute Voice Macro                                     |    |

| 8.4     | 4.1.6 EXE_VM@Rn – Execute Voice Macro Referenced by Rn                 |    |

| 8.4     | 4.1.7 PLAY_SIL – Play Silence                                          |    |

| 8.4     | 4.1.8 STOP – Stop the Play Operations                                  |    |

| 8.4     | 4.1.9 STOP_LP – Stop Loop Play Operations                              |    |

| 8.4     | 4.1.10 SPI_PCM_READ – SPI Read De-Compressed PCM Data from Memory      |    |

| 8.4     | 4.1.11 SPI_SND_DEC – SPI Send Compressed Data for Decoding             |    |

| 8.4.2   | 2 Device Status Commands                                               |    |

| - 8.4   | A.2.1 READ_STATUS – Read Status                                        |    |

|         | 1.2.2 READ_INT – Read Interrupt                                        |    |

|         | 4.2.3 READ_ID - Read Device ID                                         |    |

| 8.4.    |                                                                        |    |

|         | 1.3.1 DIG_READ – Digital Read                                          |    |

|         | 4.3.2 DIG_WRITE – Digital Write                                        |    |

|         | 1.3.3 ERASE_MEM – Sector Erase Memory                                  |    |

|         | 1.3.4 CHIP_ERASE – Erase Entire Memory                                 |    |

|         |                                                                        |    |

|         |                                                                        |    |

| 8.4.4   |                                                                        |    |

|         | 4.4.1 PWR_UP – Power Up Device                                         |    |

|         | 4.4.2 PWR_DN – Power Down Device                                       |    |

|         | 4.4.3 SET_CLK_CFG – Set Clock Configuration Register                   |    |

|         | 4.4.4 RD_CLK_CFG – Read Clock Configuration Register                   |    |

| 8.4     | 4.4.5 WR_CFG_REG – Write Configuration Register                        |    |

|         | 4.4.6 RD_CFG_REG – Read Configuration Register                         |    |

| 8.4     | 1.4.7 RESET – Reset Device                                             |    |

| 9. REG  | SISTER OPERATIONS                                                      |    |

| 10. APF | LICATION DIAGRAMS                                                      |    |

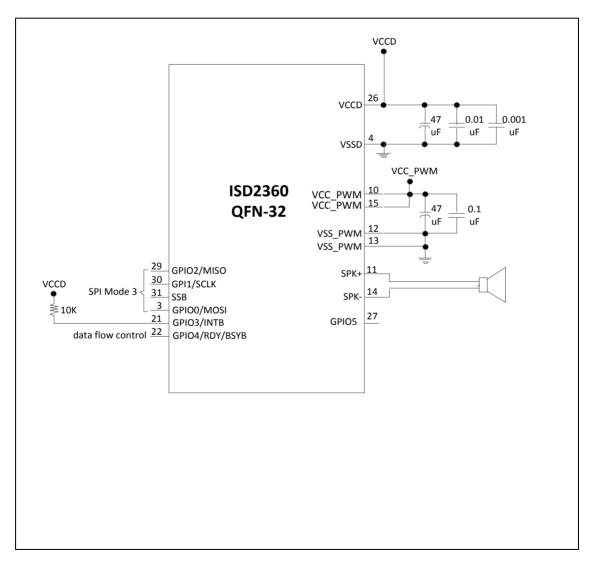

| 10.1    | SPI APPLICATION UNDER MCU CONTROL                                      | 57 |

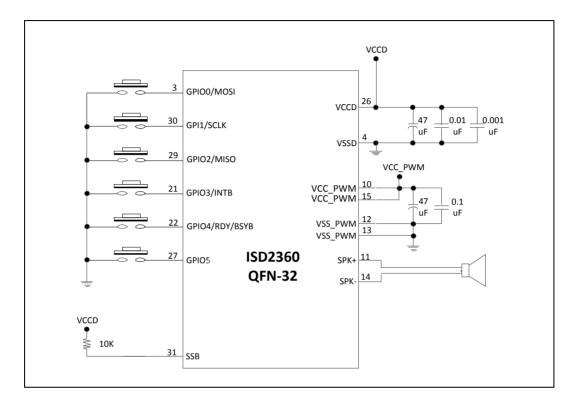

|         | GPIO TRIGGER STANDALONE APPLICATION                                    |    |

|         |                                                                        |    |

| 11. ELE | CTRICAL CHARACTERISTICS                                                | 59 |

| 11.1    | ABSOLUTE MAXIMUM RATINGS                                               | 59 |

|         | OPERATING CONDITIONS                                                   |    |

|         | AC PARAMATERS                                                          |    |

| 11.0    |                                                                        |    |

## nuvoTon

|     |        | Internal Oscillator |    |

|-----|--------|---------------------|----|

|     | 11.3.2 | Speaker Outputs     |    |

|     |        | DC Parameters       |    |

|     | 11.3.4 | SPI Timing          | 61 |

|     |        |                     |    |

| 12. | PACKA  | AGE DIMENSIONS      | 62 |

|     | -      | AGE DIMENSIONS      | _  |

### List of Figures-

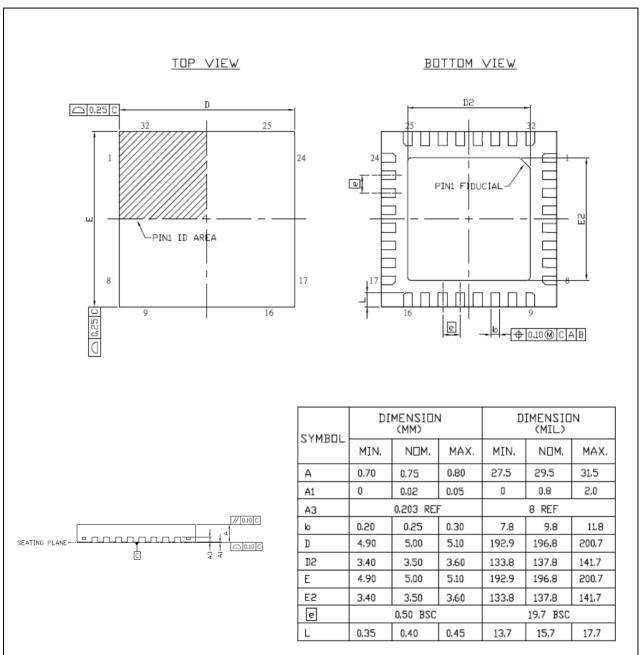

| Figure 2-1 ISD2360 QFN 32-Lead Package                  |  |

|---------------------------------------------------------|--|

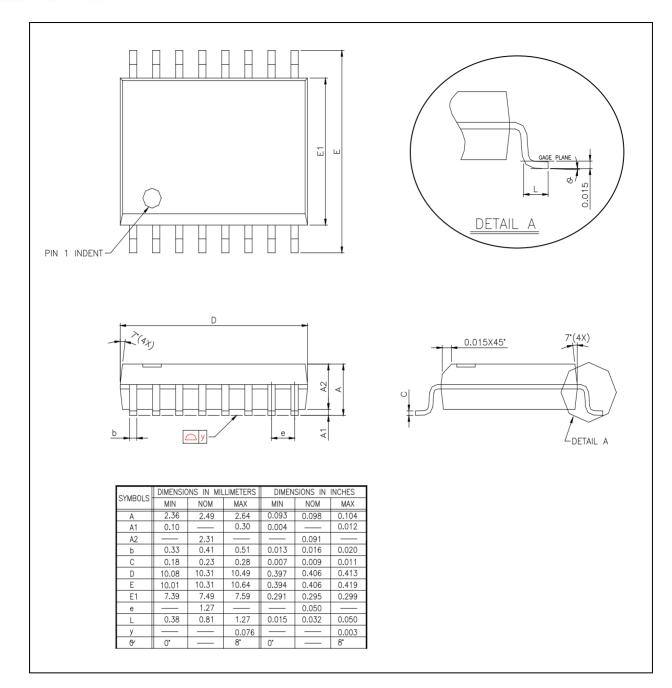

| Figure 2-2 ISD2360 SOP 16-Lead 300 mil Package 4        |  |

| Figure 3-1 ISD2360 Block Diagram7                       |  |

| Figure 5-1 GPIO Pad Structure 11                        |  |

| Figure 5-2 ISD2360 Signal Path 12                       |  |

| Figure 5-3 PWM Output Thermal Shutdown 15               |  |

| Figure 6-1 System Reserved Voice Macro Flow Chart 18    |  |

| Figure 6-2 POR Reset Failure from Power Supply Glitches |  |

| Figure 7-1 ISD2360 Memory Organization                  |  |

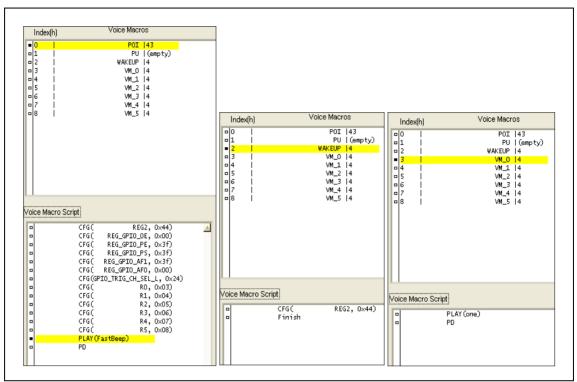

| Figure 7-2 Sample_Project_1 Configuration               |  |

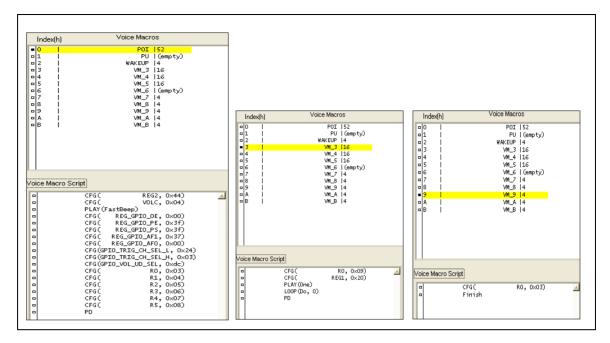

| Figure 7-3 Sample_Project_2 Configuration               |  |

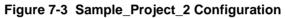

| Figure 7-4 Sample_Project_3 Configuration               |  |

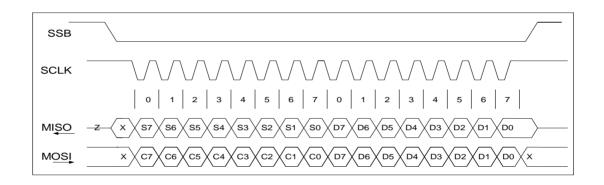

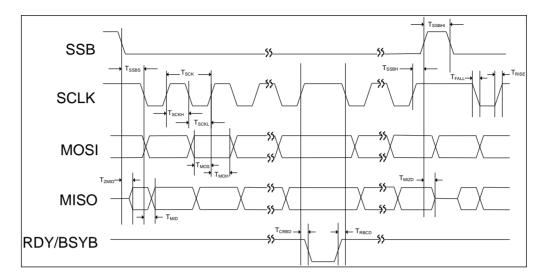

| Figure 8-1 SPI Data Transaction Waveform                |  |

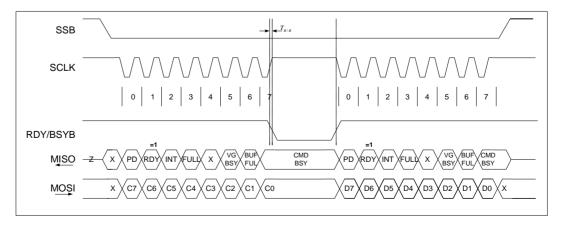

| Figure 8-2 RDY/BSYB Timing for SPI Write Transactions   |  |

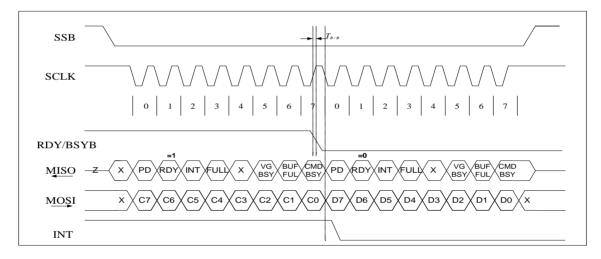

| Figure 8-3 RDY/BSYB Ignored for SPI Transactions        |  |

| Figure 8-4 SPI Read De-Compressed Data (Playback) 43    |  |

| Figure 8-5 SPI Send Compressed Data to Decode           |  |

| Figure 10-1 SPI Application under MCU Control           |  |

| Figure 10-2 GPIO Trigger Standalone Application         |  |

| Figure 11-1 SPI Timing                                  |  |

| Figure 12-1 QFN 32-Lead Package                         |  |

| Figure 12-2 SOP 16-Lead Package                         |  |

### List of Tables-

| Table 2-1  | 32-Lead QFN Pin Descriptions                           | 4  |

|------------|--------------------------------------------------------|----|

| Table 2-2  | SOP 16-Lead Pin Descriptions                           | 6  |

| Table 4-1  | Device Status Register Description                     | 8  |

| Table 4-2  | Interrupt Status Register Description                  | 9  |

| Table 5-1  | AF1/AF0 Bit Combinations for GPIO Pin Function Mode 1  | 0  |

| Table 5-2  | GPIO Pin Function Modes 1                              | 1  |

| Table 5-3  | Checksum Register Result Data Storage 1                | 3  |

| Table 5-4  | C Code Example Fletcher-32 Checksum Calculation 1      | 3  |

| Table 5-5  | Indirect Reference Registers R0-R7 1                   | 4  |

| Table 5-6  | GPIO Pin and Indirect Reference Register Association 1 | 4  |

| Table 6-1  | Available Sample Rates 1                               | 7  |

| Table 7-1  | Memory Data Sequence without Reserved User Data        | 24 |

| Table 7-2  | Memory Header MP_CFG Byte                              | 25 |

| Table 7-3  | Memory Protection Scheme                               | 25 |

| Table 7-4  | Voice Macro Commands                                   | 27 |

| Table 8-1  | SPI Commands                                           | 37 |

| Table 8-2  | SPI Commands vs. Status                                | 38 |

| Table 9-1  | Register Operations5                                   | 50 |

| Table 11-7 | 1 Operating Conditions (Industrial Packaging)5         | 59 |

| Table 11-2 | 2 SPI Timing6                                          | 51 |

### 1. General Description

#### Overview

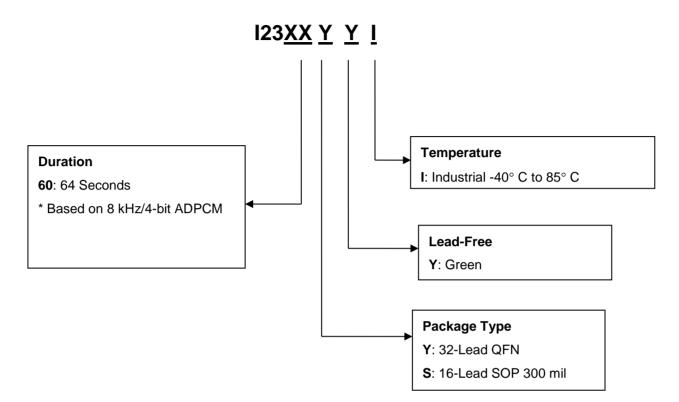

The ISD2360 3-channel digital ChipCorder<sup>®</sup> provides single-chip storage and playback of high quality audio. The ISD2360 features digital de-compression, comprehensive memory management, Flash storage, an integrated audio signal path with up to 3 channel concurrent playback and a Class D speaker driver capable of delivering 1 W of power. The ISD2360 utilizes Flash memory, in 1-Kbyte sectors, to provide non-volatile audio playback for a single-chip audio playback solution for up to 64 seconds duration (based on 8 kHz/4-bit ADPCM compression). This eliminates the need for additional EEPROM/Flash devices.

The ISD2360 can be controlled and programmed through a Serial Peripheral Interface (SPI) or can operate in standalone mode by triggers applied to the device's six General Purpose Input/Output (GPIO) pins.

The ISD2360 includes an internal oscillator and requires no external clock sources or components other than a speaker to deliver quality audio prompts or sound effects to enhance user interfaces. The ISD2360 also provides higher sampling frequencies, improved Signal-to-Noise Ratios (SNR), reduced power consumption, fast programming time and integrated program verification.

#### Features

- Performance Enhancements

- o 3-channel mixing playback

- GPIO parallel processing: supports dynamic change on GPIO output during playback

- EMI, EFT, ESD improvements

- $\circ$  1 W power output at 5 V

- Duration—64 sec. based on 8 kHz/4-bit ADPCM in 2 Mbits of Flash storage (256 KB)

- Audio Management

- Store pre-recorded audio (Voice Prompts) using high quality digital compression

- Use simple index-based commands for playback no address needed

- Execute pre-programmed macro scripts (Voice Macros) designed to control the configuration of the device and playback Voice Prompts sequences

- Path and Playback Control

- Audio streaming for up to 3 channels can be mixed and played back concurrently

- Independent counters for each channel enable user micro-management on Voice Macro execution

- $\circ$  Mask Jump for branch execution; based on internal register or external GPIO pin

- Control

- Serial Peripheral Interface (SPI) for microprocessor control and programming

- Standalone control when customized Voice Macro scripts are assigned to GPIO trigger pins

- Sample Rates

- o 8 sampling frequencies available: 4, 5.3, 6.4, 8, 10.67, 12.8, 16 and 32 kHz

- o Each Voice Prompt can have its own optimal sample rate

- De-Compression Algorithms

- $\circ~\mu\text{-Law:}$  6, 7 or 8 bits per sample.

- Differential µ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample

- Enhanced ADPCM: 2, 3, 4 or 5 bits per sample

- Variable bit-rate optimized compression allows best possible compression given a metric of Signal-to-Noise Ratios (SNR) and background noise levels

- Clock Source: Internal oscillator with internal reference, factory trimmed to ±1% deviation at room temperature

- Output

- $\circ~$  Pulse Wave Modulation (PWM): Class D speaker driver to direct drive an 8  $\Omega~$  speaker or buzzer

- Delivers 1W at 5V supply

- $\circ~$  Delivers 400mW at 3V supply

- I/Os

- o SPI interface: MISO, MOSI, SCLK, SSB for commands and digital audio data

- $\circ~$  6 General Purpose I/O (GPIO) pins multiplexed with the SPI interface

- Flash Storage

- o 2 Mbits of storage for combined audio/data content

- Fast programming time (20 μs/byte)

- Erase sector size 1 Kbyte, sector erase time 2 ms

- $\circ$   $\;$  Integrated memory checksum calculation for fast verification

- Endurance >100K cycles; retention > 10 years

- Operating Voltage: 2.4-5.5 V

- Packages, Green:

- QFN 32-Lead

- o SOP 16-Lead 300 mil

- Temperature Range: Industrial: -40° C to 85° C

### 2. Pin Configurations

#### 2.1 Pin Diagrams

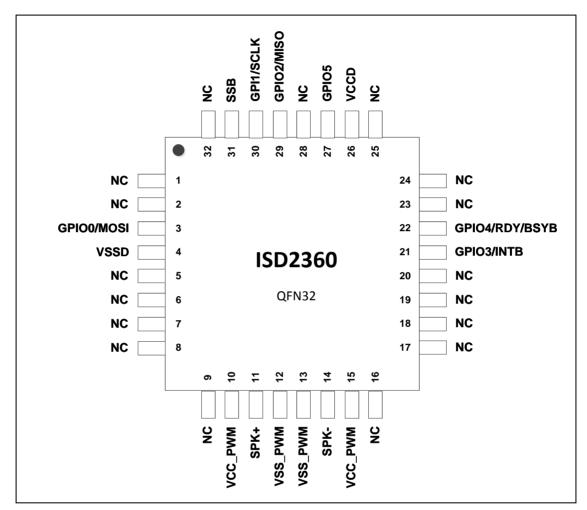

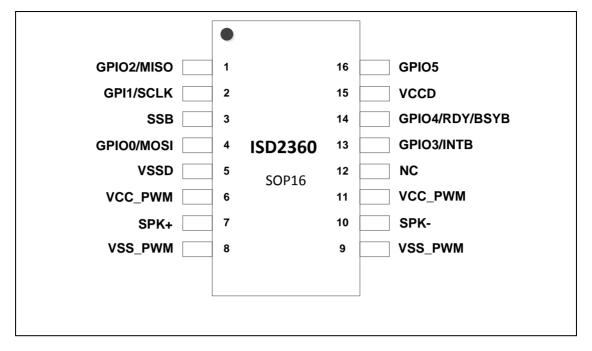

The ISD2360 ChipCorder is available in QFN 32-Lead and SOP 16-Lead 300 mil packages, as shown in Figure 2-1 and Figure 2-2.

Note: The large center exposed pad under the QFN 32-Lead package should be connected to VSSD on the board to ensure good heat dissipation and mechanical stability.

Figure 2-2 ISD2360 SOP 16-Lead 300 mil Package

#### 2.2 Pin Descriptions

п

The pin descriptions for the ISD2360 in QFN 32-Lead package and in SOP 16-Lead 300 mil package are provided in Table 2-1 and Table 2-2, respectively.

| Pin | Pin Name   | I/O | Function                                                                                                                                                                             |  |  |  |  |

|-----|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 2   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 3   | GPIO0/MOSI | Ι   | Master-Out-Slave-In. Serial input to the ISD2360 from the host.<br>Can be configured as a General Purpose I/O pin.                                                                   |  |  |  |  |

| 4   | VSSD       |     | Digital Ground.                                                                                                                                                                      |  |  |  |  |

| 5   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 6   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 7   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 8   | NC         |     | This pin should remain Not Connected                                                                                                                                                 |  |  |  |  |

| 9   | NC         |     | This pin should remain Not Connected.                                                                                                                                                |  |  |  |  |

| 10  | VCC_PWM    | Ι   | Digital Power for the PWM Driver. It can be from a separate power supply other than VCCD.                                                                                            |  |  |  |  |

| 11  | SPK+       | 0   | PWM driver positive output.<br>The SPK+ output and the SPK- pin provide a differential output to drive an 8 $\Omega$ speaker or buzzer. During power down, this pin is in tri-state. |  |  |  |  |

| 12  | VSS_PWM    | I   | Digital Ground for the PWM Driver.                                                                                                                                                   |  |  |  |  |

| 13  | VSS_PWM    |     | Digital Ground for the PWM Driver.                                                                                                                                                   |  |  |  |  |

| 14  | SPK-       | 0   | PWM driver negative output.                                                                                                                                                          |  |  |  |  |

Table 2-1 32-Lead QFN Pin Descriptions

## ISD2360 Design Guide

| Pin | Pin Name              | I/O | Function                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |                       |     | The SPK- output and the SPK+ pin provide a differential output to drive an 8 $\Omega$ speaker or buzzer. During power down, this pin is tri-state.                                                                                                                            |  |  |  |  |

| 15  | VCC_PWM               | I   | Digital Power for the PWM Driver. It can be from a separate power supply other than VCCD.                                                                                                                                                                                     |  |  |  |  |

| 16  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 17  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 18  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 19  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 20  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 21  | GPIO3/INTB            | 0   | Active low interrupt request pin.<br>This pin is an open-drain output.<br>Can be configured as a General Purpose I/O pin.                                                                                                                                                     |  |  |  |  |

| 22  | GPIO4/RDY/<br>BSYB    | 0   | Output pin reports the status of data transfer on the SPI interface. "High" indicates the ISD2360 is ready to accept n SPI commands or data. Can be configured as a General Purpose I/O pin.                                                                                  |  |  |  |  |

| 23  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 24  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 25  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 26  | VCCD                  | Ι   | Digital Power. It can be from a separate power supply other than VCC_PWM.                                                                                                                                                                                                     |  |  |  |  |

| 27  | GPIO5                 | I/O | General Purpose I/O pin                                                                                                                                                                                                                                                       |  |  |  |  |

| 28  | NC                    |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |  |

| 29  | GPIO2/MISO            | 0   | Master-In-Slave-Out. Serial output from the ISD2360 to the host. This pin is in tri-state when SSB=1.                                                                                                                                                                         |  |  |  |  |

|     |                       |     | Can be configured as a general purpose I/O pin.                                                                                                                                                                                                                               |  |  |  |  |

| 30  | GPI1/SCLK             | Ι   | Serial Clock input to the ISD2360 from the host.<br>Can be configured as a General Purpose input pin.                                                                                                                                                                         |  |  |  |  |

| 31  | SSB                   | I   | Slave Select input to the ISD2360 from the host.<br>When SSB is low, the device is selected and responds to<br>commands on the SPI interface. When asserted, GPIO0/1/2<br>automatically configure to MOSI/SCLK and MISO respectively.<br>SSB has an internal pull-up to VCCD. |  |  |  |  |

| 32  | NC                    |     | This pin should remain Not Connected.                                                                                                                                                                                                                                         |  |  |  |  |

| -   | center<br>exposed pad |     | The center pad under the QFN 32-Lead package is connected to VSSD internally.                                                                                                                                                                                                 |  |  |  |  |

nuvoTon

| Table 2-2 | SOP | 16-Lead Pin | Descriptions |

|-----------|-----|-------------|--------------|

|-----------|-----|-------------|--------------|

| Pin | Pin Name           | I/O | Function                                                                                                                                                                                                                                                                      |  |  |  |

|-----|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | GPIO2/MISO         | 0   | Master-In-Slave-Out. Serial output from the ISD2360 to the host. This pin is in tri-state when SSB=1.                                                                                                                                                                         |  |  |  |

|     |                    |     | Can be configured as a general purpose I/O pin.                                                                                                                                                                                                                               |  |  |  |

| 2   | GPI1/SCLK          | I   | Serial Clock input to the ISD2360 from the host.<br>Can be configured as a General Purpose input pin.                                                                                                                                                                         |  |  |  |

| 3   | SSB                | Ι   | Slave Select input to the ISD2360 from the host.<br>When SSB is low, the device is selected and responds to<br>commands on the SPI interface. When asserted, GPIO0/1/2<br>automatically configure to MOSI/SCLK and MISO respectively.<br>SSB has an internal pull-up to VCCD. |  |  |  |

| 4   | GPIO0/MOSI         | I   | Master-Out-Slave-In. Serial input to the ISD2360 from the host.<br>Can be configured as a General Purpose I/O pin.                                                                                                                                                            |  |  |  |

| 5   | VSSD               |     | Digital Ground.                                                                                                                                                                                                                                                               |  |  |  |

| 6   | VCC_PWM            | I   | Digital Power for the PWM Driver. It can be from a separate power supply other than VCCD.                                                                                                                                                                                     |  |  |  |

| 7   | SPK+               | 0   | PWM driver positive output.<br>The SPK+ output and the SPK- pin provide a differential output to drive an 8 $\Omega$ speaker or buzzer. During power down, this pin is in tri-state.                                                                                          |  |  |  |

| 8   | VSS_PWM            | I   | Digital Ground for the PWM Driver.                                                                                                                                                                                                                                            |  |  |  |

| 9   | VSS_PWM            | I   | Digital Ground for the PWM Driver.                                                                                                                                                                                                                                            |  |  |  |

| 10  | SPK-               | 0   | PWM driver negative output.<br>The SPK- output and the SPK+ pin provide a differential output<br>to drive an 8 $\Omega$ speaker or buzzer. During power down, this<br>pin is tri-state.                                                                                       |  |  |  |

| 11  | VCC_PWM            | Ι   | Digital Power for the PWM Driver. It can be from a separate power supply other than VCCD.                                                                                                                                                                                     |  |  |  |

| 12  | NC                 |     | This pin should remain Not Connected                                                                                                                                                                                                                                          |  |  |  |

| 13  | GPIO3/INTB         | 0   | Active low interrupt request pin.<br>This pin is an open-drain output.<br>Can be configured as a General Purpose I/O pin.                                                                                                                                                     |  |  |  |

| 14  | GPIO4/RDY/<br>BSYB | 0   | Output pin reports the status of data transfer on the SPI<br>interface. "High" indicates the ISD2360 is ready to accept new<br>SPI commands or data. Can be configured as a General<br>Purpose I/O pin.                                                                       |  |  |  |

| 15  | VCCD               | I   | Digital Power. It can be from a separate power supply other than VCC_PWM.                                                                                                                                                                                                     |  |  |  |

| 16  | GPIO5              | I/O | General Purpose I/O pin                                                                                                                                                                                                                                                       |  |  |  |

nuvoton

### 3. Block Diagram

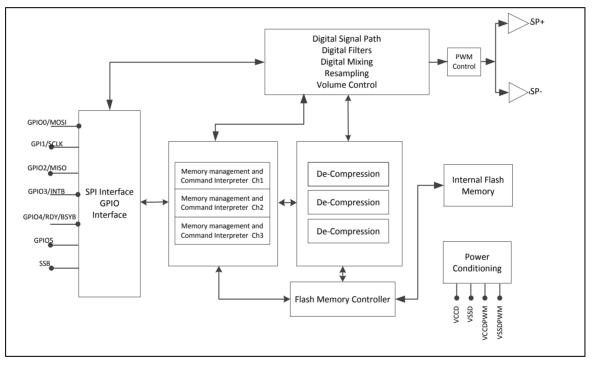

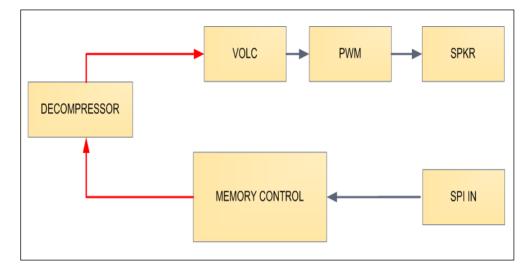

The major functional blocks of the ISD2360 ChipCorder, as shown in **Figure** 3-1 include:

- SPI and GPIO Interfaces

- Memory Management and Command Interpreters

- De-Compression

- Digital Signal Path Filtering, Mixing, Sampling and Volume Control

- PWM Control

- Internal Flash Memory

- Power Conditioning

- Flash Memory Controller

The ISD2360 can be controlled and programmed through a Serial Peripheral Interface (SPI) or can operate in standalone mode by triggers applied to the device's six General Purpose Input/Output (GPIO) pins. Voice Prompt and Voice Macro commands facilitate fast programming.

The ISD2360 ChipCorder provides 2 Mbits of Flash storage for combined audio/data content. Memory is available in 1-Kbyte sectors, eliminating the need for additional serial EEPROM/Flash devices. The Flash memory provides non-volatile audio playback for a single-chip audio playback solution for up to 64 seconds duration (based on 8 kHz/4-bit ADPCM compression).

### 4. Device Status

The ISD2360 status can be acquired by querying the *Device Status Register* and the *Interrupt Status Register*. After receiving a READ\_STATUS command, the ISD2360 ChipCorder continues to send back the device status byte and the interrupt status byte in turn, as long as the master provides the clock.

During an SPI transaction, the ISD2360 continually sends back its current status via MISO. When executing an SPI command or a Voice Macro command (refer to section 7.3 for details of Voice Macro) script, the ISD2360 continually updates its device status register bits. Upon completion of an SPI command or a Voice Macro command, the ISD2360 updates its interrupt status register bits.

#### 4.1 Device Status Register

During an SPI transaction, for all commands except digital reading commands, the device status byte is sent back from device via MISO for every byte of data sent to the ISD2360.The details of the device status bits are shown in Table 4-1.

| Status Byte                                                                                             |          |     |   |         |         |         |         |  |  |

|---------------------------------------------------------------------------------------------------------|----------|-----|---|---------|---------|---------|---------|--|--|

| Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |          |     |   |         |         |         |         |  |  |

| PD                                                                                                      | DBUF_RDY | INT | - | CH2_BSY | CH1_BSY | CH0_BSY | DIG_BSY |  |  |

Table 4-1

Device Status Register Description

The individual bits of the Device Status Register refer to the following conditions:

- **PD** If this bit is set, the device is powered down. The DBUF\_RDY bit will be low. When PD is high, only the READ\_STATUS, READ\_INT and PWR\_UP commands are accepted. If any other command is sent, it is ignored and no interrupt for an error is generated.

- **DBUF\_RDY** In Power Down status, this bit is low indicating the device can only accept a PWR\_UP (power up) command. When PD is low, this bit reflects the state of the RDY/BSY pin.

- **INT** Indicates that an interrupt has been generated. The interrupt is cleared by the READ\_INT command. The Interrupt type can be determined by the bits of the Interrupt Status Byte.

- **CHx\_BSY** When high, this bit indicates that channel [x] is in one of the following conditions:

- Processing a Voice Macro

- Processing a Voice Prompt

- Channel is waiting to process existing command in command buffer

- GPIO command is pending

Once set, Channel [x] will not respond to a new audio command until it returns low.

**DIG\_BUSY** When high, this bit indicates that the Flash controller is still processing a digital memory access. For device erase commands, such as ERASE\_MEM and CHIP\_ERASE, the user can poll this bit to determine if the erasure is complete.

#### 4.2 Device Interrupt Register

nuvoton

Whenever the ISD2360 generates an interrupt, the *Interrupt Status Register* holds flags that indicate the type of interrupt that was generated. The interrupt bits are shown in **Table** 4-2. These flags will remain set until a READ\_INT command clears them and the hardware interrupt pin (INTB) is set. Some interrupts require further servicing to remove the condition generating the interrupt; for instance, a FIFO full or empty interrupts. If the condition is not serviced before a READ\_INT, the device will immediately generate a new interrupt. To respond to an interrupt, use the following procedure:

- READ\_STATUS to determine which interrupt flags are set.

- Service the interrupt appropriately.

- READ\_INT to determine if a new interrupt has occurred during the service routines.

- If a new interrupt is detected, go to step 2. READ\_INT will clear the interrupt status.

#### Table 4-2 Interrupt Status Register Description

| Interrupt Status Byte |         |        |         |         |         |         |         |  |  |  |  |

|-----------------------|---------|--------|---------|---------|---------|---------|---------|--|--|--|--|

| Bit 7                 | Bit 6   | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |  |  |

| TALARM_INT            | MPT_ERR | WR_FIN | CMD_ERR | OVF_ERR | CH2_FIN | CH1_FIN | CH0_FIN |  |  |  |  |

The individual bits of the Interrupt Status Register refer to the following conditions:

- INT An interrupt has been generated. The interrupt is cleared by the READ\_INT command.

- **TALARM\_INT** Indicates that a temperature alarm has been set.

- **MPT\_ERR** Indicates a memory protection error. Digital access is attempted for protected memory.

- **WR\_FIN** Indicates a digital write command has finished writing to the Flash memory.

- **CMD\_ERR** An invalid command was sent to the device. The invalid command will be ignored because the command buffer was full, a Voice Macro has been active, or the device was not ready to respond to an erase command.

- **OVF\_ERR** This error is generated if the host illegally tries to read or write data while the RDY/BSYB pin is low. It is also generated if a digital read or write attempts to read or write past the end of memory.

- **CHx\_FIN** This bit indicates an interrupt was generated because a command finished executing on Channel X. A CHx\_FIN interrupt will be generated each time a Voice Macro or Voice Prompt play finishes.

### 5. Device Configuration

The ISD2360 is configured by writing to a set of configuration registers. This can be accomplished either by sending an SPI command, such as WR\_CFG\_REG, or by executing Voice Macros that contain configuration commands.

All configuration registers are reset to their default values when there is a reset condition. When the ISD2360 is in Power Down Mode, a group of 3 V registers will retain their values while all other registers lose their content. Note the difference between Power Down and Power Off: Power Down means the device is entering the standby state with the PD bit set; Power Off means the device no longer has power

Refer to Section 9 REGISTER OPERATIONS for more detailed register information.

#### 5.1 Device ID

The ISD2360 responds to an SPI READ\_ID command by sending out its 4-byte identification data through the MISO line. Within these 4 bytes, the first byte is the ISD digital ChipCorder family ID which is 0x05 for ISD2360. The following three bytes are a JEDEC compliant code indicating the memory type; they are manufacturer ID, memory type ID and memory size byte with values of 0xEF, 0x20 and 0x60 respectively, for an ISD2360 device.

#### 5.2 Clock Configuration

The ISD2360 has an internal oscillator trimmed at manufacturing that requires no external components to operate. This oscillator provides an internal clock source that operates the

ISD2360 at a maximum audio sample rate  $F_{smax}$  of 32 kHz. The ISD2360 user should always use the clock from the internal oscillator with an internal reference that is the device default setting. By default, the ISD2360 device sets the clock register value as 0x00, which uses the internal oscillator with an internal reference. The user should not change the clock source.

#### 5.3 GPIO Configuration

#### 5.3.1 GPIO Pin Function Definition

The ISD2360 includes 6 GPIO pins. Each pin can be individually configured as an I/O pin with internal pull up/down capability, as an alternate function pin, or as a triggering pin. More specifically, the functional configuration of each GPIO pin may be one of the following four choices: an I/O pin, an alternate function pin, a falling-edge-triggering pin or a rising-and-falling-edge-triggering pin. Alternate function control registers, AF1 (0x1E) and AF0 (0x1F), define the specific function mode of each pin. The function mode of a GPIO pin is defined by AF1 bit0 and AF0 bit0, shown in Table 5-1. The configuration choices for each mode are identified in **Table** 5-2. The upper two bits of the AF1 and AF0 registers are don't care bits.

|                                              | Bit7 | Bit6 | Bit5              | Bit4              | Bit3              | Bit2              | Bit1             | Bit0              |

|----------------------------------------------|------|------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|

| Alternate<br>Function<br>Control 1<br>(0x1E) | -    | -    | GPIO5<br>Function | GPIO4<br>Function | GPIO3<br>Function | GPIO2<br>Function | GPI1<br>Function | GPIO0<br>Function |

| Alternate<br>Function<br>Control 0<br>(0x1F) | -    | -    | Mode              | Mode              | Mode              | Mode              | Mode             | Mode              |

| Table 5-1 | AF1/AF0 Bit Combinations for GPIO Pin Function Mode |  |

|-----------|-----------------------------------------------------|--|

|-----------|-----------------------------------------------------|--|

| AF1 Bit | AF0 Bit | Configuration                   |

|---------|---------|---------------------------------|

| 0       | 0       | IO pin                          |

| 0       | 1       | Alternate Function              |

| 1       | 0       | Falling-edge Trigger            |

| 1       | 1       | Rising-and-falling edge Trigger |

#### Table 5-2 GPIO Pin Function Modes

Notes: GPIO1 is permanently low to guarantee SPI operation. Do not use as an output. GPIO5 does not have an alternate function.

#### 5.3.2 Special 3 V Registers

The ISD2360 device contains a group of special registers that can keep their value during power down. This special group includes registers in the range of 0x14-0x16 and 0x19-0x2F, and they are powered by an internal regulated 3V power supply.

During power down with  $1\mu$ A typical standby current, the GPIO triggering configuration in those 3V registers is still in effect; therefore, the ISD2360 can continue detecting a GPIO trigger during power down.

#### 5.3.3 GPIO Pin Structure

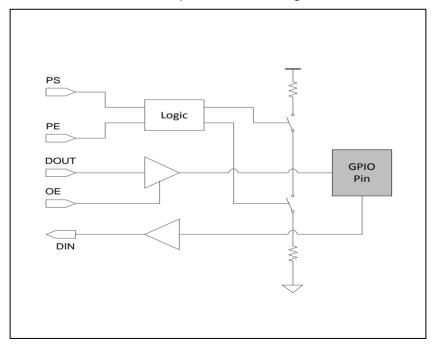

Once a GPIO pin is configured as an I/O pin, additional configuration of this I/O pin can be done by configuring the *Output Data Control Register*(0x19), *Output Enable Control Register*(0x1A), *Pull Enable Control Register*(0x1B), *Input Data Control Register*(0x1C) and *Pull Select Control Register*(0x1D). When the GPIO is selected for its alternate function, the DOUT and OE connections to the pin are driven by sources other than the DOUT and OE registers. The structure of the GPIO pads is shown in Figure 5-1.

#### Figure 5-1 GPIO Pad Structure

Regardless of the configuration of GPIO pins 0,1 and 2, these pins turn into the SPI interface

whenever the SSB pin goes low and revert back to their former configurations when the SSB pin goes back to high. On the contrary, GPIO pins 3, 4 and 5 do not automatically change their configurations when the SSB pin goes low. Users must especially pay attention to the GPIO4 (RDY/BSYB) as RDY/BSYB pin is required when performing a digital-read or digital-write. This requires manual configuration of GPIO4 to the RDY/BSYB function before the digital operation is required. GPI03 can be configured as an INTB pin so the user can monitor this pin for task completion.

Transitions on the GPIO pins can generate a GPIO\_INT interrupt. At the moment when the ISD2360 goes into a power down state, the status of the GPIO pins are latched. If the GPIO pin is configured as a triggering pin (interrupt enabled) and toggling on the pin is the valid triggering type indicated by AF1 and AF0, then when the toggling happens the ISD2360 device will execute a wake-up event.

#### 5.4 Signal Path Configuration

nuvoton

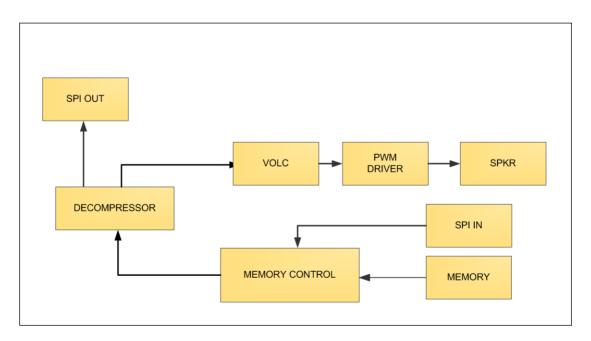

The signal path involves filtering, sample rate conversion, volume control and decompression. A block diagram of the signal path is shown in **Figure 5-2**. The two PWM driver output pins SPK-and SPK+ provide a differential output to drive an 8  $\Omega$  speaker or buzzer. Note that during power down, these pins are in tri-state.

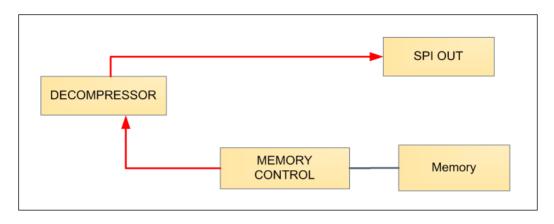

Pre-compressed audio signals transfer from memory or the SPI interface through the decompressor block to the PWM driver or SPI out. The audio level is adjustable via VOLC before going out to the PWM driver path. As shown in **Figure** 5-2, the possible path combinations are:

- MEMORY → DECOMPRESS → SPKR (Playback to Speaker)

- MEMORY → DECOMPRESS → SPI\_OUT (SPI Playback)

- SPI\_IN → DECOMPRESS → SPKR (SPI Decode to Speaker)

To configure a signal path, such as a playback path from memory to the PWM output, the user should enable decompression and PWM (write 0x44 to register 0x02). Later, audio can be played through the PWM output by issuing a PLAY\_VP command.

#### 5.5 Device Checksum

The ISD2360 is able to calculate the hardware checksum from the beginning of memory to a specified end address. To start a checksum calculation, the user should first reset the circuit by writing one followed by a zero, to the RST\_CHECKSUM bit in *Checksum Reset Register*, and then issue the SPI CHECKSUM command to initiate the calculation. The calculation is based on the Fletcher-32 algorithm, and the calculated checksum is stored in read-only *Checksum Register* 0x10-0x13, with the order of CHK\_SUM1[7:0], CHK\_SUM1[15:8], CHK\_SUM2[7:0] and CHK\_SUM2[15:8] respectively, as shown in Table 5-3.

| Table |        | nounn r | legis | ter neoun | Dulu Olorugi | •     |       |          |      |      |

|-------|--------|---------|-------|-----------|--------------|-------|-------|----------|------|------|

|       | Addre  | SS      | Acc   | ess Mode  | Value At Re  | set   | Nomir | al Value |      |      |

|       | 0x10-0 | x13     |       | R         | 0x0000       |       |       |          |      |      |

|       | Bit7   | Bit     | 6     | Bit5      | Bit4         | E     | Bit3  | Bit2     | Bit1 | Bit0 |

| 0x10  |        |         |       |           | CHK_SUM1     | [7:0] |       |          |      |      |

| 0x11  |        |         |       |           | CHK_SUM1[    | 15:8  | ]     |          |      |      |

| 0x12  |        |         |       |           | CHK_SUM2     | [7:0] |       |          |      |      |

| 0x13  |        |         |       |           | CHK_SUM2[    | 15:8  | ]     |          |      |      |

| Table 5-3 | Checksum | Register | Result | Data Storage |

|-----------|----------|----------|--------|--------------|

|-----------|----------|----------|--------|--------------|

Note that the hardware Fletcher-32 algorithm calculation starts from the specified end address and continues backwards until the data address reaches 0. Therefore, the software checksum calculation should follow the same sequence fetching data. An example of the ISD2360 Fletcher-32 calculation routine is shown in Table 5-4:

Table 5-4 C Code Example Fletcher-32 Checksum Calculation

```

unsigned int fletcher32 RevrseCalculate(unsigned char *data, size tlen)

{

int temp;

unsigned int sum1 = 0xffff, sum2 = 0xffff;

while (len) {

unsignedtlen = len> 360 ? 360 : len;

len -= tlen;

do {

sum1 += *data;

data--;

sum2 += sum1;

} while (--tlen);

sum1 = (sum1 & 0xffff) + (sum1 >> 16);

sum2 = (sum2 & 0xffff) + (sum2 >> 16);

}

// Second reduction step to reduce sums to 16 bits

sum1 = (sum1 & 0xffff) + (sum1 >> 16);

sum2 = (sum2 \& 0xfff) + (sum2 >> 16);

return sum2 << 16 | sum1;</pre>

```

#### 5.6 Indirect Reference Registers

nuvoTon

Eight 16-bit Indirect Reference Registers (R0-R7) can be used to store the following:

- Voice Prompt indexes for the SPI commands PLAY\_VP@Rn and PLAY\_VP\_LP@Rn

- Voice Macro index for the SPI command EXE\_VM@

- Voice Macro index associated with GPIO triggering

Table 5-5 shows the address locations of the R0-R7 registers.

| Access  | Mode   | Va | lue At Res | et | Nomina   | l Value |    |          |         |          |

|---------|--------|----|------------|----|----------|---------|----|----------|---------|----------|

| R/W     | 1      |    | 0x00xx     |    |          |         |    |          |         |          |

| 0x20    | 0x21   |    | 0x22       |    | 0x23     | 0x24    | ŀ  | 0x25     | 0x26    | 0x27     |

| R0[7:0] | R0[15: | 8] | R1[7:0]    | R  | R1[15:8] | R2[7:0  | D] | R2[15:8] | R3[7:0] | R3[15:8] |

| 0x28    | 0x29   |    | 0x2A       |    | 0x2B     | 0x2C    | ;  | 0x2D     | 0x2E    | 0x2F     |

| R4[7:0] | R4[15: | 8] | R5[7:0]    | R  | R5[15:8] | R6[7:0  | D] | R6[15:8] | R[7:0]  | R1[15:8] |

Normally when a GPIO pin is configured as a GPIO trigger pin, the entry index of its associated Voice Macro should be written into the corresponding Indirect Reference Register in POI Voice Macro, so the associated Voice Macro can be executed once the trigger happens. The association between a GPIO pin and its Indirect Reference Register is fixed by hardware, as shown in Table 5-6.

#### Table 5-6 GPIO Pin and Indirect Reference Register Association

|                                           | GPIO0 | GPIO1 | GPIO2 | GPIO3 | GPIO4 | GPIO5 | GPIO6 | GPIO7 |

|-------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Associated Indirect<br>Reference Register | R0    | R1    | R2    | R3    | R4    | R5    | R6    | R7    |

#### 5.7 GPIO4 Configuration for Digital Read/Write

The ISD2360 implements an internal FIFO with 4-byte depth which governs digital read/write operations flow throughput. For digital read operations, the host controller should only try to read from the SPI when the FIFO has data – when RDY/BSYB is high. For digital write operations, the host controller should only try to write into ISD2360 via SPI when the FIFO has vacant space – when RDY/BSYB is high.

The GPIO4 pin can be configured as RDY/BSYB pin to reflect this internal FIFO status. Although the host controller can always rely on polling the DBUF\_RDY bit to achieve the flow control, utilizing a direct RDY/BSYB pin hardware feature provides a much easier and more efficient solution. To configure the GPIO4 pin to function as a dedicated RDY/BSYB pin, write AF1 bit4 as 0 and AF0 bit4 as 1.

Flow control through the RDY/BSYB pin, or through the DBUF\_RDY bit using a pure software solution must be implemented for the following SPI digital operations:

- **DIG\_READ** Read from memory, for example.

- **DIG\_WRITE** Programming the ISD2360, for example.

- **SPI\_PCM\_READ** De-compress the memory data, then read the de-compressed 16-bit PCM data from the SPI interface.

- **SPI\_SND\_DEC** Send compressed data to ISD2360, allow the ISD2360 to de-compress the data and then play it out.

#### 5.8 Fast De-Bounce for GPIO Trigger

The default value of FAST\_DEB bit in the *De-bounce Time Control Register* is zero, which gives 20 ms de-bounce time for the ISD2360 GPIO trigger. Writing one to this bit enables the fast de-bounce feature, and the de-bounce time will be reduced to 8 ns. Fast de-bounce time should be used only in such situations in which fast speed is desired, and more importantly, the triggering signal is very clean without glitches – usually done by a MCU controlled I/O line. This allows a much faster and reliable IO controlled GPIO trigger to be achieved.

#### 5.9 Thermal Shutdown

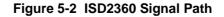

The ISD2360 device PWM driver can deliver a maximum output of nearly 1 Watt when operating at 5 V. With the increase of the delivered output power, the heat generated also increases. To prevent the accumulating heat from burning out the device, a thermal shutdown feature is implemented which is able to automatically shut down the PWM output when the temperature reaches the shutdown threshold.

The ISD2360 PWM output thermal shutdown feature is shown in **Figure 5-3**. When the device temperature reaches the threshold Talarm, the device automatically shuts down its PWM output while the rest of the device continues to operate. When the temperature of the ISD2360 drops to the level around (Talarm-10) C°, the PWM module resumes operation. For more details regarding the Talarm setting, refer to the *Thermal Control Register* description in Section 9 REGISTER OPERATIONS.

Figure 5-3 PWM Output Thermal Shutdown

### nuvoTon

### 6. Operational Description

#### 6.1 Overview

In almost all cases, the ISD2360 needs to be programmed before being put into use in the field. A GUI software, *ISD-VPE2360* (Voice Prompt Editor for ISD2360 device) can be used to generate the application image file. Once the image file is ready, the user can choose to program the devices before populating them onto target systems, or to perform in-system programming in field.

In brief, the process for developing an ISD2360 application includes:

- Analyzing the application needs and decide on SPI or GPIO Trigger operation mode.

- Developing an *ISD-VPE2360* project; evaluate it on a demo system; and create the desired image file.

- Assembling the application target board using programmed devices, or using insystem programming in field.

The following sections describe the details involved in these procedures.

#### 6.2 Audio Storage

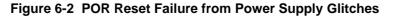

ISD2360 has a built-in 2-Mbit flash memory, which consists of 256 sectors with a sector size of 1024-byte each; that in total can give 64 seconds playback duration, given the 8 kHz ADPCM4 compression algorithm to be used.

ISD2360 is a playback only device. For it to be functional, in most cases the ISD2360 device must first be programmed. Programming is done by using the SPI *DIG\_WRITE* command, by writing an image file into the device Flash memory from the beginning of the Flash memory.

The GUI software, *ISD-VPE2360* enables users to create the application image file. Provided by Nuvoton Technology Corp., the *ISD-VPE2360* is available at no charge and can be downloaded from the Nuvoton website.

The *ISD-VPE2360* software generates the application image file based on the user's project. The image index/control data, called Memory Header, is stored from the first sector starting from address 0x00000. During power-on or power-up, the ISD2360 device automatically loads data from sector 0 for the initialization. Writing random data into the sector 0 has potential risk of causing the device to be unusable. Unless programming the device using the image file created by *ISD-VPE2360* Software, the user should avoid using sector 0.

For more details about memory organization, refer to Section 7 MEMORY MANAGEMENT.

#### 6.3 Sample Rates

The ISD2360 device is an audio de-compression device with a maximum supported sample rate at 32 KHz. The audio data compression is done by software, and the software should not use any compression method with a higher sample rate than 32 KHz.

By default (SRCFG=0), the ISD2360 generates the playback audio streaming according to the audio data header. To overturn the sample rate set by the audio data header and force the device to use the sample rate set by the *Sample Rate Overwrite Register*, the SRCFG bit in the *De-compres sion Control* Register needs to be set.

The forced sample rates available for playback are shown in Table 6-1

| SR[2:0] | Ratio to F <sub>smax</sub> | Sample Rate Fs (kHz) |

|---------|----------------------------|----------------------|

| 0       | 8                          | 4                    |

| 1       | 6                          | 5.44                 |

| 2       | 5                          | 6.4                  |

| 3       | 4                          | 8                    |

| 4       | 2.5                        | 12.8                 |

| 5       | 2                          | 16                   |

| 6       | 1                          | 32                   |

| 7       | 3                          | 10.67                |

#### Table 6-1 Available Sample Rates

#### 6.4 Audio Compression and De-Compression

ISD2360 hardware performs only audio de-compression. Audio compression relies on the supplied software – ISD-VPE2360 or Voice Prompt Editor. This software takes a wave file as the input; converts it to Voice Prompt which is the basic usable audio element in a project. After the project image is burned into device, the audio sound effect can be re-produced by an SPI command, such as PLAY\_VP.

When adding the wave file into a VPE project, the following algorithms are available:

- µ-Law: 6, 7 or 8 bits per sample.

- Differential µ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample

- Enhanced ADPCM: 2, 3, 4 or 5 bits per sample

- Variable-bit-rate optimized compression

Eight sampling frequencies (4, 5.3, 6.4, 8, 10.67, 12.8, 16 and 32 kHz) are available for each specified compression algorithm.

During playback, device hardware interprets the Voice Prompt header and de-compress the VP data accordingly. Unless overridden, ISD2360 hardware always plays the VP according to the sample rate specified in the VP header which is determined by the VPE project when adding wave files.

To override the setting in the VP header to enable play back of the audio streaming at a different sample rate, register 0x01 bit0 SRCFG must be set. Once the SRCFG bit is set, the device will play back audio streaming at the sample rate determined by register 0x00 bit5~7..

#### 6.5 System Voice Macro Flow Chart

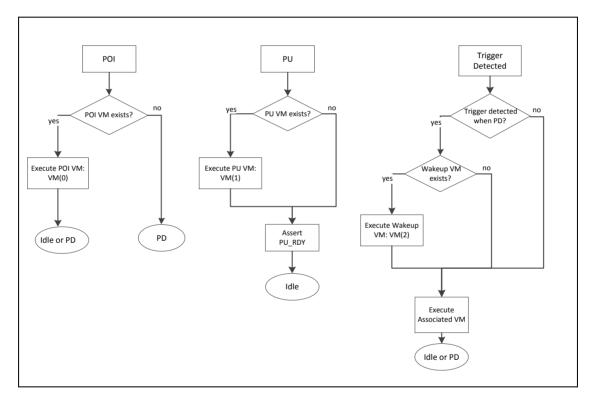

The ISD2360 reserves the first three Voice Macros for Power-On/Reset events, Power-UP initialization and GPIO triggering wake-up events with entry index 0x00, 0x01 and 0x02 respectively. The custom Voice Macro entry index starts from 0x03.

Whenever the ISD2360 detects a power-on reset condition, or receives a SPI RESET command, it begins a Power-On Initialization (POI) sequence and executes the POI Voice Macro, VM#0.

When the ISD2360 receives a Power Up command (PU) under power down state, it begins a power-up initialization (PU) sequence and executes PU Vocie Macro, VM#1. Note that if the device is already powered up, it will not execute PU Vocie Macro after receiving PU

#### command.

If the vectors for VM#0 or VM#1 do not exist in flash memory header, i.e. the POI Voice Macro and PU Voice Macro are not implemented, then a default routine for POI or PU is executed. The default sequence for POI is to power-down the ISD2360. The default PU sequence is to power up the device, assert the DBUF\_RDY bit and clear the PD bit in status byte, and stay idle (powered up). **Figure** 6-1 shows the device initialization execution flow.

Once powered on, no matter if it is in PU or PD state, the ISD2360 device constantly detects edge transition on all GPIO pins. If an edge transition is detected and it meets the triggering condition defined by the AF1 and AF0 registers, then it a valid trigger occurs. If the edge transition does not match the triggering condition, or there is no trigger configuration defined at all, then the edge transition will be ignored.

When a valid trigger occurs, depending on if the trigger occurs in PD state, the ISD2360 device will or will not execute the Wakeup Voice Macro before executing the triggering pin associated Voice Macro, as shown in Figure 6-1. Please note that the Wakeup Voice Macro is shared by all triggering events so Wakeup Voice Macro can be used for common initialization when any triggering event awakes the device.

Figure 6-1 System Reserved Voice Macro Flow Chart

#### 6.6 GPIO Trigger

#### 6.6.1 GPIO Trigger Basics

Once power on, the ISD2360 continually detects the GPIO signal level transition. If an edge is detected, the ISD2360 hardware will further check if the edge matches the triggering condition defined in the *Alternate Function Control 1* and *Alternate Function Control 0* registers. If it matches, then this edge will cause a valid trigger and a sequence of operations will follow, otherwise the edge will be discarded.

Depends on whether the device was in PU or PD state when the trigger happened, the ISD2360 device operates differently. If the device was in PU state when the trigger happened, the device will only execute the GPIO pin associated Voice Macro; if the device was in PD state when the trigger happened, then device will first execute the Wakeup Voice Macro – no matter if it is implemented, then go to execute the GPIO pin associated Voice Macro. The Wakeup Voice Macro is a system reserved Voice Macro with fixed index 0x02; it always exists even if it is not implemented. If the Wakeup Voice Macro is not implemented, then the device will simply run default hardware initialization and power itself up, before executing the trigger associated Voice Macro.

The GPIO triggering pin to VM association is determined by hardware. That is: GPIO0 trigger will execute the VM whose index is in register R0, GPIO1 trigger will execute the VM whose index is in R1, and so on. If a trigger occurs but the associated VM index is not prepared in advance in the corresponding indirect reference register, the chip behavior is unknown.

During a triggering execution, the ISD2360 uses the associated VM index to locate the starting and end address of the Voice Macro script data in its memory, and then fetches the VM command data for execution.

To implement the GPIO triggering function, the user can follow the steps listed below; mostly the configuration is done in POI Voice Macro.

- Prepare the triggering condition:

- Write Output Enable Control Register (0x1A) to configure the GPIO pin as an input pin.

- Write Output Enable Control Register (0x1B) and Pull Select Control Register (0x1D). Configure the GPIO pin pull status according to the hardware feature. For example: if press-button pulls the GPIO low, and a falling edge trigger is desired, then the GPIO pin should be configured as an input with internal pulled high.

- Assign the channel for the Voice Macro:

- Write GPIO Trigger Channel Select 1 (0x14) and GPIO Trigger Channel Select 2 (0x15) registers, so the associated VM can be assigned into the specified channel for execution.

- Configure the triggering mode:

- Write Alternate Function Control 1 (0x1E) and Alternate Function Control 0 (0x1F) registers.

- Write the associated Voice Macro index into the Indirect Reference Register R0~R5:

- Write CFG\_REG 0x20~0x2B.

- Edit the associated VM in the ISD-VPE2360 GUI environment.

After creating and programming the application image into the device, , the ISD2360 device is ready for use in a triggering application.

#### 6.6.2 SPI or GPIO Trigger

There are two ways to operate the ISD2360: via the SPI interface or through GPIO trigger. The SPI interface can be always available; whereas, GPIO trigger function mode is available only after the related registers are configured. The GPIO trigger is preemptive, where SPI operation is not preemptive.

#### 6.6.2.1 Pulling SSB low automatically claims the SPI interface

Each of the six ISD2360 GPIO pins can be configured to work at the one of the following four function modes: GPIO pin, alternate function pin, falling-edge triggering pin or falling-and-rising-edge triggering pin. The GPIO pin function modes are defined by AF1 (0x1E) and AF0 (0x1F) registers.

Regardless of the AF1 and AF0 setting, the GPIO0/MOSI, GPI1/SCLK and GPIO2/MISO three pins will be automatically changed to alternate function mode so that SPI transactions can proceed whenever the SSB bar is pulled low. And these three pin's function modes will automatically recover to what are specified by the AF1 and AF0 registers once the SSB bar is pulled back to high. The mode change for these three pins triggered by SSB level changing is done by hardware and is transparent to the user.

#### 6.6.2.2 Pulling SSB Low does not affect the triggering capability

Pulling SSB low has nothing to do with the triggering feature. In other words, if the SPI pins including MISO, MOSI and SCLK pins are configured as trigger pins, even after SSB is pulled low, edges on those pins can still trigger. Whether a pin can trigger or not solely depends on its setting in AF1 and AF0 registers.

#### 6.6.2.3 GPIO Trigger Execution is preemptive

For SPI commands to be valid and action to be taken, certain conditions must be met. As a general rule, to ensure the success of an SPI operation, the user must check the device status before sending the SPI commands.

Unlike the SPI operation, in GPIO Trigger operation, the ISD2360 always executes the associated VM in the assigned channel, regardless the current status of the channel. That is, even if the current channel is busy playing a Voice Prompt or executing other Voice Macro commands, all the activities in the channel will be terminated and the device will start to execute the Voice Macro associated with the latest trigger.

#### 6.6.2.4 SPI vs. GPIO Triggering Reliability

In most cases, especially in standalone applications, the setup of the GPIO triggering feature relies completely on the execution of the POI Voice Macro. In turn, having POI VM executed relies on the successful detection of the power-on reset condition, as in standalone applications, an SPI RESET command is not likely to be available.

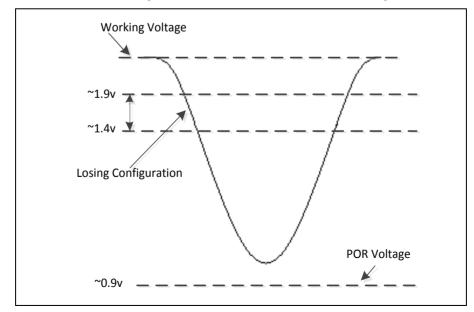

In user applications, there is a risk that power supply glitches causing device POI VM not be executed and hence the device will stop responding to the GPIO trigger after power on. **Figure** 6-2 shows how power supply glitches might cause POR (Power On Reset) failure and therefore, cause the 3 V registers of the ISD2360 to lose their configuration.

When the power supply drops to ~1.9 V, the 3 V registers of the ISD2360 start to lose their values. If the power supply continues to drop to a level lower than the POR (Power On Reset) voltage, which is about 0.9 V, then once the power supply rises back to normal working voltage, POI VM will be triggered to run and the register settings can be recovered. However, if the power supply lowers to a level where it causes the device 3V registers to lose value, but not low enough (lower then ~0.9 V) to cause POR event, then once the power supply rise back to working voltage, the POI VM will not get triggered and hence the device lose desired triggering settings and may malfunction as a result. Once this has occurred, the only way to recover is to cycle the power again.

A clean power supply is very much desired in trigger application; because that can greatly reduce or even eliminate the chances for device losing its configurations.

On the other hand, the SPI interface is guaranteed to be responsive in any circumstances. For applications which require extreme reliability, the user should give SPI operation preferred consideration.

#### 6.6.3 Volume Control via GPIO Trigger

By configuring the *Trigger Volume Control Register*, the user can use a GPIO Trigger to raise or lower the volume of the PWM output. GPIO trigger volume control provides 8 steps of attenuation, from maximum volume to maximum attenuation -63.75 dB. Note that the content of the *Volume Control Register* does not belong to the group of 3 V registers and the volume level is not retained at power down. When a GPIO trigger is configured as the volume up/down trigger, the ISD2360 device no longer executes its associated Voice Macro.

#### 6.7 Multi-Channel Feature

nuvoton

The ISD2360 is a 3-channel device. The 3-channel mixer allows the user to mix audio data on any or all of the three channels. By first filtering and up-sampling the data from the individual channel(s) to an intermediate frequency of 64 kHz, the ISD2360 allows the user to mix audio data on the three channels with independent sample rates. Channel mixing is performed following the up-sampling and prior to volume control.

#### 6.7.1 SPI Multi Channel

For audio playback operation started by an SPI command, the channel in which the playback is performed is determined by SPI\_CMD\_CH bits in the *Channel Control* Register. At any time, either one channel (0, 1, or 2) or all three channels may be in operation. Note that when all channels are selected, it is invalid to issue SPI play commands such as PLAY\_VP or PLAY\_VM. Otherwise, the command will be ignored and the CMD\_ERR bit will be set. However, when all channels are selected, issuing the STOP command is a valid operation, and all activities in all three channels will be stopped.

To mix multiple channels for mixed playback, the user should first choose one channel and start the first playback, then select another channel to start the second playback. The two playbacks streaming will be automatically mixed and sent to the PWM output if enabled. For SPI play command, the device always checks whether the current channel is available – as reflected by the CHn\_BSY bits in the Status Register. Issuing a SPI play command when the current channel is busy causes the play command to be ignored and the CMD\_ERR bit to be asserted. The SPI STOP command stops the audio activity in the current channel, but has no effect on other channels. When all channels are selected, a STOP command stops activities in all three channels.

#### 6.7.2 Multi Channel GPIO Trigger

A GPIO pin associated Voice Macro executes in its assigned channel. The two registers *GPIO Trigger Channel Select 1* and *GPIO Trigger Channel Select 2* specify the channel in which each of the six GPIO trigger-associated Voice Macros executes.

nuvoTon

Multiple GPIO pins can be associated with the same VM; and multiple VMs can be assigned to the same channel. If two GPIO trigger Voice Macros are to be executed in the same channel, the later triggered playback will preempt the earlier triggered playback.

A GPIO triggering associated VM preempts only its own channel; the execution in other channels is not affected. In total, the ISD2360 device can have 3 channels running in parallel. If a trigger VM is assigned to "all channels", i.e. 0x11 being written into the corresponding *GPIOn\_TRIG\_VH\_SEL* bits, the result is that the VM will preempt all 3 channels when triggered; execution will begin in Channel 0. The status bit *CH0\_BSY* will be set, which can in turn be preempted by another Channel 0 associated VM.

#### 6.8 VM Jump and Channel Counter Commands

The ISD2360 has several special VM commands added to its VM command set. They are the Voice Macro Branch and Channel Counter commands. VM Branch commands include the unconditional jump (GOTO) and conditional jump (MASK\_GOTO) commands. The Channel Counter uses the WAIT\_CHN\_CNT commands.

#### 6.8.1 VM Branch Commands

GOTO is an unconditional absolute jump command. Similar to the absolute jump command commonly available to a microcontroller instruction set, it branches from the current execution and jumps to execute another valid VM command. The next to be executed VM command does not need to belong to the current VM from which the device jumps; it can be any valid VM command anywhere within the device image.