### 8-bit Microcontroller

# KM101EF59R Datasheet

The information described in this Datasheet is the exclusive intellectual property of Nuvoton Technology Corporation Japan and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing document only for reference purposes of KM101EF59R based system design.

Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

Apr 11, 2012 Rev 1.01

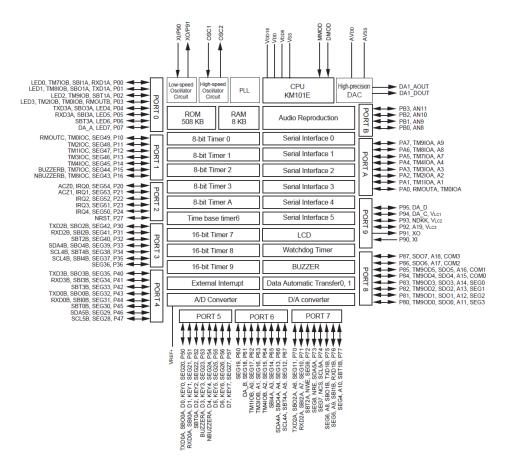

# 1. Overview

#### 1.1 Overview

The KM101E series of 8-bit single-chip microcontrollers incorporate multiple types of peripheral functions. This chip series is well suited for camera, VCR, MD, TV, CD, LD, printer, telephone, home automation, pager, air conditioner, PPC, fax machine, music instrument and other applications.

This LSI brings to embedded microcontroller applications flexible, optimized hardware configurations and a simple efficient instruction set. The KM101EF59R has an internal 928 KB (maximum) of ROM and 8 KB (maximum) of RAM. Peripheral functions include 6 external interrupts, 30 internal interrupts including NMI, 9 timer counters, 6 sets of serial interfaces, A/D converter, D/A converter,

LCD driver, watchdog timer, 2 sets of automatic data transfer, synchronous output function and buzzer output. The configuration of this microcontroller is well suited for application as a system controller in camera, timer selector for VCR, CD player, or minicomponent, and also suited for audio reproduction with a high-precision D/A converter.

With three oscillation system (high frequency: max. 20 MHz / low frequency: 32.768 kHz and PLL: frequency multiplier of high frequency) contained on the chip, the system clock can be switched to high frequency input (high speed mode), PLL input (PLL mode), or to low frequency input (low speed mode). The system clock is generated by dividing the oscillation clock. The best operation clock for the system can be selected by switching its frequency by software. High speed mode has the normal mode based on fpll/2 which is half clock generated from an original oscillation and PLL, and the double speed mode based on fpll which is clock generated from an original oscillation without dividing.

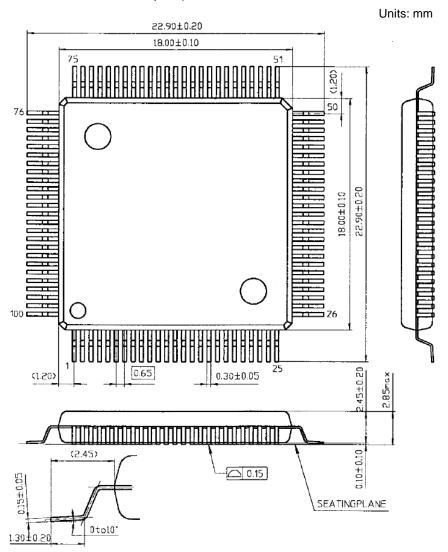

A machine cycle (min. instructions execution) in the normal mode is 100 ns when fosc is 20 MHz (at the time that PLL is not used). A machine cycle in the double speed mode is 50 ns when fosc is 20 MHz. A machine cycle in the PLL mode is 50 ns (maximum). The package is 100-pinQFP.

### 1.2 Product Summary

This datasheet describes the following models of the KM101EF59R.

Table: 1.1 Product Summary

| Model      | ROM Size | RAM Size | Classification       | Package     |

|------------|----------|----------|----------------------|-------------|

| KM101EF59R | 928 KB   | 8 KB     | Flash EEPROM version | QFP 100-pin |

# 2. Hardware Functions

• ROM Capacity 928 KB

• RAM Capacity 8 KB

• Package QFP 100-pin (18 mm x 18 mm, 0.65 mm pitch)

• Machine Cycle High speed mode

PLL mode

Low speed mode

•Clock Gear Operation speed of system clock is variable by changing the frequency

• Multiplied Clock High-speed frequency clock (fosc) can be multiplied by 2, 3, 4, 5, 6, 8 and 10.

• Memory bank Data memory space is expanded by the bank system.

Bank for the source address/Bank for the destination address.

• ROM correction Correcting address designation: up to 7 addresses possible

• Operation Modes NORMAL mode ( High speed mode)

PLL mode

SLOW mode (Low speed mode)

HALT mode STOP mode

(The operation clock can be switched in each mode.)

•Operating Voltage 2.2 V to 5.5 V

• Operating Temperature

-40°C to +85°C

#### • Interrupt 36 levels

<Watchdog timer>

NMI-Watchdog timer overflow

<Timer interrupts>

TM0IRQ-Timer 0 interrupt (8-bit timer)

TM1IRO-Timer 1 interrupt (8-bit timer)

TM2IRQ-Timer 2 interrupt (8-bit timer)

TM3IRQ-Timer 3 interrupt (8-bit timer)

TM4IRQ-Timer 4 interrupt (8-bit timer)

TM6IRQ-Timer 6 interrupt (8-bit timer)

TBIRQ-Clock timer interrupt

TM7IRQ-Timer 7 interrupt (16-bit timer)

T7OC2IRQTimer 7 interrupt (16-bit timer)

TM8IRQ-Timer 8 interrupt (16-bit timer)

T8OC2IRQTimer 8 interrupt (16-bit timer)

TM9IRQ-Timer 9 interrupt (16-bit timer)

T9OC2IRQTimer 9 interrupt (16-bit timer)

#### <Serial interrupts>

SC0TIRQ-Serial interface 0 interrupt

SCORIRQ-Serial interface 0 UART reception interrupt (peripheral function group interrupt)

SC1TIRQ-Serial interface 1 interrupt

SC1RIRQ-Serial interface 1 UART reception interrupt (peripheral function group interrupt)

SC2TIRQ-Serial interface 2 interrupt

SC2RIRQ-Serial interface 2 UART reception interrupt

SC3TIRO-Serial interface 3 interrupt

SC3RIRQ-Serial interface 3 UART reception interrupt (peripheral function group interrupt)

SC4TIRQSerial interface 4 interrupt

SC4SIRQSerial interface 4 stop condition interrupt (peripheral function group interrupt)

SC5TIRQSerial interface 5 interrupt (peripheral function group interrupt)

#### <A/D conversion end>

ADIRQ-AD conversion end (peripheral function group interrupt)

< Automatic Transfer Controller interrupts>

ATC0IRQ-ATC0 interrupt (peripheral function group interrupt)

ATC1IRQ-ATC1 interrupt (peripheral function group interrupt)

<External interrupts> Edge selectable

IRQ0:External interrupt (AC zero-cross detector, With/Without noise filter)

IRQ1:External interrupt (AC zero-cross detector, With/Without noise filter)

IRQ2:External interrupt (Both edges interrupt)

IRQ3:External interrupt (Both edges interrupt)

IRQ4:External interrupt (Both edges interrupt)

IRQ5:External interrupt (Key scan interrupt only)

<Audio interrupts>

Audio reproduction end interrupt

Audio phrase end interrupt

#### • Timer Counter

11 timers All timer counters generate interrupt (10 can be operated independently)

- 8-bit timer for general use: 5 sets

- 8-bit free-running timer: 1 set

- Time base timer: 1 set

- 16-bit timer for general use: 3 sets

- Simple 8-bit timer: 1 set

#### Timer 0 (8-bit timer for general use)

- Square wave output (timer pulse output), added pulse(2-bit) system PWM output (can be output to large current pin TM0IOB), event count, remote control carrier output, simple pulse with measurement

- Clock source

fpll, fpll/4, fpll/16, fpll/32, fpll/64, fpll/128, fs/2, fs/4, fs/8, fx, external clock, TimerA output

- Real timer output control

Control the timer (PWM) output by the falling edge of external interrupt 0 (IRQ0) with the follow 3 value; "High"-fixed, "LOW"-fixed and "Hi-Z"-fixed

#### Timer 1 (8-bit timer for general use)

- Square wave output (timer pulse output), event count, 16-bit cascade connected (timer0, 1) timer synchronous output event

- Clock source

fpll, fpll/4, fpll/16, fpll/32, fpll/64, fpll/128, fs/2, fs/4, fs/8, fx, external clock, TimerA output

#### Timer 2 (8-bit timer for general use)

- Square wave output (timer pulse output), added pulse(2-bit) system PWM output (can be output to large current pin TM2IOB), event count, simple pulse with measurement, 24-bit cascade connected (timer0, 1) timer synchronous output event

- Clock source

fpll, fpll/4, fpll/16, fpll/32, fpll/64, fpll/128, fs/2, fs/4, fs/8, fx, external clock, TimerA output

- Real timer output control

Control the timer (PWM) output by the falling edge of external interrupt 0 (IRQ0) with the follow 3 value; "High"-fixed, "LOW"-fixed and "Hi-Z"-fixed

#### Timer 3 (8-bit timer for general use)

- Square wave output (timer pulse output), event count, remote control carrier output, 16bit cascade connected (timer2), 32-bit cascade connected (timer0, 1, 2)

- Clock source

fpll, fpll/4, fpll/16, fpll/32, fpll/64, fpll/128, fs/2, fs/4, fs/8, fx, external clock, TimerA output

#### Timer 4 (8-bit timer for general use)

- Square wave output (timer pulse output), added pulse(2-bit) system PWM output, event count, serial transfer clock, simple pulse measurement

- Clock source

fpll, fpll/4, fpll/16, fpll/32, fpll/64, fpll/128, fs/2, fs/4, fs/8, fx, external clock, TimerA output

#### Timer 6 (8-bit free-running timer, Time base timer)

8-bit free-running timer

- Clock source

fpll, fpll/ $2^{12}$ , fpll/ $2^{13}$ , fs, fx, fx/ $2^{12}$ , fx/ $2^{13}$  Time base timer

- Interrupt generation cycle

fpll/2<sup>7</sup>, fpll/2<sup>8</sup>, fpll/2<sup>9</sup>, fpll/2<sup>10</sup>, fpll/2<sup>13</sup>, fpll/2<sup>15</sup>, fx/2<sup>7</sup>, fx/2<sup>8</sup>, fx/2<sup>9</sup>, fx/2<sup>10</sup>, fx/2<sup>13</sup>, fx/2<sup>15</sup>

• Timer Counter (continued)

Timer 7 (16-bit timer for general use)

- Clock source

fpll, fpll/2, fpll/4, fpll/16, fs, fs/2, fs/4, fs/16

1/1, 1/2, 1/4, 1/16 of the external clock, TimerA output

- Hardware organization

Compare register with double buffer: 2 sets

Input capture register: 1 set Timer interrupt: 2 vectors

- Timer functions

Square wave output (Timer pulse output), High precision PWM output (Cycle/Duty continuous changeable), IGBT output (Cycle/Duty continuous changeable) can be output to large current pin TM7IOB

Timer synchronous output, event count, Input capture function (Both edges can be operated)

-Real timer output control

Control the timer (PWM) output by the falling edge of external interrupt 0 (IRQ0) with the follow 3 value; "High"-fixed, "LOW"-fixed and "Hi-Z"-fixed

Timer 8 (16-bit timer for general use)

- Clock source

fpll, fpll/2, fpll/4, fpll/16, fs, fs/2, fs/4, fs/16

1/1, 1/2, 1/4, 1/16 of the external clock, TimerA output

- Hardware organization

Compare register with double buffer: 2 sets Input capture register: 1 set

Timer interrupt: 2 vectors

- Timer functions

Square wave output (Timer pulse output), High precision PWM output (Cycle/Duty continuous changeable) can be output to large current pin TM8IOB, event count, pulse width measurement, input capture (Both edge available), 32-bit cascade connected (Timer7, 8), 32-bit PWM output, Input capture is available at 32-bit cascade

Timer 9 (16-bit timer for general use)

- Clock source

fpll, fpll/2, fpll/4, fpll/16, fs, fs/2, fs/4, fs/16, 1/1, 1/2, 1/4, 1/16 of the external clock TimerA output

- Hardware organization

Compare register with double buffer: 2 sets Input capture register: 1 set

Timer interrupt: 2 vectors

- Timer functions

Square wave output (Timer pulse output), High precision PWM output (Cycle/Duty continuous changeable) can be output to large current pin TM9IOB, event count, pulse width measurement, input capture (Both edge available)

- Real timer output control

Control the timer (PWM) output by the falling edge of external interrupt 0 (IRQ0) with the follow 3 value; "High"-fixed, "LOW"-fixed and "Hi-Z"-fixed

TimerA output (Simple timer counter A)

Clock output for peripheral function

Time-out cycle can be selected from  $fs/2^{16}$ ,  $fs/2^{18}$ ,  $fs/2^{20}$ Watchdog timer

On detection of errors, hard reset is done inside LSI

Synchronous output function

Timer synchronous output, interrupt synchronous output Port 8 outputs the latched data, on the event timing of the synchronous output signal of timer 1, 2, or 7, or of the external interrupt 2 (IRQ2).

• Buzzer Output/Reverse Buzzer Output

Output frequency can be selected from fpll/2<sup>9</sup>,fpll/2<sup>10</sup>,fpll/2<sup>11</sup>,fpll/2<sup>12</sup>,fpll/2<sup>13</sup>,fpll/2<sup>14</sup>,  $fx/2^3, fx/2^4$

• Remote Control Carrier Output:

A remote control carrier output with duty cycle of 1/2 or 1/3 of timer 0 or timer 3 output are available.

A/D Converter 10-bit x 12 channels

• D/A Converter 8-bit x 4 channels

Data automatic transfer

#### 2 systems

#### ATC0

Data is transferred automatically in all memory space

- External request/internal event request/software request

- Maximum transfer cycles are 255

- Support continuous serial transmission / reception.

- Burst transfer function (Urgent stop of interrupts is contained.)

Data is transferred automatically in all memory space

- External request/internal event request/software request

- Maximum transfer cycles are 255

- Support continuous serial transmission / reception.

- Burst transfer function (Urgent stop of interrupts is contained.)

#### Serial Interface

#### 6 channels

Serial 0 (Full duplex UART / Synchronous serial interface)

Synchronous serial interface

- Transfer clock source

- fpll/2, fpll/4, fpll/16, fpll/64, fs/2, fs/4, Timer0,1,2,3,4 and A output, external clock

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- Sequence transmission, reception or both are available.

Full duplex UART (Baud rate timer, Timer0,1,2,3,4 and A)

- Parity check, Overrun error / Framing error detection

- Transfer size 7 to 8 bits can be selected.

Serial 1 (Full duplex UART / Synchronous serial interface)

Synchronous serial interface

- Transfer clock source

- fpll/2, fpll/4, fpll/16, fpll/64, fs/2, fs/4, Timer0,1,2,3,4 and A output, external clock

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- Sequence transmission, reception or both are available.

Full duplex UART (Baud rate timer, Timer0,1,2,3,4 and A)

- Parity check, Overrun error / Framing error detection

- Transfer size 7 to 8 bits can be selected.

• Serial Interface (continued)

Serial 2 (Full duplex UART / Synchronous serial interface)

Synchronous serial interface

- Transfer clock source

- fpll/2, fpll/4, fpll/16, fpll/64, fs/2, fs/4, Timer0,1,2,3,4 and A output, external clock

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- Sequence transmission, reception or both are available.

Full duplex UART (Baud rate timer, Timer0,1,2,3,4 and A)

- Parity check, Overrun error / Framing error detection

- Transfer size 7 to 8 bits can be selected.

Serial 3 (Full duplex UART / Synchronous serial interface)

Synchronous serial interface

- Transfer clock source

- fpll/2, fpll/4, fpll/16, fpll/64, fs/2, fs/4, Timer0,1,2,3,4 and A output ,external clock

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- Sequence transmission, reception or both are available.

Full duplex UART (Baud rate timer, Timer0,1,2,3,4 and A)

- Parity check, Overrun error / Framing error detection

- Transfer size 7 to 8 bits can be selected.

Serial 4 (multi master I2C / Synchronous serial interface)

Synchronous serial interface

- Transfer clock source

- fpll/2, fpll/4, fpll/8, fpll/32, fs/2, fs/4, Timer0,1,2,3,4 and A output, external clock

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- Sequence transmission, reception or both are available.

Multi master I2C

- 7-bit of slave address can be set.

- General call communication mode handling

#### Serial 5

- IIC slave interface

- IIC high-speed transfer mode (communication speed: 400 kbps)

- 7-bit or 10-bit of slave address can be set.

- General call communication mode handling

- •LED Driver

8 pins (Push-pull structure)

Automatic Reset

•LCD Driver LCD driver pins Segment output max. 55 pins (SEG0 to 54) SEG0 to 54 can be switched to I/O ports by 1 pin [Note: At reset, SEG0 to 54 are input ports.] Common output pins:4 pins COM0 to 3 can be switched to I/O ports by 1 pin Display mode selection Static 1/2 duty, 1/2 bias 1/3 duty, 1/3 bias 1/4 duty, 1/3 bias LCD driver clock - When the source clock is the main clock (fpll)  $1/2^{18}$ ,  $1/2^{17}$ ,  $1/2^{16}$ ,  $1/2^{15}$ ,  $1/2^{14}$ ,  $1/2^{13}$ ,  $1/2^{12}$ ,  $1/2^{11}$ - When the source clock is the sub clock (fx)  $1/2^9$ ,  $1/2^8$ ,  $1/2^7$ ,  $1/2^6$ - Timer0, 1, 2, 3, 4 and A output LCD power supply Use at  $V_{DD5} \ge V_{LC1}$ External supply voltage is input from V<sub>LC1</sub>, V<sub>LC2</sub>, V<sub>LC3</sub> pins or voltage applied to V<sub>LC1</sub> is divided by internal resistance and supplied to  $V_{LC2}$  and  $V_{LC3}$  pins •DAC for audio reproduction Analog DAC input PWM digital output Continuous reproduction function Repeat function (phrase repeat) Volume control (2048 tone) Sampling frequency: 8 to 44.1 kHz Port I/O ports : 85 pins LED (large current) driver pins : 8 pins LCD driver for segment : 55 pins LCD driver for common : 4 pins : 34 pins serial interface pin : 28 pins Timer I/O Buzzer output : 4 pins : 12 pins A/D input : 5 pins External interrupt pin

LCD power : 3 pins XI/XO : 2 pins D/A output : 4 pins Audio output : 2 pins Special pins : 10 pins Operation mode input pins : 3 pin Analog reference voltage input pins: : 1 pin Reset input pin : 1 pin Oscillation pins : 2 pins Power pins : 6 pins

8

# 3.Pin Description

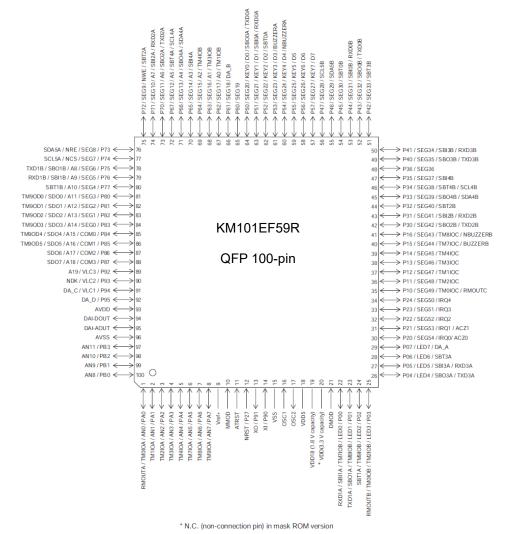

#### 3.1 Pin configuration

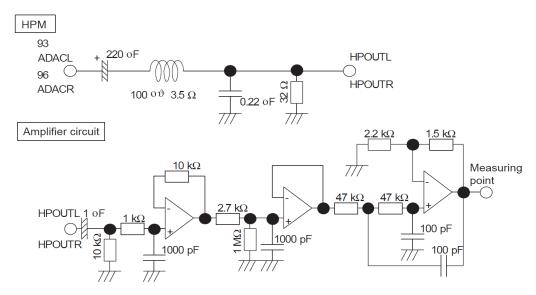

Figure: 3.1 Pin Configuration

### 3.2 Pin Functions

Table: 3.1 Pin Functions

| Name                                                 | Pin No                                 | I/O             | Function                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------|----------------------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS<br>VDD5<br>AVDD<br>AVSS                          | 15<br>18<br>93<br>96                   | -               | Power connect pins                    | Supply 2.2 V to 5.5 V to VDD5, 5.0 V to AVDD and 0 V to VSS and AVSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD18<br>(Capacity<br>1.8 V)                         | 19                                     | -               | Capacity connect pins                 | For internal power circuit output stability, connect at least one bypass capacitor of 1 $\mu\text{F}$ or larger between VDD18 and VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDD<br>(Capacity<br>3.3 V)                           | 20                                     | -               | Capacity connect pins                 | For internal power circuit output stability, connect at least one bypass capacitor of 1 µF or larger between VDD and VSS. (Only Flash version)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

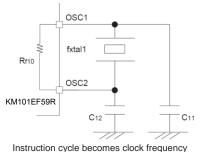

| OSC1<br>OSC2                                         | 16<br>17                               | Input<br>Output | Clock input pins<br>Clock output pins | Connect these oscillation pins to ceramic or crystal oscillators for high-frequency clock operation.  If the clock is an external input, connect it to OSC1 and leave OSC2 open. The chip will not operate with an external clock when using either the STOP or SLOW modes.                                                                                                                                                                                                                                                                                                                                                                             |

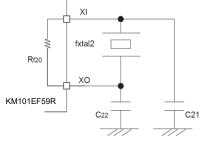

| XI<br>XO                                             | 14<br>13                               | Input<br>Output | Clock input pins<br>Clock output pins | Connect these oscillation pins to crystal oscillators for low-frequency clock operation.  If the clock is an external input, connect it to XI and leave XO open. the chip will not operate with an external clock when using the STOP mode. If these pins are not used, connect XI to VSS and leave XO open.                                                                                                                                                                                                                                                                                                                                            |

| NRST                                                 | 12                                     | Input           | Reset pin [Active low]                | This pin resets the chip when power is turned on, is allocated as P27 and contains an internal pull-up resistor (Type. 50 k $\Omega$ ). Setting this pin low initialize the internal state of the device. Thereafter, setting the input to high releases the reset. The hardware waits for the system clock to stabilize, then processes the reset interrupt. Also, if "0" is written to P27 and the reset is initiated by software, a low level will be output. The output has an n-channel open-drain configuration. If a capacitor is to be inserted between NRST and VSS, it is recommended that a discharge diode be placed between NRST and VDD5. |

| ATRST                                                | 11                                     | Input           | Auto reset setting pins 2             | Input "H" to enable auto reset function and "L" to disable this function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P00<br>P01<br>P02<br>P03<br>P04<br>P05<br>P06<br>P07 | 22<br>23<br>24<br>25<br>26<br>27<br>28 | I/O             | I/O port0                             | 8-bit CMOS tri-state I/O port. Each bit can be set individually as either an input or output by the P0DIR register. A pull-up /pull-down resistor for each bit can be selected individually by the P0PLUD register. A pull-up/down resistor connection for each port can be selected individually by the SELUD register. (However, pull-up and pull-down resistors cannot be mixed.) Direct LED drive available at output. At reset, the input mode is selected and pull-up resistors are disabled (high                                                                                                                                                |

| Name       | Pin No   | I/O   | Function    | Description                                                                                                                                                           |

|------------|----------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P10<br>P11 | 35<br>36 | I/O   | I/O port1   | 7-bit CMOS tri-state I/O port. Each bit can be set individually as either an input or output by the P1DIR register. A pull-up /pull-down resistor for each bit can be |

| P12        | 37       |       |             | selected individually by the P1PLUD register.                                                                                                                         |

| P13        | 38       |       |             | A pull-up/down resistor connection for each port can be selected                                                                                                      |

| P14        | 39       |       |             | individually by the SELUD register. A pull-up/pull down can not be mixed. At reset, the input mode is selected and pull-up resistors                                  |

| P15        | 40       |       |             | are disabled (high impedance).                                                                                                                                        |

| P16        | 41       |       |             |                                                                                                                                                                       |

| P20        | 30       | I/O   | I/O port2   | 5-bit CMOS tri-state I/O port.                                                                                                                                        |

| P21        | 31       |       |             | Each bit can be set individually as either an input or output by the P2DIR register. A pull-up /pull-down resistor for each bit can be                                |

| P22        | 32       |       |             | selected individually by the P2PLUD register.                                                                                                                         |

| P23        | 33       |       |             | A pull-up/down resistor connection for each port can be selected                                                                                                      |

| P24        | 34       |       |             | individually by the SELUD register. (A pull-up/pull down can not be mixed.) At reset, the input mode is selected and pull-up resistors are disabled (high impedance)  |

| P27        | 12       | Input | Input port2 | Port P27 has an N-channel open-drain configuration. When "0" is written and the reset is initiated by software, a low level will be output.                           |

| P30        | 42       | I/O   | I/O port3   | 7-bit CMOS tri-state I/O port.                                                                                                                                        |

| P31        | 43       |       |             | Each bit can be set individually as either an input or output by the                                                                                                  |

| P32        | 44       |       |             | P3DIR register. A pull-up /pull-down resistor for each bit can be selected individually by the P3PLUD register.                                                       |

| P33        | 45       |       |             | A pull-up/down resistor connection for each port can be selected                                                                                                      |

| P34        | 46       |       |             | individually by the SELUD register. (A pull-up/pull down can not be mixed.) At reset, the input mode is selected and pull-up resistors                                |

| P35        | 47       |       |             | are disabled (high impedance)                                                                                                                                         |

| P36        | 48       |       |             |                                                                                                                                                                       |

| P40        | 49       | I/O   | I/O port4   | 8-bit CMOS tri-state I/O port.                                                                                                                                        |

| P41        | 50       |       |             | Each bit can be set individually as either an input or output by the P4DIR register. A pull-up /pull-down resistor for each bit can be                                |

| P42        | 51       |       |             | selected individually by the P4PLUD register.                                                                                                                         |

| P43        | 52       |       |             | A pull-up/down resistor connection for each port can be selected                                                                                                      |

| P44        | 53       |       |             | individually by the SELUD register. A pullup/pull down can not be mixed. At reset, the input mode is selected and pull-up resistors                                   |

| P45        | 54       |       |             | are disabled (high impedance)                                                                                                                                         |

| P46        | 55       |       |             |                                                                                                                                                                       |

| P47        | 56       |       |             |                                                                                                                                                                       |

| P50        | 64       | I/O   | I/O port5   | 8-bit CMOS tri-state I/O port.                                                                                                                                        |

| P51        | 63       |       |             | Each bit can be set individually as either an input or output by the                                                                                                  |

| P52        | 62       |       |             | P5DIR register. A pull-up /pull-down resistor for each bit can be selected individually by the P5PLUD register.                                                       |

| P53        | 61       |       |             | A pull-up/down resistor connection for each port can be selected                                                                                                      |

| P54        | 60       |       |             | individually by the SELUD register. (A pull-up/pull down can not be mixed.) At reset, the input mode is selected and pull-up resistors                                |

| P55        | 59       |       |             | are disabled (high impedance)                                                                                                                                         |

| P56        | 58       |       |             |                                                                                                                                                                       |

| P57        | 57       |       |             |                                                                                                                                                                       |

| Name     | Pin No | I/O | Function          | Description                                                                                                                            |

|----------|--------|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| P60      | 65     | I/O | I/O port6         | 8-bit CMOS tri-state I/O port.                                                                                                         |

| P61      | 66     |     |                   | Each bit can be set individually as either an input or output by the P6DIR register. A pull-up /pull-down resistor for each bit can be |

| P62      | 67     |     |                   | selected individually by the P6PLUD register.                                                                                          |

| P63      | 68     |     |                   | A pull-up/down resistor connection for each port can be selected                                                                       |

| P64      | 69     |     |                   | individually by the SELUD register. (A pull-up/pull down can not be mixed.) At reset, the input mode is selected and pull-up resistors |

| P65      | 70     |     |                   | are disabled (high impedance)                                                                                                          |

| P66      | 71     |     |                   |                                                                                                                                        |

| P67      | 72     |     |                   |                                                                                                                                        |

| P70      | 73     | I/O | I/O port7         | 8-bit CMOS tri-state I/O port.                                                                                                         |

| P71      | 74     |     |                   | Each bit can be set individually as either an input or output by the                                                                   |

| P72      | 75     |     |                   | P7DIR register. A pull-up /pull-down resistor for each bit can be selected individually by the P7PLUD register.                        |

| P73      | 76     |     |                   | A pull-up/down resistor connection for each port can be selected                                                                       |

| P74      | 77     |     |                   | individually by the SELUD register. (A pull-up/pull down can not be mixed.) At reset, the input mode is selected and pull-up resistors |

| P75      | 78     |     |                   | are disabled (high impedance)                                                                                                          |

| P76      | 79     |     |                   |                                                                                                                                        |

| P77      | 80     |     |                   |                                                                                                                                        |

| P80      | 81     | I/O | I/O port8         | 8-bit CMOS tri-state I/O port.                                                                                                         |

| P81      | 82     |     |                   | Each bit can be set individually as either an input or output by the                                                                   |

| P82      | 83     |     |                   | P8DIR register. A pull-up resistor for each bit can be selected individually by the P8PLUD register.                                   |

| P83      | 84     |     |                   | At reset, the input mode is selected and pull-up resistors are                                                                         |

| P84      | 85     |     |                   | disabled (high impedance)                                                                                                              |

| P85      | 86     |     |                   |                                                                                                                                        |

| P86      | 87     |     |                   |                                                                                                                                        |

| P87      | 88     |     |                   |                                                                                                                                        |

| P90      | 14     | I/O | I/O port9         | 7-bit CMOS tri-state I/O port.                                                                                                         |

| P91      | 13     |     |                   | Each bit can be set individually as either an input or output by the                                                                   |

| P92      | 89     |     |                   | P9DIR register. A pull-up resistor for each bit can be selected individually by the P8PLUD register.                                   |

| P93      | 90     |     |                   | At reset, the input mode is selected and pull-up resistors are                                                                         |

| P94      | 91     |     |                   | disabled (high impedance)                                                                                                              |

| P95      | 92     |     |                   |                                                                                                                                        |

| PA0      | 1      | I/O | I/O portA         | 8-bit CMOS tri-state I/O port.                                                                                                         |

| PA1      | 2      |     |                   | Each bit can be set individually as either an input or output by the                                                                   |

| PA2      | 3      |     |                   | PADIR register. A pull-up resistor for each bit can be selected individually by the PAPLUD register.                                   |

| PA3      | 4      |     |                   | At reset, the input mode is selected and pull-up resistors are                                                                         |

| PA4      | 5      |     |                   | disabled (high impedance)                                                                                                              |

| PA5      | 6      |     |                   |                                                                                                                                        |

| PA6      | 7      |     |                   |                                                                                                                                        |

| PA7      | 8      |     |                   |                                                                                                                                        |

| PB0      | 100    | I/O | I/O portB         | 8-bit CMOS tri-state I/O port.                                                                                                         |

| PB1      | 99     |     |                   | Each bit can be set individually as either an input or output by the                                                                   |

| PB2      | 98     |     |                   | PBDIR register. A pull-up resistor for each bit can be selected individually by the PBPLUD register.                                   |

| PB3      | 97     |     |                   | At reset, the input mode is selected and pull-up resistors are disabled (high impedance)                                               |

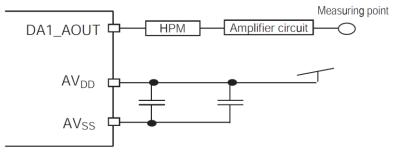

| DA1_DOUT | 94     | I/O | Audio output pins | Special output pins for audio production function                                                                                      |

| DA1_AOUT | 95     |     |                   | These output "L" at reset.                                                                                                             |

| Name  | Pin No | I/O    | Function                        | Description                                                                                                           |

|-------|--------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| SBO0A | 64     | I/O    | Serial interface transmission   | Transmission data output pins for serial interface 0 to 4.                                                            |

| SBO0B | 52     |        | data output pins                | The output configuration, either CMOS push-pull or n-channel open-drain can be selected with the POODC, P3ODC, P4ODC, |

| SBO1A | 23     |        |                                 | P5ODC, P6ODC, P7ODC registers.                                                                                        |

| SBO1B | 78     |        |                                 | Pull-up resistor can be selected by the POPLUD, P3PLUD,                                                               |

| SBO2A | 73     |        |                                 | P4PLUD, P5PLUD, P6PLUD and P7PLUD registers. Select the output mode at the P0DIR, P3DIR, P4DIR, P5DIR, P6DIR and      |

| SBO2B | 42     |        |                                 | P7DIR registers and serial data output mode by serial mode                                                            |

| SBO3A | 26     |        |                                 | register 1 (SC0MD1 to SC4MD1).                                                                                        |

| SBO3B | 49     |        |                                 | These can be used as normal I/O pins when the serial interface is not used.                                           |

| SBO4A | 71     |        |                                 |                                                                                                                       |

| SBO4B | 45     |        |                                 |                                                                                                                       |

| SBI0A | 63     |        | Serial interface reception data | Reception data output pins for serial interface 0 to 4.                                                               |

| SBI0B | 53     |        | input pins                      | A pull-up resistor can be selected with the P0ODC, P3ODC,                                                             |

| SBI1A | 22     |        |                                 | P4ODC, P5ODC, P6ODC, P7ODC registers. Select the output mode at the P0DIR, P3DIR, P4DIR, P5DIR,                       |

| SBI1B | 79     |        |                                 | P6DIR and P7DIR registers and serial data output mode by serial                                                       |

| SBI2A | 74     |        |                                 | mode register 1 (SC0MD1 to SC4MD1). These can be used as normal I/O pins when the serial interface is                 |

| SBI2B | 43     |        |                                 | not used.                                                                                                             |

| SBI3A | 27     |        |                                 |                                                                                                                       |

| SBI3B | 50     |        |                                 |                                                                                                                       |

| SBI4A | 70     |        |                                 |                                                                                                                       |

| SBI4B | 47     |        |                                 |                                                                                                                       |

| SBT0A | 62     | I/O    | Serial interface clock I/O pins | Clock I/O pins for serial interface 0 to 4.                                                                           |

| SBT0B | 54     |        | ·                               | The output configuration, either CMOS push-pull or n-channel                                                          |

| SBT1A | 24     |        |                                 | open-drain can be selected with the POODC, P3ODC, P4ODC, P5ODC, P6ODC, P7ODC registers.                               |

| SBT1B | 80     |        |                                 | Pull-up resistor can be selected by the P0PLUD, P3PLUD,                                                               |

| SBT2A | 75     |        |                                 | P4PLUD, P5PLUD, P6PLUD and P7PLUD registers. Select the                                                               |

| SBT2B | 44     |        |                                 | clock I/O with the P0DIR, P3DIR, P4DIR, P5DIR, P6DIR and P7DIR registers and serial data output mode by serial mode   |

| SBT3A | 28     |        |                                 | register 1 (SC0MD1 to SC4MD1) according to the communication.                                                         |

| SBT3B | 51     |        |                                 | These can be used as normal I/O pins when the serial interface is not used.                                           |

| SBT4A | 72     |        |                                 | not used.                                                                                                             |

| SBT4B | 46     |        |                                 |                                                                                                                       |

| TXD0A | 64     | Output | UART transmission data output   | In the serial interface0 to 3 in UART mode, this pin is configured as                                                 |

| TXD0B | 52     |        | pins                            | the transmission data output pin.                                                                                     |

| TXD1A | 23     |        |                                 | The output configuration, either CMOS push-pull or n-channel open-drain can be selected with the POODC, P3ODC, P4ODC, |

| TXD1B | 78     |        |                                 | P5ODC, P7ODC registers.                                                                                               |

| TXD2A | 73     |        |                                 | Pull-up resistor can be selected by the POPLUD, P3PLUD,                                                               |

| TXD2B | 42     |        |                                 | P4PLUD, P5PLUD and P7PLUD registers. Select the output mode at the P0DIR, P3DIR, P4DIR, P5DIR and P7DIR registers and |

| TXD3A | 26     |        |                                 | serial data output mode by serial mode register 1 (SC0MD1 to                                                          |

| TXD3B | 49     |        |                                 | SC3MD1). These can be used as normal I/O pins when the serial interface is                                            |

|       |        |        |                                 | not used.                                                                                                             |

| RXD0A | 63     | Input  | UART reception                  | In the serial interface0 to 3 in UART mode, this pin is configured as                                                 |

| RXD0B | 53     | ·      | data input pins                 | the reception data output pin.                                                                                        |

| RXD1A | 22     |        |                                 | Pull-up resistor can be selected by the P0PLUD, P3PLUD, P4PLUD, P5PLUD and P7PLUD registers.                          |

| RXD1B | 79     |        |                                 | Select the output mode at the P0DIR, P3DIR, P4DIR, P5DIR and                                                          |

| RXD2A | 74     |        |                                 | P7DIR registers and serial data output mode by serial mode                                                            |

| RXD2B | 43     |        |                                 | register 1 (SC0MD1 to SC3MD1). These can be used as normal I/O pins when the serial interface is                      |

| RXD3A | 27     |        |                                 | not used.                                                                                                             |

|       |        |        |                                 |                                                                                                                       |

| Name                                                                                                            | Pin No                                  | I/O | Function                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA4A<br>SDA4B<br>SDA5A<br>SDA5B                                                                                | 71<br>45<br>76<br>55                    | I/O | IIC data I/O pins                              | In the serial interface4, 5 in IIC mode, this pin is configured as the data input / output pin.  For the output configuration, select n-channel open-drain with the P3ODC, P4ODC, P6ODC and P7ODC registers and pull-up resistors by the P3PLUD, P4PLUD, P6PLUD and P7PLUD registers. Select the output mode at the P3DIR, P4DIR, P6DIR and P7DIR registers and serial data input / output mode by serial mode register 1 (SC4MD1, SC5MD1).  These can be used as normal I/O pins when the serial interface is not used.                                                                                                                                                                                                                                    |

| SCL4A<br>SCL4B<br>SCL5A<br>SCL5B                                                                                | 72<br>46<br>77<br>56                    |     | IIC clock I/O pins                             | In the serial interface4, 5 in IIC mode, this pin is configured as the clock input / output pin. For the output configuration, select n-channel open-drain with the P3ODC, P4ODC, P6ODC and P7ODC registers and pull-up resistors by the P3PLUD, P4PLUD, P6PLUD and P7PLUD registers. Select the output mode at the P3DIR, P4DIR, P6DIR and P7DIR registers and serial data input / output mode by serial mode register 1 (SC4MD1, SC5MD1). These can be used as normal I/O pins when the serial interface is not used                                                                                                                                                                                                                                      |

| TMOIOA TMOIOB TMOIOC TM1IOA TM1IOB TM1IOC TM2IOA TM2IOB TM2IOC TM3IOA TM3IOC TM3IOB TM3IOC TM4IOA TM4IOB TM4IOA | 1 25 35 2 67 37 3 25 36 4 68 38 5 69 39 | I/O | Timer I/O pins                                 | Event counter clock input pin, timer output and PWM signal output pin for 8-bit timer 0 to 4.  To use this pin as event clock input, configure this as input by P0DIR register, P1DIR register, P6DIR register and PADIR register. In the input mode, pull-up resistors can be selected by the P0PLUD register, P1PLUD register, P6PLUD register and PAPLU register.  For timer output, PWM signal output, select the special function pin by port 0 output mode register, port 1 output mode register, port 6 output mode register and port A output mode register ((P0OMD, P1OMD, P6OMD and PAOMD), and set to the output mode at P0DIR register, P1DIR register and PADIR register. These can be used as normal I/O pins when the timer I/O is not used. |

| RMOUTA<br>RMOUTB<br>RMOUTC                                                                                      | 1<br>25<br>35                           | I/O | Remote control transmission signal output pins | Output pin for remote control transmission with a carrier signal. For remote control carrier output, select the special function pin by the port 0 output mode register, port 1 output mode register and port A output mode register (P0OMD, P1OMD and PAOMD), and set to the output mode by the P0DIR register, P1DIR register and PADIR register.  At the same time, select remote control carrier output by the remote control carrier output register.  These can be used as normal I/O pins when the buzzer output is not used.                                                                                                                                                                                                                        |

| BUZZERA<br>BUZZERB<br>NBUZZERA<br>NBUZZERB                                                                      | 61<br>40<br>60<br>41                    | I/O | Buzzer output                                  | Piezoelectric buzzer driving pin. Buzzer output available to port1, port5.  The driving frequency can be selected with the DLYCTR register. To select buzzer output for porrt1, port5, select the special function pin by the port 1 output mode register and port 5 output mode register (P1OMD and P5OMD), and set to the output mode by the P1DIR register and P5DIR register.  At the same time, select buzzer output by the oscillation stabilization wait control register (DLYCTR).  These can be used as normal I/O pins when the buzzer output is not used.                                                                                                                                                                                        |

| Name   | Pin No | I/O    | Function                         | Description                                                                                                                                                                                                                                                                            |

|--------|--------|--------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TM7IOA | 6      | I/O    | Timer I/O pins                   | Event counter clock input pin, timer output and PWM signal output                                                                                                                                                                                                                      |

| TM7IOB | 22     |        |                                  | pin for 16-bit timer7 and 8.  To use this pin as event clock input, configure this as input with the                                                                                                                                                                                   |

| TM7IOC | 40     |        |                                  | PADIR register. In the input mode, pull-up resistors can be                                                                                                                                                                                                                            |

| AOI8MT | 7      |        |                                  | selected by P0PLU register, P1PLU register and PAPLU register.                                                                                                                                                                                                                         |

| TM8IOB | 23     |        |                                  | For timer output, PWM signal output, select the special function pin<br>by the port 0 output mode register, port 1 output mode register and                                                                                                                                            |

| TM8IOC | 41     |        |                                  | port A output mode register (P0OMD, P1OMD and PAOMD), and                                                                                                                                                                                                                              |

| TM9IOA | 8      |        |                                  | set to the output mode at P0DIR register, P1DIR register and PADIR register.                                                                                                                                                                                                           |

| TM9IOB | 24     |        |                                  | These can be used as normal I/O pins when not used                                                                                                                                                                                                                                     |

| TM9OD0 | 81     | Output | Timer output pins                | Timer output and PWM signal output pin for 16-bit timer.                                                                                                                                                                                                                               |

| TM9OD1 | 82     |        |                                  | To select timer output and PWM signal output, select the special function pin by the P8PLU register, and set to the output mode at                                                                                                                                                     |

| TM9OD2 | 83     |        |                                  | the P8DIR register.                                                                                                                                                                                                                                                                    |

| TM9OD3 | 84     |        |                                  | These can be used as normal I/O pins when not used as timer I/O                                                                                                                                                                                                                        |

| TM9OD4 | 85     |        |                                  | pins.                                                                                                                                                                                                                                                                                  |

| TM9OD5 | 86     |        |                                  |                                                                                                                                                                                                                                                                                        |

| SDO0   | 81     | Output | Synchronous output pins          | 8-bit synchronous output pins.                                                                                                                                                                                                                                                         |

| SDO1   | 82     |        |                                  | Synchronous output for each bit can be selected individually by the port 8 synchronous output control register (P8SYO). Set to the                                                                                                                                                     |

| SDO2   | 83     |        |                                  | output mode by the P8DIR register.                                                                                                                                                                                                                                                     |

| SDO3   | 84     |        |                                  | These pins can be used as a normal I/O pins when not used for synchronous output pin.                                                                                                                                                                                                  |

| SDO4   | 85     |        |                                  | Synchronous output pin.                                                                                                                                                                                                                                                                |

| SDO5   | 86     |        |                                  |                                                                                                                                                                                                                                                                                        |

| SDO6   | 87     |        |                                  |                                                                                                                                                                                                                                                                                        |

| SDO7   | 88     |        |                                  |                                                                                                                                                                                                                                                                                        |

| VREF+  | 100    | -      | + power supply for A/D converter | Reference power supply pins for the A/D converter. Use this under the condition: 2.0 V $\leq$ VREF+ $\leq$ VDD5                                                                                                                                                                        |

| AN0    | 1      | Input  | Analog input pins                | Analog input pins for an 16-channel, 10-bit A/D converter.                                                                                                                                                                                                                             |

| AN1    | 2      |        |                                  | When not used for analog input, these pins can be used as normal input pins.                                                                                                                                                                                                           |

| AN2    | 3      |        |                                  | imput pino.                                                                                                                                                                                                                                                                            |

| AN3    | 4      |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN4    | 5      |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN5    | 6      |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN6    | 7      |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN7    | 8      |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN8    | 100    |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN9    | 99     |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN10   | 98     |        |                                  |                                                                                                                                                                                                                                                                                        |

| AN11   | 97     |        |                                  |                                                                                                                                                                                                                                                                                        |

| DA_A   | 29     | Output | Analog output pins               | Analog output pins for an 4-channel, 8-bit A/D converter.                                                                                                                                                                                                                              |

| DA_B   | 66     |        |                                  | When not used for analog output, these pins can be used as normal I/O pins.                                                                                                                                                                                                            |

| DA_C   | 91     |        |                                  |                                                                                                                                                                                                                                                                                        |

| DA_D   | 92     |        |                                  |                                                                                                                                                                                                                                                                                        |

| IRQ0   | 30     | Input  | External interrupt input pins    | External interrupt input pins. The valid edge for IRQ0 to 4 can be selected with the IRQnICR                                                                                                                                                                                           |

| IRQ1   | 31     |        |                                  | register.                                                                                                                                                                                                                                                                              |

| IRQ2   | 32     |        |                                  | IRQ1 has AC zero-cross detection function. IRQ1 can be set at                                                                                                                                                                                                                          |

| IRQ3   | 33     |        |                                  | both edges at pin voltage level.  When not used for interrupts, these can be used as normal input                                                                                                                                                                                      |

| IRQ4   | 34     |        |                                  | pins.                                                                                                                                                                                                                                                                                  |

| ACZ1   | 31     | Input  | AC zero-cross detection input    | AC zero-cross detection input pin.                                                                                                                                                                                                                                                     |

| ACZ0   | 30     |        | pins                             | AC zero-cross detection output "H" when input level is mid-level and "L" otherwise.  ACZ input signal is connected to P20 input and IRQ0 interrupt circuit or P21 input and IRQ1 interrupt circuit. When not used for AC zero-cross detection, these can be used as normal input pins. |

| Name         | Pin No   | I/O    | Function                           | Description                                                                                                                                                                                                                                                                                                              |

|--------------|----------|--------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACZ1<br>ACZ0 | 31<br>30 | Input  | AC zero-cross detection input pins | AC zero-cross detection input pin. AC zero-cross detection output "H" when input level is mid-level and "L" otherwise. ACZ input signal is connected to P20 input and IRQ0 interrupt circuit or P21 input and IRQ1 interrupt circuit. When not used for AC zero-cross detection, these can be used as normal input pins. |

| KEY0         | 64       | Input  | Key interrupt input pins           | Input pins for interrupt based on OR result of pin                                                                                                                                                                                                                                                                       |

| KEY1         | 63       |        |                                    | inputs. These can be set to key input pins by 1-bit with the key interrupt                                                                                                                                                                                                                                               |

| KEY2         | 62       |        |                                    | control register (KEYT3_1IMD, KEYT3_2IMD) and by 2-bit with the                                                                                                                                                                                                                                                          |

| KEY3         | 61       |        |                                    | key interrupt control register (KEYT3_1IMD). When not used for KEY input, these pins can be used                                                                                                                                                                                                                         |

| KEY4         | 60       |        |                                    | as normal I/O pins.                                                                                                                                                                                                                                                                                                      |

| KEY5         | 59       |        |                                    | ·                                                                                                                                                                                                                                                                                                                        |

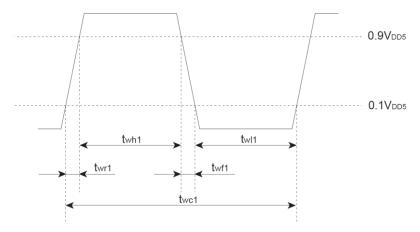

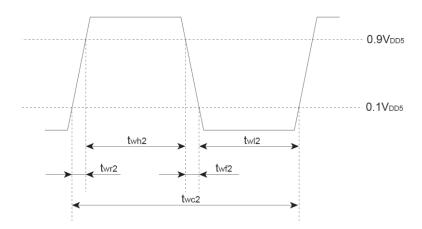

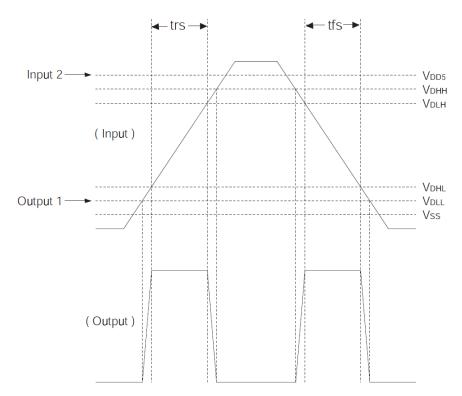

| KEY6         | 58       |        |                                    |                                                                                                                                                                                                                                                                                                                          |