#### 8-bit Microcontroller

# KM101EF56K/57G/76K Series Datasheet

The information described in this Datasheet is the exclusive intellectual property of Nuvoton Technology Corporation Japan and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing document only for reference purposes of KM101EF56K/57G/76K Series based system design. Nuvoton assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

For additional information or question, please contact Nuvoton Technology Corporation Japan. www.nuvoton.co.jp

#### 1. Overview

#### 1.1 Overview

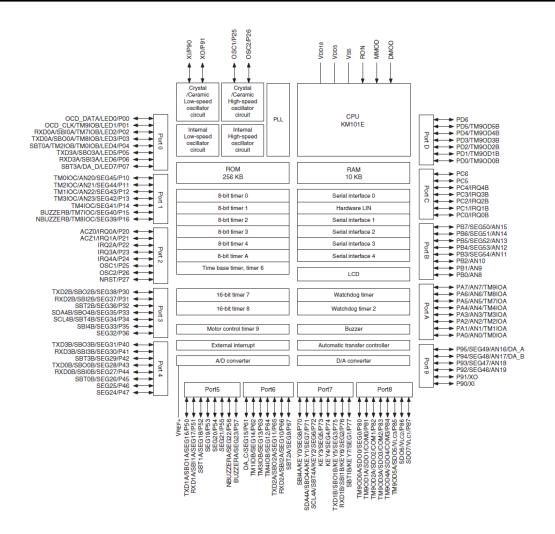

The KM101E series of 8-bit single-chip microcontrollers incorporate multiple types of peripheral functions. This chip series is well suited for camera, VCR, MD, TV, CD, LD, printer, telephone, home automation, pager, air conditioner, PPC, fax machine, music instrument and other applications.

This LSI brings to embedded microcontroller applications flexible, optimized hardware configurations and a simple efficient instruction set. KM101EF57 series has an internal 128 KB of ROM and 6 KB of RAM. Peripheral functions include 5 external interrupts, 29 internal interrupts including NMI, 12 timer counters, 4 types of serial interfaces, A/D converter, D/A converter, LCD driver, 2 types of watchdog timer, data automatic function and buzzer output. The system configuration is suitable for in camera, timer selector for VCR, CD player, or mini-component.

With 5 oscillation systems (high-speed (internal frequency: 20 MHz), high-speed (crystal/ceramic frequency: max. 10 MHz) / low-speed (internal frequency: 30 kHz), low-speed (crystal/ceramic frequency: 32.768 kHz) and PLL: frequency multiplier of high frequency) contained on the chip, the system clock can be switched to high-speed frequency input (NORMAL mode), PLL input (PLL mode), or to low-speed frequency input (SLOW mode). The system clock is generated by dividing the oscillation clock or PLL clock. The best operation clock for the system can be selected by switching its frequency ratio by programming. High speed mode has the normal mode which is based on the clock dividing fpll, (fpll is generated by original oscillation and PLL), by 2 (fpll/2), and the double speed mode which is based on the clock not dividing fpll.

A machine cycle (minimum instruction execution time) in the normal mode is 200 ns when the original oscillation fosc is 10 MHz (PLL is not used). A machine cycle in the double speed mode, in which the CPU operates on the same clock as the external clock, is 100 ns when fosc is 10 MHz. A machine cycle in the PLL mode is 50 ns (maximum).

#### 1.2 Product Summary

This datasheet describes the following model.

| Model      | ROM Size | RAM Size | Classification       | Package                    |

|------------|----------|----------|----------------------|----------------------------|

| KM101EF76K | 256 KB   | 10 KB    | Flash EEPROM version | LQFP 128-pin               |

| KM101EF57G | 128 KB   | 6 KB     | Flash EEPROM version | LQFP 80-pin<br>TQFP 80-pin |

| KM101EF56K | 256 KB   | 10 KB    | Flash EEPROM version | QFP 100-pin                |

Table: 1.1 Product Summary

### 2. Hardware Functions

| • ROM / RAM capacity     | KM101EF76K: ROM 256 KB / RAM 10 KB<br>KM101EF57G: ROM 128 KB / RAM 6 KB<br>KM101EF56K: ROM 256 KB / RAM 10 KB                                                                                                                                                                                                 |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

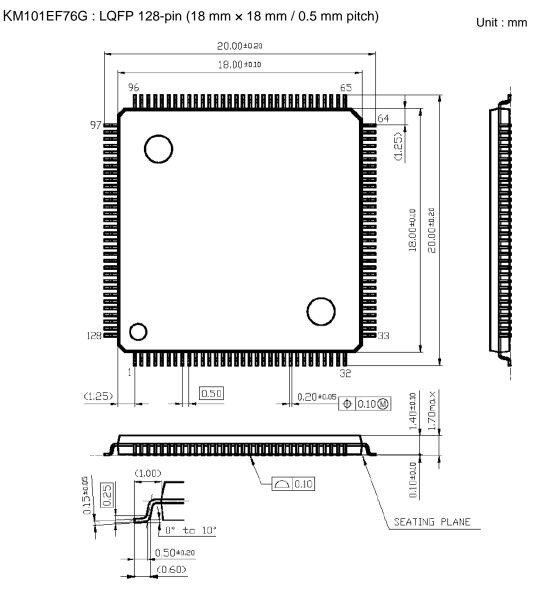

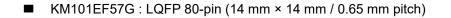

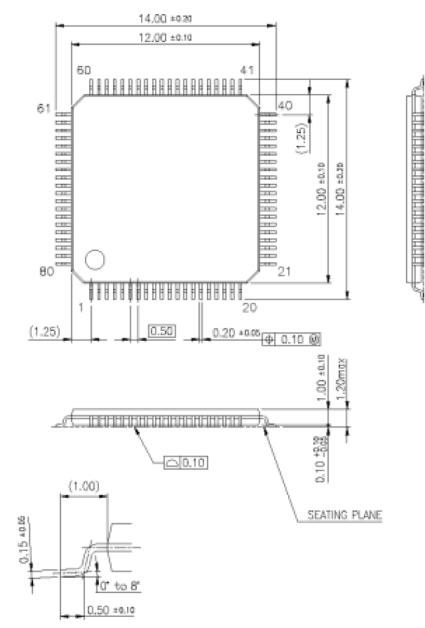

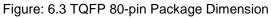

| • Package:               | KM101EF76K: LQFP 128-pin (18 mm × 18 mm / 0.5 mm pitch)<br>KM101EF57G: LQFP 80-pin (14 mm × 14 mm / 0.65 mm pitch)<br>TQFP 80-pin (12 mm × 12 mm / 0.5 mm pitch)<br>KM101EF56K: QFP 100-pin (18 mm × 18 mm / 0.65 mm pitch)                                                                                   |

| Machine Cycle            | High-speed mode<br>0.05 µs/20 MHz (2.7 V to 5.5 V)<br>0.125 µs/8 MHz (1.8 V to 5.5 V)<br>Low-speed mode<br>62.5 µs/ 32 kHz (1.8 V to 5.5 V)                                                                                                                                                                   |

| Clock Gear Circuit       | Internal system clock speed is changeable by selecting division ratio of oscillation clock. (Divided by 1, 2, 4, 16, 32, 64, 128)                                                                                                                                                                             |

| Oscillation Circuit      | 4 types<br>High-speed (Internal oscillation: frc), High-speed (crystal/ceramic: fosc),<br>Low-speed (Internal oscillation: frcs), Low-speed (crystal/ceramic: fx)<br>High-speed internal oscillation 20 MHz / 16 MHz (selectable)<br>Low-speed internal oscillation 30 kHz                                    |

| • Clock Multiplication G | Circuit                                                                                                                                                                                                                                                                                                       |

|                          | PLL circuit output clock (fpll) fosc multiplied by 2, 3, 4, 5, 6, 8, 10,<br>1/2 × frc multiplied by 4, 5 enabled<br>* When clock multiplication circuit is not used, fpll = fosc or fpll = frc<br>* Selectable from high-speed clock for peripheral functions (fpll-div) fpll, fpll divided by<br>2, 4, 8, 16 |

| • Memory bank            | Data memory space is expanded by the bank system.<br>Bank for the source address / Bank for the destination address.                                                                                                                                                                                          |

| • Operation Mode         | NORMAL mode (high-speed mode)<br>PLL mode<br>SLOW mode (low-speed mode)<br>HALT mode<br>STOP mode<br>and operation clock switching                                                                                                                                                                            |

| • Operating Voltage      | 1.8 V to 5.5 V                                                                                                                                                                                                                                                                                                |

• Operation ambient temperature

-40 °C to +85 °C

#### • Interrupt

| Interrupt                                                                                | KM101EF76K<br>36 sets | KM101EF57G<br>34 sets | KM101EF56K<br>36 sets |

|------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|

| <overrun interrupt=""></overrun>                                                         |                       |                       |                       |

| Non-maskable interrupt (NMI)                                                             |                       | $\checkmark$          |                       |

| <timer interrupt=""></timer>                                                             |                       |                       |                       |

| Timer 0 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 1 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 2 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 3 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 4 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 6 interrupt                                                                        |                       | $\checkmark$          |                       |

| Timer 7 interrupt                                                                        |                       | $\checkmark$          |                       |

| Time-base interrupt                                                                      |                       | $\checkmark$          |                       |

| Timer 7 compare register 2 match interrupt                                               |                       | $\checkmark$          |                       |

| Timer 8 interrupt                                                                        | √                     |                       |                       |

| Timer 8 compare register 2 match interrupt                                               | √                     |                       |                       |

| PWM overflow interrupt                                                                   | √<br>√                | <u>الم</u>            |                       |

| PWM under flow interrupt                                                                 | <u>الا</u>            |                       | 1                     |

| Timer 9 compare register 2 match interrupt                                               | <u>الم</u>            |                       |                       |

| 24H timer interrupt                                                                      | <u>الم</u>            |                       | <u>ا</u>              |

| Alarm match interrupt                                                                    | N                     | V                     |                       |

| <serial interrupt=""></serial>                                                           | ,                     | ,                     | ,                     |

| LIN interrupt                                                                            | ν                     | √                     |                       |

| Serial 0 interrupt                                                                       |                       |                       |                       |

| Serial 0 UART reception interrupt                                                        |                       |                       |                       |

| Serial 1 interrupt                                                                       |                       |                       |                       |

| Serial 1 UART reception interrupt                                                        |                       |                       |                       |

| Serial 2 interrupt                                                                       |                       | V                     |                       |

| Serial 2 UART reception interrupt                                                        |                       |                       |                       |

| Serial 3 interrupt                                                                       |                       | -                     |                       |

| Serial 3 UART reception interrupt                                                        |                       | -                     |                       |

| Serial 4 interrupt                                                                       |                       |                       |                       |

| Serial 4 stop condition interrupt                                                        |                       | V                     |                       |

| <a d="" interrupt=""></a>                                                                | ,                     | ,                     | ,                     |

| A/D conversion interrupt                                                                 |                       | $\checkmark$          |                       |

| <data automatic="" interrupt="" transfer=""></data>                                      |                       |                       |                       |

| ATC1 interrupt                                                                           |                       |                       |                       |

| <low detection="" interrupt="" voltage=""></low>                                         |                       |                       | · · ·                 |

| Low voltage detection interrupt                                                          |                       | $\checkmark$          |                       |

| <external interrupt=""></external>                                                       |                       |                       |                       |

| IRQ0 (Edge selection, noise filter connectable)                                          |                       | $\checkmark$          | $\checkmark$          |

| IRQ1 (Edge selection, noise filter connectable)                                          |                       | $\checkmark$          | $\checkmark$          |

| IRQ2 (Edge selection, both edge interrupt, noise filter connectable)                     | $\checkmark$          | $\checkmark$          | $\checkmark$          |

| IRQ3 (Edge selection, both edge interrupt, noise filter connectable)                     | $\checkmark$          | $\checkmark$          |                       |

| IRQ4 (Edge selection, both edge interrupt, noise filter connectable, KEY scan interrupt) | $\checkmark$          | $\checkmark$          |                       |

- Timer Counter:

- 12 sets

- General-purpose 8-bit timer  $\times$  5 sets

- General-purpose 16-bit timer  $\times$  2 sets

- General-purpose 16-bit timer  $\times$  2 sets

- Motor control 16-bit timer  $\times$  1 set

- 8-bit free-run timer  $\times$  1 set-Time-base timer  $\times$  1 set

- Baud rate timer  $\times$  1 set

- 24H timer  $\times$  1 set

- Timer 0 (General-purpose 8-bit timer)

- Square wave output (Timer pulse output), added pulse (2 bits) type PWM output can be output to large current pin TM0IOB, event count, simple pulse width measurement

- Double-buffered compare register ( $\times$  1) \* Function in KM101EF76K and

- KM101EF56K

- Clock source

- $fpll-div,\,fpll-div/4,\,fpll-div/16,\,fpll-div/32,\,fpll-div/64,\,fpll-div/128,$

- fs/2, fs/4, fs/8, fslow, external clock, timer A output

- Real-time control

Timer (PWM) output is controlled among the three values: "Fixed to High", "Fixed to Low", or "Hi-Z" at falling edge of external interrupt 0 (IRQ0)

- Timer 1 (General-purpose 8-bit timer)

- Square wave output (Timer pulse output), event

- count 16-bit cascade connection (connected with timer 0)

- Double-buffered compare register (× 1) \* Function in KM101EF76K and KM101EF56K

- Clock source

- fpll-div, fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fslow, external clock, timer A output

- Timer 2 (General-purpose 8-bit timer)

- Square wave output (Timer pulse output), added pulse (2 bits) type PWM output can be output to large current pin TM2IOB, event count, simple pulse width measurement, 24-bit cascade connection (connected with timer 0, 1), timer synchronous output

- Double-buffered compare register ( $\times$  1)

- Clock source

- fpll-div, fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128,

- fs/2, fs/4, fs/8, fslow, external clock, timer A output

- Real-time control

Timer (PWM) output is controlled among the three values: "Fixed to High", "Fixed to Low", or "Hi-Z" at falling edge of external interrupt 0 (IRQ0)

- Timer 3 (General-purpose 8-bit timer)

- Square wave output (Timer pulse output), event count

- 16-bit cascade connection (connected with timer 2),

32-bit cascade connection (connected with timer 0, 1, 2)

- Double-buffered compare register ( $\times$  1)

- Clock source

- fpll-div/, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fslow, external clock, timer A output

- Timer 4 (General-purpose 8-bit timer)

- Square wave output (Timer pulse output), added pulse (2bit) type PWM output, event count, simple pulse width measurement

- Clock source

- fpll-div, fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fslow, external clock, timer A output

| • Timer Counter<br>(continued) | Timer 6 (8-bit free-run timer, time-base timer)<br>8-bit free-run timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (continued)                    | <ul> <li>Clock source<br/>fpll-div/2<sup>2</sup>, fpll-div/2<sup>3</sup>, fpll-div/2<sup>12</sup>, fpll-div/2<sup>13</sup>, fs, fslow,<br/>fslow/2<sup>2</sup>, fslow/2<sup>3</sup>, fslow/2<sup>12</sup>, fslow/2<sup>13</sup></li> <li>Time-base timer</li> <li>Interrupt generation cycle<br/>fpll-div/2<sup>7</sup>, fpll-div/2<sup>8</sup>, fpll-div/2<sup>9</sup>, fpll-div/2<sup>10</sup>, fpll-div/2<sup>13</sup>, fpll-div/2<sup>15</sup>,<br/>fslow/2<sup>7</sup>, fslow/2<sup>8</sup>, fslow/2<sup>9</sup>, fslow/2<sup>10</sup>, fslow/2<sup>13</sup>, fslow/2<sup>15</sup></li> </ul>                                                                                                                              |

|                                | <ul> <li>Timer 7 (General-purpose 16-bit timer) <ul> <li>Clock source</li> <li>fpll-div, fs, external clock, timer A output, serial 0 transfer clock output, timer 6 compare match cycle divided by 1, 2, 4, 16</li> <li>Hardware configuration</li> <li>Double-buffered compare register (× 2)</li> <li>Double-buffered input capture register (× 2)</li> <li>Timer interrupt (× 2 vector)</li> </ul> </li> <li>Timer function <ul> <li>Square wave output (Timer pulse output), high-precision PWM output (cycle/duty continuous changeable) can be output to large current pin TM7IOB, timer synchronous output, event count, input capture function (both edges operable)</li> <li>Real-time control</li> </ul> </li> </ul> |

|                                | <ul> <li>Timer (PWM) output is controlled among the three values: "Fixed to High", "Fixed to Low", or "Hi-Z" at falling edge of external interrupt 0 (IRQ0)</li> <li>Timer 8 (General-purpose 16-bit timer) <ul> <li>Clock source</li> <li>fall div. fa avternal clock, timer A output, timer 6 compare metch cycle divided by 1</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                         |

|                                | <ul> <li>fpll-div, fs, external clock, timer A output, timer 6 compare match cycle divided by 1, 2, 4, 16</li> <li>Hardware configuration <ul> <li>Double-buffered compare register (× 2)</li> <li>Double-buffered input capture register (× 1)</li> <li>Timer interrupt (× 2 vector)</li> </ul> </li> <li>Timer function <ul> <li>Square wave output (Timer pulse output), high-precision PWM output (cycle/duty continuous changeable) can be output to large current pin TM8IOB, event count, pulse width measurement, input capture function (both edges operable)</li> </ul> </li> </ul>                                                                                                                                   |

|                                | <ul> <li>32-bit cascade connection (connected with timer 7), 32-bit PWM output, input capture is available in 32-bit cascade</li> <li>Timer 9 (Motor control 16-bit timer)</li> <li>Clock source</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | <ul> <li>clock source</li> <li>fpll-div, fs, external clock, Timer A output divided by 1, 2, 4, 16</li> <li>Hardware configuration</li> <li>Double-buffered compare register (× 2)</li> <li>Timer interrupt (× 3 vector)</li> <li>Timer function</li> <li>Square wave output (Timer pulse output) can be changed to large current output, complementary 3-phase PWM output, triangle wave and saw tooth wave are supported, dead time insertion available, event count</li> <li>Pin output control</li> <li>PWM output control is possible by external interrupt 0 to 4 (IRQ 0 to 4) ("Hi-z", output data fixed)</li> </ul>                                                                                                     |

|                                | <ul> <li>Timer A (baud rate timer)</li> <li>Clock output for peripheral functions</li> <li>Clock source</li> <li>fpll-div divided by 1/1, 2, 4, 8, 16, 32, and fs divided by 2, 4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • Timer Counter<br>(continued) | <ul> <li>24H timer <ul> <li>Clock source (Usable frequency)</li> <li>fpll (4 MHz, 4.19 MHz, 5 MHz, 8 MHz, 8.38 MHz, 10 MHz, 16 MHz, 16,77 MHz, 20 MHz), fx (32.768 kHz), frc (20 MHz, 16 MHz), frcs (30 kHz)</li> <li>Hardware configuration <ul> <li>0.5 seconds counter, minute counter, hour counter</li> <li>Alarm compare register (in 0.5 seconds, in minutes, in hours) (× 1)</li> <li>Timer interrupt (·×2 vector)</li> </ul> </li> <li>Timer function <ul> <li>Interval function (interrupts every 0.5 seconds, 1 second, 1 minute, 1 hour, 24 hours)</li> <li>Alarm function</li> </ul> </li> </ul></li></ul>                                                                                                                                                                                                                                                               |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Watchdog timer               | Overrun detection cycle is selectable from $fs/2^{16}$ , $fs/2^{18}$ , $fs/2^{20}$<br>Forced to reset inside LSI by hardware when a software processing error is detected twice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| • Watchdog timer2              | Overrun detection cycle is selectable from frcs/2 <sup>4</sup> , frcs/2 <sup>5</sup> , frcs/2 <sup>6</sup> , frcs/2 <sup>7</sup> , frcs/2 <sup>8</sup> , frcs/2 <sup>9</sup> , frcs/2 <sup>10</sup> , frcs/2 <sup>11</sup> , frcs/2 <sup>12</sup> , frcs/2 <sup>13</sup> , frcs/2 <sup>14</sup> , frcs/2 <sup>15</sup><br>Forced to reset inside LSI by hardware when a software processing error is detected twice                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| • Synchronous output           | function (Timer synchronous output, interrupt synchronous output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | Latch data is output from port 8 at the event timing of synchronous output signal of timer 1, timer 2, timer 7, or external interrupt2 (IRQ2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Buzzer Output                  | Output frequency can be selected from fpll-div/2 <sup>9</sup> , fpll-div/2 <sup>10</sup> , fpll-div/2 <sup>11</sup> , fpll-div/2 <sup>12</sup> , fpll-div/2 <sup>13</sup> , fpll-div/2 <sup>14</sup> , fslow/2 <sup>3</sup> , fslow/2 <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • A/D converter                | KM101EF76K: 10-bit × 24 channels<br>KM101EF57G: 10-bit × 12 channels<br>KM101EF56K: 10-bit × 24 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| • D/A converter                | KM101EF76K: 8-bit × 4 channels<br>KM101EF57G: 8-bit × 2 channels<br>KM101EF56K: 8-bit × 4 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • Data automatic trans         | sfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                | Data is automatically transferred in all memory space<br>- External interrupt activation/internal event activation/software activation<br>- Max. 255 byte continuous transfer<br>- Serial continuous transmission and reception is supported<br>- Burst transfer function (Including interrupt emergency stop)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| • Serial interface             | KM101EF76K: 5 systems<br>KM101EF57G: 4 systems<br>KM101EF56K: 5 systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                | <ul> <li>Serial interface 0 (Hardware LIN / Full duplex UART / Synchronous serial interface)</li> <li>Synchronous serial interface <ul> <li>Transfer clock source</li> <li>fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4,</li> <li>Timer 0 to 4, Timer A output divided by 1, 2, 4, 8, 16, External clock</li> <li>MSB/LSB first selectable, 1 to 8 bits of arbitrary transfer</li> <li>Continuous transmission, continuous reception, continuous transmission and reception are available.</li> </ul> </li> <li>Full duplex UART (Baud rate timer: selected from timer 0 to 4, or timer A) <ul> <li>Parity check, overrun error/framing error are detected</li> <li>Transfer bits 7 to 8 are selectable</li> <li>Hardware LIN</li> <li>Synch Break generation, Wake-up detection, Synch Break detection, Synch Field measurement are available</li> </ul> </li> </ul> |

| • Serial interface<br>(continued) | <ul> <li>Serial interface 1 (Full duplex UART / Synchronous serial interface)</li> <li>Synchronous serial interface <ul> <li>Transfer clock source</li> <li>fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4,</li> <li>Timer 0 to 4, Timer A output divided by 1, 2, 4, 8, 16, External clock</li> <li>MSB/LSB first selectable, 1 to 8 bits of arbitrary transfer</li> <li>Continuous transmission, continuous reception, continuous transmission and reception are available.</li> </ul> </li> <li>Full duplex UART (Baud rate timer: selected from timer 0 to 4, or timer A) <ul> <li>Parity check, overrun error/framing error are detected</li> <li>Transfer bits 7 to 8 are selectable</li> </ul> </li> </ul>                                                  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | <ul> <li>Serial interface 2 (Full duplex UART / Synchronous serial interface)</li> <li>Synchronous serial interface <ul> <li>Transfer clock source</li> <li>fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4,</li> <li>Timer 0 to 4, Timer A output divided by 1, 2, 4, 8, 16, External clock</li> <li>MSB/LSB first selectable, 1 to 8 bits of arbitrary transfer</li> <li>Continuous transmission, continuous reception, continuous transmission and reception are available.</li> </ul> </li> <li>Full duplex UART (Baud rate timer: selected from timer 0 to 4, or timer A) <ul> <li>Parity check, overrun error/framing error are detected</li> <li>Transfer bits 7 to 8 are selectable</li> </ul> </li> </ul>                                                  |

|                                   | <ul> <li>Serial interface 3 (Full duplex UART / Synchronous serial interface)</li> <li>* Function in KM101EF76K and KM101EF56K</li> <li>Synchronous serial interface <ul> <li>Transfer clock source</li> <li>fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4,</li> <li>Timer 0 to 4, Timer A output divided by 1, 2, 4, 8, 16, External clock</li> <li>MSB/LSB first selectable, 1 to 8 bits of arbitrary transfer</li> <li>Continuous transmission, continuous reception, continuous transmission and reception are available.</li> </ul> </li> <li>Full duplex UART (Baud rate timer: selected from timer 0 to 4, or timer A) <ul> <li>Parity check, overrun error/framing error are detected</li> <li>Transfer bits 7 to 8 are selectable</li> </ul> </li> </ul> |

|                                   | <ul> <li>Serial interface 4 (Multi master IIC / Synchronous serial interface)</li> <li>Synchronous serial interface <ul> <li>Transfer clock source</li> <li>fpll-div/2, fpll-div/4, fpll-div/8, fpll-div/32, fs/2, fs/4,</li> <li>Timer 0 to 4, Timer A output divided by 1, 2, 4, 8, 16, External clock</li> <li>MSB/LSB first selectable, 1 to 8 bits of arbitrary transfer</li> <li>Continuous transmission, continuous reception, continuous transmission and reception are available.</li> </ul> </li> <li>Multi master IIC</li> </ul>                                                                                                                                                                                                                                      |

- 7, 10-bit slave address is settable

- General call communication mode is supported

- Auto reset circuit

- Low voltage detection circuit

- Clock Monitoring Function

| • LED driver | 8 sets                                                                                                                                                                                                                                                           |                                        |            |            |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|------------|--|--|--|--|

| • LCD driver | Segment output<br>KM101EF76K: Max. 55 pins (SEG0 to SEG54)<br>KM101EF57G: Max. 41 pins (SEG0 to SEG40)<br>KM101EF56K: Max. 55 pins (SEG0 to SEG54)<br>Segment output pins can be switched to I/O ports in 1 bit.<br>* At reset, Segment outputs are input ports. |                                        |            |            |  |  |  |  |

|              | Common output: 4 pins                                                                                                                                                                                                                                            |                                        |            |            |  |  |  |  |

|              | COM0 to 3 can be switched to I/O                                                                                                                                                                                                                                 | ports in 1 bit.                        |            |            |  |  |  |  |

|              | Display mode selection                                                                                                                                                                                                                                           |                                        |            |            |  |  |  |  |

|              | Static                                                                                                                                                                                                                                                           |                                        |            |            |  |  |  |  |

|              | 1/2 duty, 1/2 bias                                                                                                                                                                                                                                               |                                        |            |            |  |  |  |  |

|              | 1/3 duty, $1/3$ bias                                                                                                                                                                                                                                             |                                        |            |            |  |  |  |  |

|              | 1/4 duty, 1/3 bias<br>LCD driver clock                                                                                                                                                                                                                           |                                        |            |            |  |  |  |  |

|              | When the source clock is the main $1/2^{18}, 1/2^{17}, 1/2^{16}, 1/2^{15}, 1/2^{14}, 1/2^{13},$                                                                                                                                                                  | clock (fpll) $1/2^{12} \cdot 1/2^{11}$ |            |            |  |  |  |  |

|              | When the source clock is the sub clock (fslow)<br>$1/2^9, 1/2^8, 1/2^7, 1/2^6$                                                                                                                                                                                   |                                        |            |            |  |  |  |  |

|              | Timer 0 to 4, Timer A output                                                                                                                                                                                                                                     |                                        |            |            |  |  |  |  |

|              | LCD power supply                                                                                                                                                                                                                                                 |                                        |            |            |  |  |  |  |

|              | LCD power supply is separated from $V_{DD5}$ . (can be used when $V_{LC1} \le V_{DD5}$ )                                                                                                                                                                         |                                        |            |            |  |  |  |  |

|              | External power supply voltage can be selectable.                                                                                                                                                                                                                 |                                        |            |            |  |  |  |  |

|              | (Supply voltage is supplied from $V_{LC1}$ , $V_{LC2}$ , and $V_{LC3}$ )                                                                                                                                                                                         |                                        |            |            |  |  |  |  |

|              | Internal dividing resistors                                                                                                                                                                                                                                      |                                        |            |            |  |  |  |  |

|              | (External power supply voltage is divided the voltage input to $V_{LC1}$ by internal                                                                                                                                                                             |                                        |            |            |  |  |  |  |

| _            | resistors.)                                                                                                                                                                                                                                                      | 1                                      |            |            |  |  |  |  |

| • Ports      | Ports                                                                                                                                                                                                                                                            | KM101EF76K                             | KM101EF57G | KM101EF56K |  |  |  |  |

|              |                                                                                                                                                                                                                                                                  | (pins)                                 | (pins)     | (pins)     |  |  |  |  |

|              | <i o="" ports=""></i>                                                                                                                                                                                                                                            | 104                                    | 70         | 104        |  |  |  |  |

|              | LCD segment                                                                                                                                                                                                                                                      | 55                                     | 41         | 55         |  |  |  |  |

|              | LCD common                                                                                                                                                                                                                                                       | 4                                      | 4          | 4          |  |  |  |  |

|              | Serial interface communication                                                                                                                                                                                                                                   | 30                                     | 21         | 30         |  |  |  |  |

|              | Timer I/O                                                                                                                                                                                                                                                        | 34                                     | 21         | 28         |  |  |  |  |

|              | Buzzer output                                                                                                                                                                                                                                                    | 4                                      | 2          | 4          |  |  |  |  |

|              | A/D input                                                                                                                                                                                                                                                        | 24                                     | 16<br>5    | 24<br>5    |  |  |  |  |

|              | External interrupt<br>LCD power supply                                                                                                                                                                                                                           | 10 3                                   | 3          | 3          |  |  |  |  |

|              | LED driver (high-current)                                                                                                                                                                                                                                        | 8                                      | 8          | 8          |  |  |  |  |

|              | High-speed oscillation                                                                                                                                                                                                                                           | 2                                      | 2          | 2          |  |  |  |  |

|              | Low-speed oscillation                                                                                                                                                                                                                                            | 2                                      | 2          | 2          |  |  |  |  |

|              | D/A output                                                                                                                                                                                                                                                       | 4                                      | 2          | 4          |  |  |  |  |

|              | <special function="" pins=""></special>                                                                                                                                                                                                                          | 10                                     | 10         | 10         |  |  |  |  |

|              | Operation mode input                                                                                                                                                                                                                                             | 3                                      | 3          | 3          |  |  |  |  |

|              | Reset input                                                                                                                                                                                                                                                      | 1                                      | 1          | 1          |  |  |  |  |

|              | Analog reference voltage input                                                                                                                                                                                                                                   | 1                                      | 1          | 1          |  |  |  |  |

|              | Power supply                                                                                                                                                                                                                                                     | 4                                      | 4          | 4          |  |  |  |  |

|              | <u> </u>                                                                                                                                                                                                                                                         |                                        |            |            |  |  |  |  |

#### 3. Pin Description

#### 3.1 Pin configuration

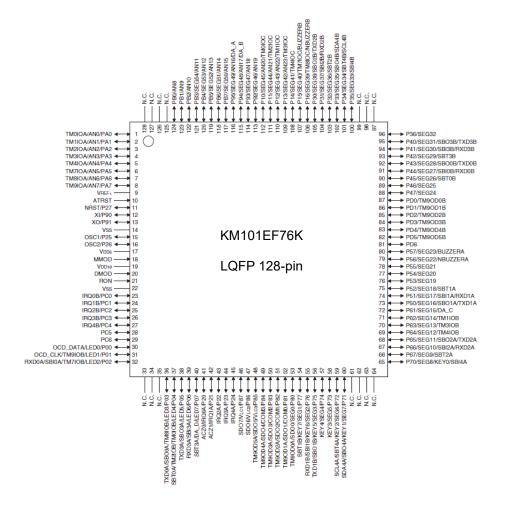

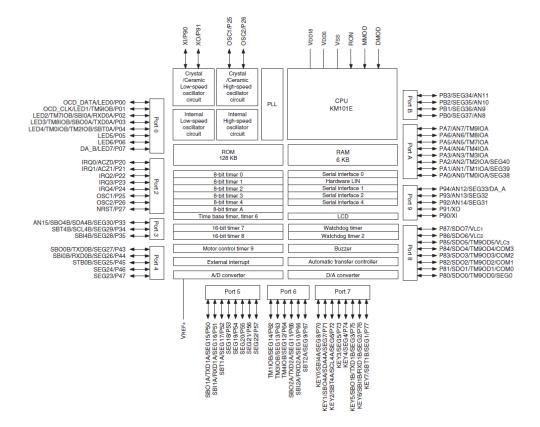

Figure: 3.1 Pin Configuration (KM101EF76K)

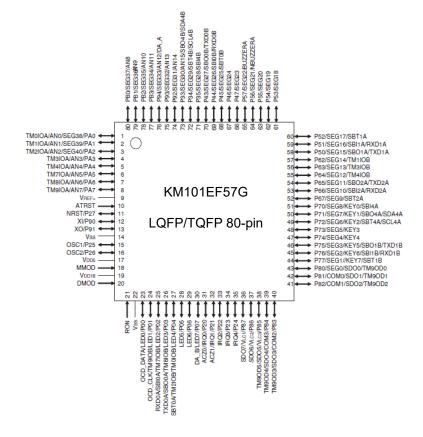

Figure: 3.2 Pin Configuration (KM101EF57G)

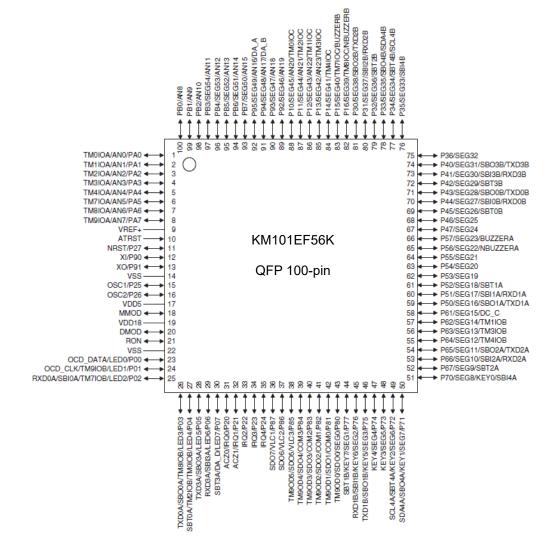

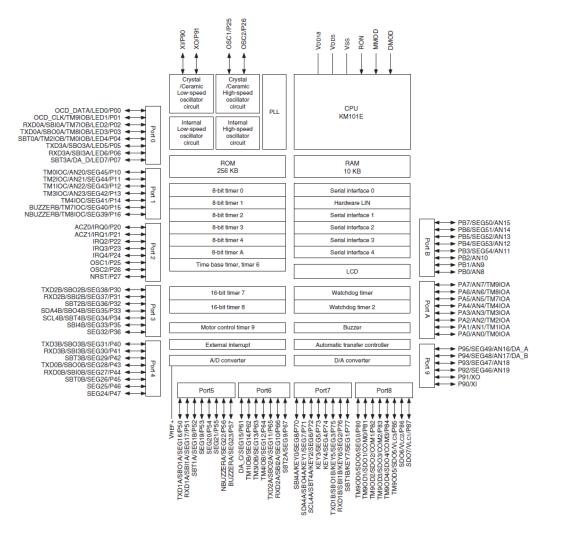

Figure: 3.3 Pin Configuration (KM101EF56K)

#### 3.2 Pin Functions

| Table: 3.1 Pin Function | ons (KM101EF76K) |

|-------------------------|------------------|

|                         |                  |

| KM101EF                                              | -76K                                          |        |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------|-----------------------------------------------|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins                                                 | Pin No.                                       | I/O    | Functions                                | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

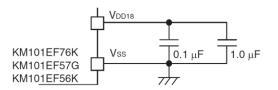

| VSS<br>VDD5                                          | 14<br>22<br>17                                | -      | Power supply pins                        | Supply 1.8 V to 5.5 V to VDD5, and 0 V to VSS. Connect 0.1 $\mu$ F and more than 1 $\mu$ F of bypass capacitor for interna power stabilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD18                                                | 19                                            | -      | Internal power output pin                | Outputs internal power voltage 1.8 V. Connect 0.1 $\mu$ F and more than 1 $\mu$ F of bypass capacitor between VDD18 and VSS pins for internal power stabilization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

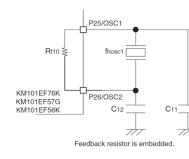

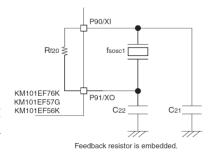

| OSC1                                                 | 15                                            | Input  | High-speed operation clock<br>input pin  | Connect these oscillation pins to ceramic oscillator or crystal oscillator for high-speed operation clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC2                                                 | 16                                            | Output | High-speed operation clock<br>output pin | For external clock input, input to OSC1 and open OSC2. The chip will not operate with an external clock when using either STOP mode or SLOW mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XI                                                   | 12                                            | Input  | Low-speed operation clock<br>input pin   | Connect these oscillation pins to ceramic oscillator or crystal oscillator for low-speed operation clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XO                                                   | 13                                            | Output | Low-speed operation clock<br>output pin  | For external clock input, input to XI and open XO. The chip will not operate with an external clock when using STOP mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NRST                                                 | 11                                            | Input  | Reset pin [Active low]                   | This pin resets the chip at power on, is allocated as P27 and contains an internal pull-up resistor (Typ. 50 k $\Omega$ ). Setting this pin low initializes the internal state of the LSI. Thereafter, setting the input to high releases the reset. The hardware waits for the system clock to stabilize, then processes the reset interrupt. Also, if "0" is written to P27 and the reset is initiated by software, a low level will be output. The output has an Nch open-drain configuration. If a capacitor is to be inserted between NRST and VDS, it is recommended that a discharge diode be placed between NRST and VDD5. |

| ATRST                                                | 10                                            | Input  | Auto reset setting pin                   | Input "High" to enable auto reset function and "Low" to disable this function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P00<br>P01<br>P02<br>P03<br>P04<br>P05<br>P06<br>P07 | 30<br>31<br>32<br>36<br>37<br>38<br>39<br>40  | I/O    | I/O port 0                               | 8-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>PODIR register.<br>A pull-up /pull-down resistor for each bit can be selected<br>individually by the POPLUD register.<br>A pull-up/down resistor connection for each port can be selected<br>individually by the SELUD register. (However, pull-up and pull-<br>down resistors cannot be mixed.)<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                         |

| P10<br>P11<br>P12<br>P13<br>P14<br>P15<br>P16        | 112<br>111<br>110<br>109<br>108<br>107<br>106 | I/O    | I/O port 1                               | 7-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>P1DIR register.<br>A pull-up /pull-down resistor for each bit can be selected<br>individually by the P1PLUD register.<br>A pull-up/down resistor connection for each port can be selected<br>individually by the SELUD register. (However, pull-up and pull-<br>down resistors cannot be mixed.)<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                         |

| P20<br>P21<br>P22<br>P23<br>P24<br>P25<br>P26        | 41<br>42<br>43<br>44<br>45<br>15<br>16        | I/O    | I/O port 2                               | 7-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>P2DIR register.<br>A pull-up resistor for each bit can be selected individually by the<br>P2PLU register.<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                                                                                                                                                                                                                |

| P27                                                  | 11                                            | Input  | Input port 2                             | P27 is an Nch open-drain port. When "0" is written and the reset is initiated by software, a low level will be output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| KM101E                                                      | F76K                                                                                                       |     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins                                                        | Pin No.                                                                                                    | I/O | Functions  | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P30<br>P31<br>P32<br>P33<br>P34<br>P35<br>P36               | 105<br>104<br>103<br>102<br>101<br>100                                                                     | I/O | I/O port 3 | 7-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>P3DIR register.<br>A pull-up resistor for each bit can be selected individually by the<br>P3PLU register.<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                                                                                                                    |

| P36<br>P40<br>P41<br>P42<br>P43<br>P44<br>P45<br>P46<br>P47 | 96<br>95<br>94<br>93<br>92<br>91<br>90<br>89<br>88                                                         | I/O | I/O port 4 | <ul> <li>8-bit CMOS tri-state I/O port.</li> <li>Each bit can be set individually as either an input or output by the P4DIR register.</li> <li>A pull-up /pull-down resistor for each bit can be selected individually by the P4PLUD register.</li> <li>A pull-up/down resistor connection for each port can be selected individually by the SELUD register. (However, pull-up and pull-down resistors cannot be mixed.)</li> <li>At reset, the input mode is selected and pull-up resistors are disabled (high impedance).</li> </ul> |

| P50<br>P51<br>P52<br>P53<br>P54<br>P55<br>P56<br>P57        | 73<br>74<br>75<br>76<br>77<br>78<br>79<br>80                                                               | I/O | I/O port 5 | <ul> <li>8-bit CMOS tri-state I/O port.</li> <li>Each bit can be set individually as either an input or output by the P5DIR register.</li> <li>A pull-up /pull-down resistor for each bit can be selected individually by the P5PLUD register.</li> <li>A pull-up/down resistor connection for each port can be selected individually by the SELUD register. (A pull-up/down can not be mixed.)</li> <li>At reset, the input mode is selected and pull-up resistors are disabled (high impedance).</li> </ul>                          |

| P61<br>P62<br>P63<br>P64<br>P65<br>P66<br>P67               | 72<br>71<br>70<br>69<br>68<br>67<br>66                                                                     | I/O | I/O port 6 | 7-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>P6DIR register.<br>A pull-up resistor for each bit can be selected individually by the<br>P6PLU register.<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                                                                                                                    |

| P70<br>P71<br>P72<br>P73<br>P74<br>P75<br>P76<br>P77        | 65<br>60<br>59<br>58<br>57<br>56<br>55<br>55<br>54                                                         | I/O | I/O port 7 | <ul> <li>8-bit CMOS tri-state I/O port.</li> <li>Each bit can be set individually as either an input or output by the P7DIR register.</li> <li>A pull-up /pull-down resistor for each bit can be selected individually by the P7PLUD register.</li> <li>A pull-up/down resistor connection for each port can be selected individually by the SELUD register. (A pull-up/pull down can not be mixed.)</li> <li>At reset, the input mode is selected and pull-up resistors are disabled (high impedance).</li> </ul>                     |

| P80<br>P81<br>P82<br>P83<br>P84<br>P85<br>P86<br>P87        | 54           53           52           51           50           49           48           47           46 | I/O | I/O port 8 | 8-bit CMOS tri-state I/O port.<br>Each bit can be set individually as either an input or output by the<br>P8DIR register.<br>A pull-up resistor for each bit can be selected individually by the<br>P8PLU register.<br>At reset, the input mode is selected and pull-up resistors are<br>disabled (high impedance).                                                                                                                                                                                                                    |

| -76K                                                | 1/0                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                             | 1/0                                                                                                                                                                                                                                                                                  | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |