# Multi-Message Record/Playback Devices

with Digital Audio Interface

nuvoTon

# nuvoTon

# **TABLE OF CONTENTS**

| 1  | GENERAL DESCRIPTION                                                                 | 4                    |

|----|-------------------------------------------------------------------------------------|----------------------|

| 2  | FEATURES                                                                            | 4                    |

| 3  | BLOCK DIAGRAM                                                                       | 6                    |

| 4  | PINOUT CONFIGURATION                                                                | 8                    |

| 5  | PIN DESCRIPTION                                                                     | 9                    |

| 6  | SPI INTERFACE                                                                       | 12                   |

| 7  | ANALOG AND DIGITAL SIGNAL PATH                                                      | 15                   |

|    | <ul> <li>7.1 ANALOG SIGNAL PATH</li></ul>                                           | 16<br>17<br>19<br>20 |

| 8  | ISD3900 MEMORY MANAGEMENT                                                           | 22                   |

|    | <ul> <li>8.1 ISD3900 MEMORY FORMAT</li></ul>                                        | 23                   |

|    | 8.2.2 Voice Macros                                                                  |                      |

|    | 8.2.3         User Data           8.2.4         Reserved Sectors                    |                      |

|    | 8.2.5 Message Recordings                                                            |                      |

|    | 8.3 MEMORY AND MESSAGE HEADERS                                                      |                      |

|    | 8.3.2 Message Header                                                                | 27                   |

|    | <ul> <li>8.4 DIGITAL ACCESS OF MEMORY</li> <li>8.5 DEVICE ERASE COMMANDS</li> </ul> |                      |

|    | 8.6 MEMORY CONTENTS PROTECTION                                                      |                      |

| 9  | I <sup>2</sup> S INTERFACE                                                          | 29                   |

| 10 | 0 CLOCK GENERATION                                                                  | 30                   |

|    | 10.1 EXTERNAL CRYSTAL OSCILLATOR                                                    |                      |

|    | <ul> <li>10.2 I<sup>2</sup>S CLOCK USAGE</li></ul>                                  |                      |

|    |                                                                                     |                      |

| 12 |                                                                                     |                      |

|    | 12.1 CLOCK CONFIGURATION                                                            |                      |

|    | 12.2 DEVICE STATUS REGISTER                                                         |                      |

|    | <ul> <li>12.3 DEVICE CONFIGURATION REGISTERS</li></ul>                              |                      |

| 13 | NA B                                                                                |                      |

| -  | 13.1 Audio Play and Record Commands                                                 |                      |

|    | Publication Release Date: Dec                                                       |                      |

# nuvoTon

| 13.1.1           | Play Voice Prompt                              | 62 |

|------------------|------------------------------------------------|----|

| 13.1.2           | Play Voice Prompt @Rn, $n = 0 \sim 7$          |    |

| 13.1.3           | Execute Voice Macro                            |    |

| 13.1.4           | Record Message                                 | 64 |

| 13.1.5           | Record Message at Address                      |    |

| 13.1.6           | Play Message at Address                        | 65 |

| 13.1.7           | Play Silence                                   | 66 |

| 13.1.8           | Stop Command                                   | 66 |

| 13.1.9           | Erase Message at Address                       |    |

| 13.1.10          | SPI Write PCM Data                             |    |

| 13.1.11          | SPI Read PCM Data                              |    |

| 13.1.12          | SPI Send Compressed Data to Decode             |    |

| 13.1.13          | SPI Receive Encoded Data                       |    |

|                  | VICE STATUS COMMANDS.                          |    |

| 13.2.1           | Read Status                                    |    |

| 13.2.2           | Read Interrupt                                 |    |

| 13.2.3           | Read Recorded Message Address Details          |    |

| 13.2.4           | Read Message Length                            |    |

| <i>13.2.5</i>    | Read I3900 ID.                                 |    |

|                  | SITAL MEMORY COMMANDS.                         |    |

| 13.3.1<br>13.3.2 | Digital Read.                                  |    |

| 13.3.2           | Digital Write                                  |    |

| 13.3.3           | Erase Memory<br>Chip Erase                     |    |

|                  | VICE CONFIGURATION COMMANDS                    |    |

| 13.4.1           | $PWR\_UP - Power up$                           |    |

| 13.4.2           | PWR_DN – Power Down                            |    |

| 13.4.3           | SET_CLK_CFG – Set Clock Configuration Register |    |

| 13.4.4           | RD_CLK_CFG – Read Clock Configuration Register |    |

| 13.4.5           | WR_CFG_REG – Write Configuration Register      |    |

| 13.4.6           | RD_CFG_REG – Read Configuration Register       |    |

| 14 ELEC          | CTRICAL CHARACTERISTICS                        | 80 |

| 14.1 AB          | SOLUTE MAXIMUM RATINGS                         | 80 |

|                  | ERATING CONDITIONS                             |    |

|                  | PARAMETERS                                     |    |

| 14.4 AC          | PARAMETERS                                     | 82 |

| 14.4.1           | Internal Oscillator                            |    |

| 14.4.2           | Inputs                                         | 82 |

| 14.4.3           | Outputs                                        |    |

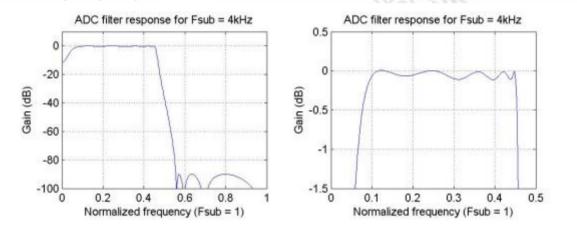

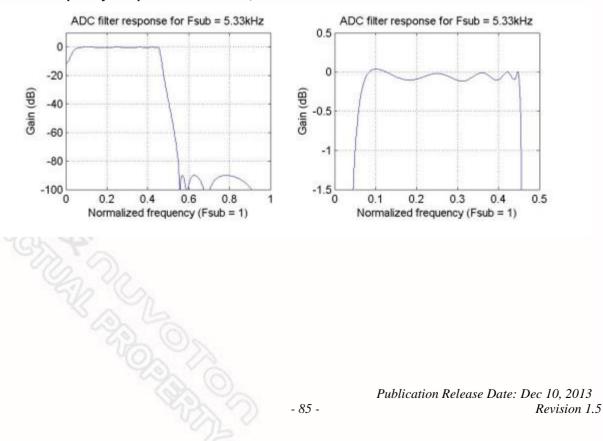

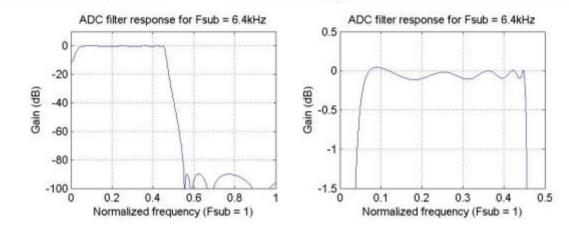

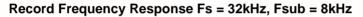

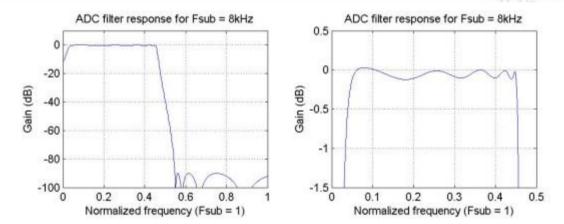

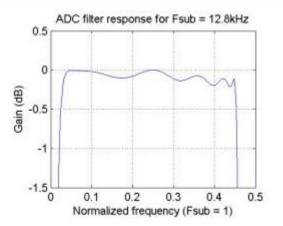

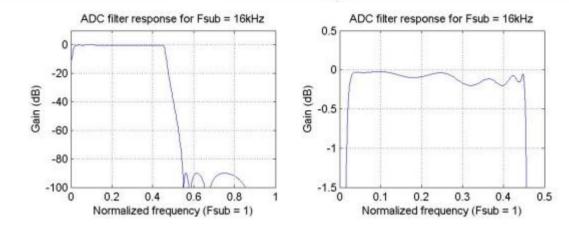

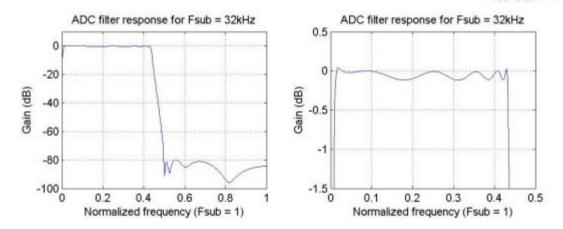

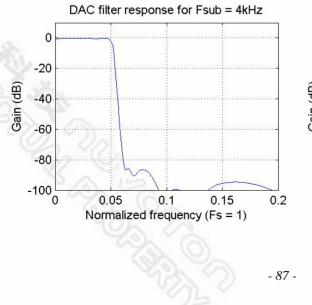

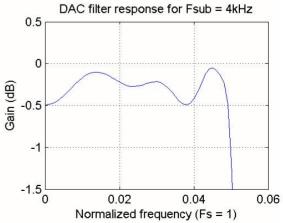

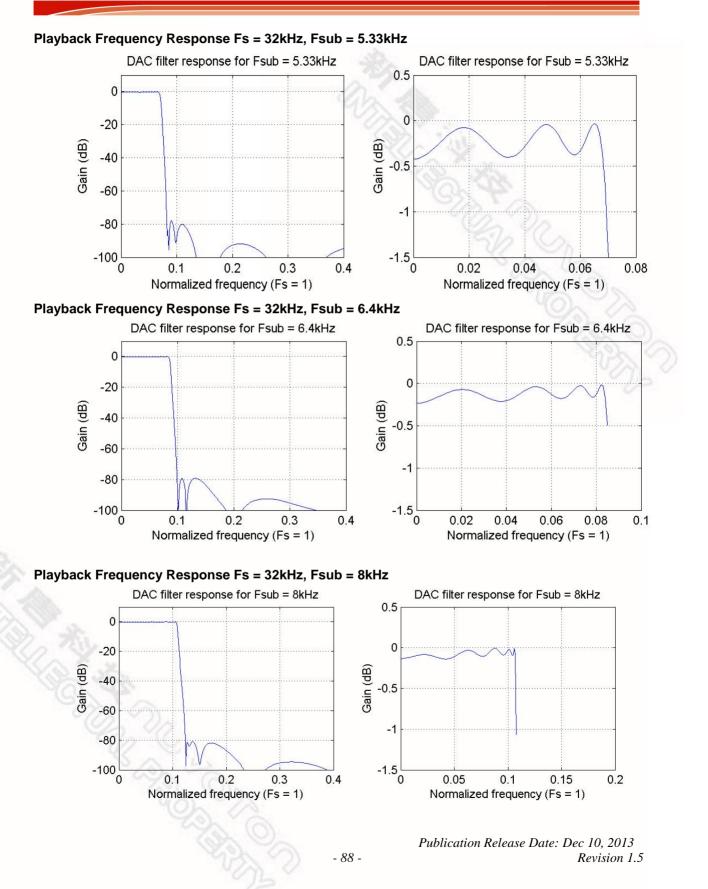

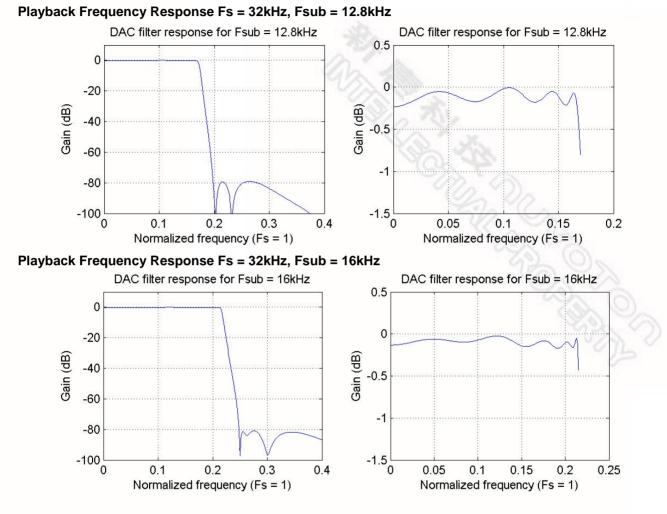

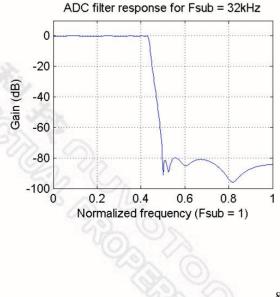

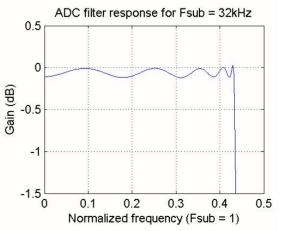

| 14.4.4           | ADC and DAC Frequency Responses                |    |

| 14.4.5           | SPI Timing                                     |    |

| 14.4.6           | I <sup>2</sup> S Timing                        | 91 |

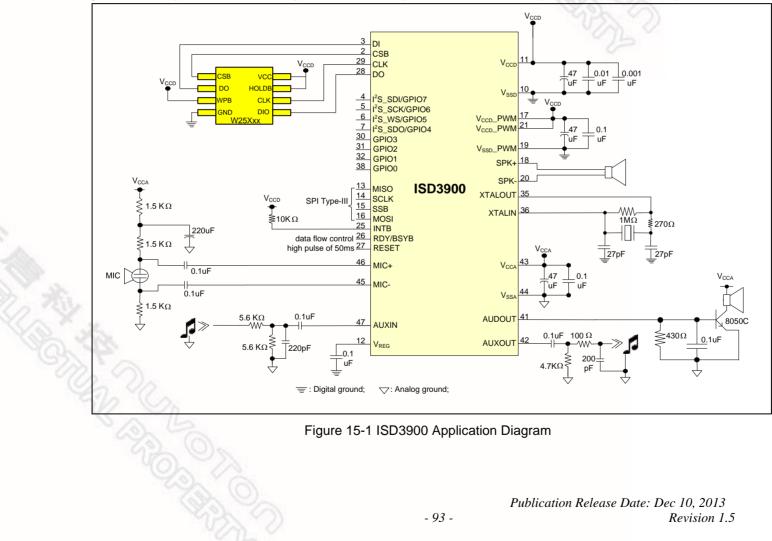

| 15 APPL          | ICATION DIAGRAM                                | 93 |

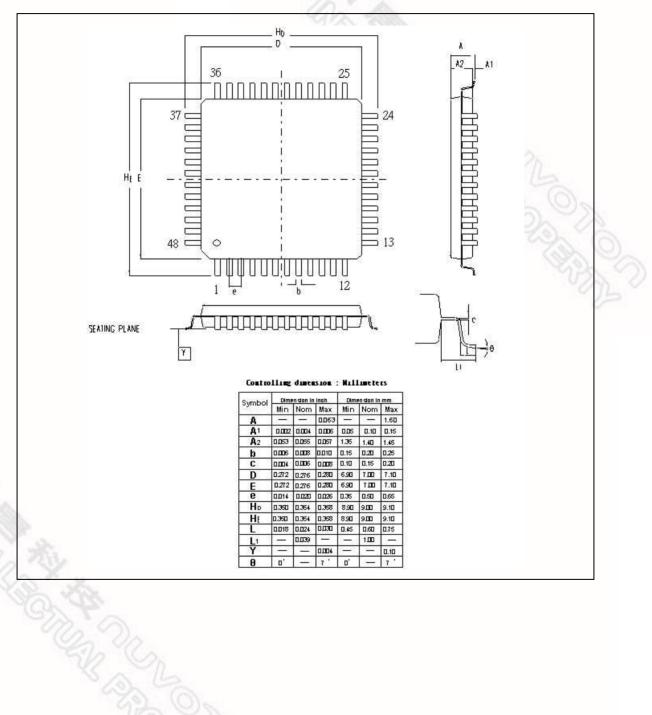

| 16 PACł          | KAGE SPECIFICATION                             | 94 |

| 16.1 481         | LEAD LQFP(7x7x1.4mm footprint 2.0mm)           | 94 |

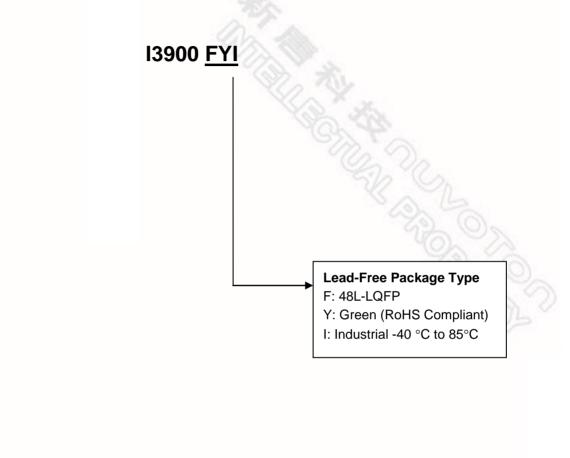

| 17 ORD           | ERING INFORMATION                              | 95 |

| 18 REVI          | SION HISTORY                                   | 96 |

|                  |                                                |    |

### 1 GENERAL DESCRIPTION

The ISD3900 is a multi-message ChipCorder<sup>®</sup> featuring digital compression, comprehensive memory management, and integrated analog/digital audio signal paths. The message management feature is designed to make message recording simple and address-free as well as make code development easier for playback-only applications. The ISD3900 utilizes winbond's 25X and 25Q series flash memory to provide non-volatile audio record/playback for a two-chip solution. Unlike other ChipCorder series, the ISD3900 provides an I<sup>2</sup>S digital audio interface, faster digital recording, higher sampling frequency, and a signal path with SNR equivalent to 12bit resolution.

The ISD3900 can take digital audio data via I<sup>2</sup>S or SPI interface. When I<sup>2</sup>S input is selected, it will replace the analog audio inputs and will support sample rates of 32, 44.1 or 48 kHz depending upon clock configuration. When SPI interface is chosen, the sample rate of the audio data sent must be one of the ISD3900 supported sample rates.

The ISD3900 has built-in analog audio inputs, analog audio line driver, and speaker driver output. The two analog audio inputs to the device are: (1) AUXIN has a fixed gain configured by SPI command, and (2) ANAIN/ANAOUT has a fixed gain amplifier with the gain set by two external resistors. ANAIN/ANAOUT can also be used as a microphone differential input (ANAIN/ANAOUT becomes MIC+/MIC-) in conjunction with an automatic gain control (AGC) circuit configured by SPI command. Analog outputs are available in three forms: (1) AUXOUT is a single-ended voltage output; (2) AUDOUT can be configured as either a single-ended voltage output or a single-ended current output; (3) BTL (bridge-tied-load) is a differential voltage output.

### 2 FEATURES

- External Memory: support winbond's 25X and 25Q SpiFlash.

- The addressing ability of ISD3900 is up to 128Mbit<sup>1</sup>, which is 64-minute recording time based on 8kHz/4bit ADPCM.

- Fast Digital Programming

- Programming rate can go up to 1Mbits/second mainly limited by the flash memory write rate.

Message Management

- Perform address-free recording: The ISD3900 allocates memory for new recording requests and upon completion, returns a start address to the host via SPI interface

- o Store pre-recorded audio (Voice Prompts) using high quality digital compression

- Use a simple index based command for playback

- Execute pre-programmed macro scripts (Voice Macros) designed to control the configuration of the device and play back Voice Prompts sequences and message recordings.

- Sample Rate

- Seven record and playback sampling frequencies are available for a given master sample rate. For example, the record and playback sampling frequencies of 4, 5.3, 6.4, 8, 12.8, 16 and 32kHz are available when the device is clocked at a 32kHz master sample rate.

- For I<sup>2</sup>S operation, 32, 44.1 and 48kHz master sample rates are available with record and playback sampling frequencies scaling accordingly.

- Compression Algorithms

- For recording

- ADPCM: 2, 3, 4 or 5 bits per sample

<sup>&</sup>lt;sup>1</sup> For details please refer to Section 8.

- μ-Law: 6, 7 or 8 bits per sample

- Differential µ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample. Each sampled value is stored as a code, offering no compression but preserving maximum resolution

- For Pre-Recorded Voice Prompts

- µ-Law: 6, 7 or 8 bits per sample

- Differential µ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample

- Enhanced ADPCM: 2, 3, 4 or 5 bits per sample

- Variable-bit-rate optimized compression. This allows best possible compression given a metric of SNR and background noise levels.

- Oscillator

- o Internal oscillator with internal reference: 2.048 MHz with ±10% deviation

- Internal oscillator with external resistor: 2.048 MHz with ±5% deviation when Rosc is 78.7Kohm

- External crystal or clock input

- $\circ$  I<sup>2</sup>S bit clock input

- Crystals and resonators support standard audio sampling rates of 2.048, 4.096, 8.192, 12.288 and11.2896MHz

- Inputs

- o AUXIN: Analog input with 2-bit gain control configured by SPI command

- ANAIN/ANAOUT:

- Analog input with the gain set by two external resistors from ANAOUT to ANAIN, or

- Microphone differential input (ANAIN/ANAOUT becomes MIC+/MIC-)

- Digital AGC:

- Automatic gain control of digitized data from the analog input

- Outputs

- $\circ$  PWM: Class D speaker driver to direct drive an 8 $\Omega$  speaker or buzzer

- AUDOUT: configurable as a current or voltage single-ended line driver

- AUXOUT: a single-ended voltage output

- o BTL: a differential voltage output

- I/Os

- SPI interface: MISO, MOSI, SCLK, SSB for commands and digital audio data

- I<sup>2</sup>S interface: I<sup>2</sup>S\_CLK, I<sup>2</sup>S\_WS, I<sup>2</sup>S\_SDI, I<sup>2</sup>S\_SDO for digital audio data

- $\circ$  8 GPIO pins (4 of the 8 GPIO pins share with I<sup>2</sup>S).

- Three 8-bit Volume Control set by SPI command for flexible mixing

- VOLA: volume control for the digital audio data from I<sup>2</sup>S or analog inputs

- VOLB: volume control for the digital audio data from decompression block or SPI

- VOLC: master volume control for PWM, AUDOUT, AUXOUT and I<sup>2</sup>S outputs

- Operating Voltage: 2.7-3.6V

- Standby Current: 1uA typical

- Package: Green 48L-LQFP

- Temperature Options:

Industrial: -40°C to 85°C

NUVOTON

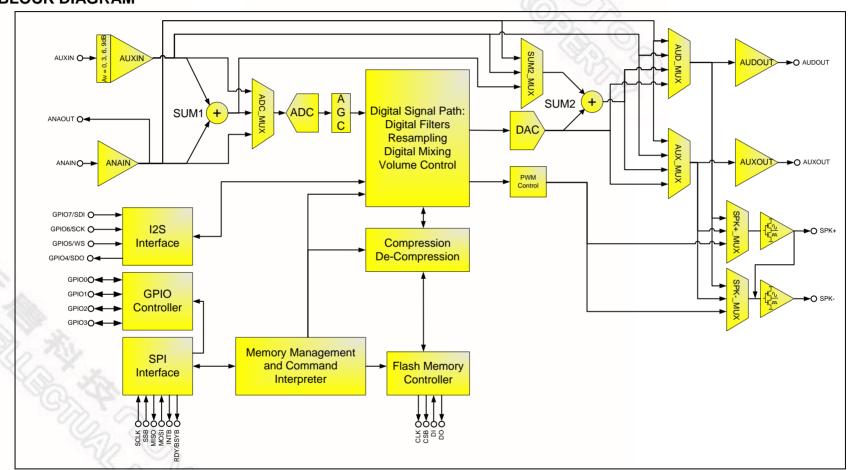

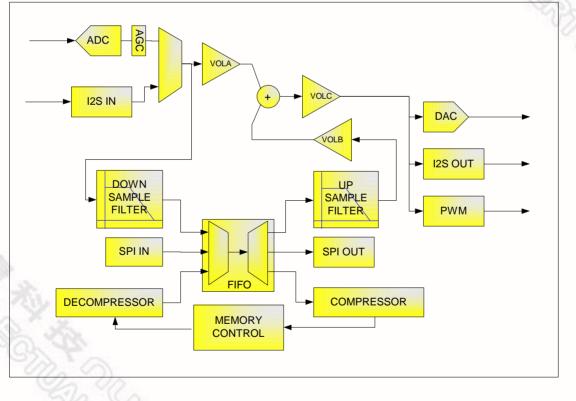

#### **3 BLOCK DIAGRAM**

Figure 3-1 ISD3900 Block Diagram, ANAIN Selected

nuvoTon

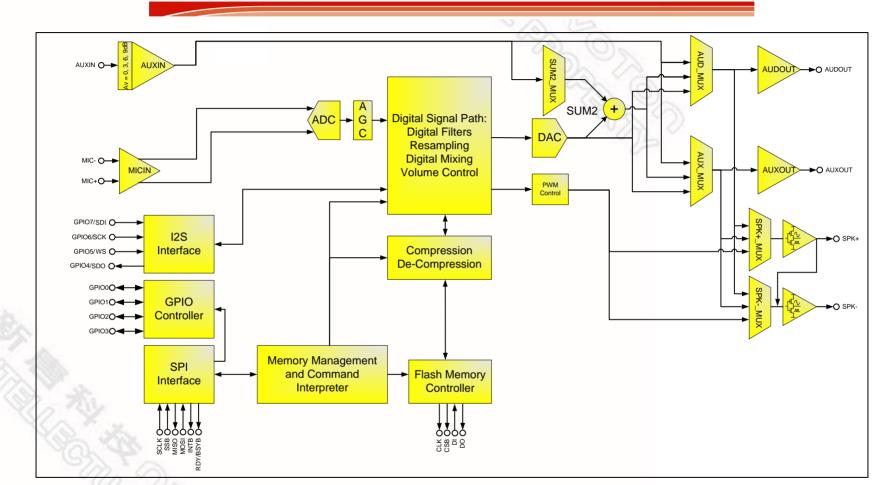

Figure 3-2 ISD3900 Block Diagram, MICIN Selected

# nuvoTon

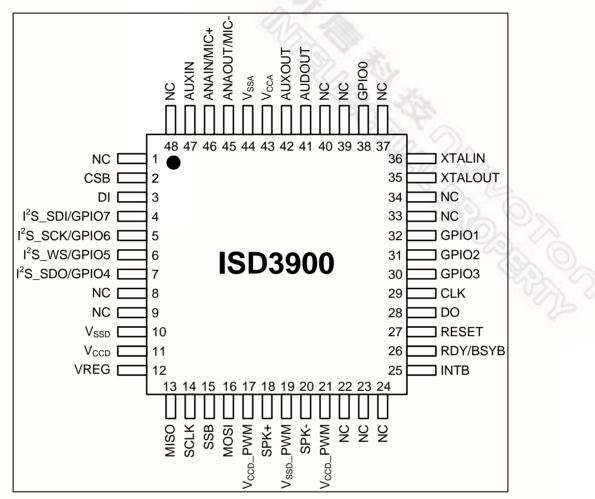

### **4 PINOUT CONFIGURATION**

Figure 4-1 ISD3900 48-Lead LQFP Pin Configuration.

#### PIN DESCRIPTION 5

| Pin<br>Number | Pin Name                       | I/O | Function                                                                                                                                                                                                                                          |

|---------------|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                              |

| 2             | CSB                            | 0   | Chip Select Bar of the external serial flash interface.                                                                                                                                                                                           |

| 3             | DI                             | I   | Serial data input to external serial flash interface. Connects to data output (DO) of external flash memory.                                                                                                                                      |

| 4             | I <sup>2</sup> S_SDI/<br>GPIO7 | I   | Serial Data Input of the I <sup>2</sup> S interface (If I2S is not used, this pin should be grounded).<br>Or, can be configured as a GPIO pin.                                                                                                    |

| 5             | I <sup>2</sup> S_SCK/<br>GPIO6 | I/O | Clock input in slave mode or clock output in master mode. This pin car<br>be configured as an external clock buffer if I <sup>2</sup> S is not used (If I2S is not<br>used, this pin should be grounded).<br>Or, can be configured as a GPIO pin. |

| 6             | I <sup>2</sup> S_WS/<br>GPIO5  | I/O | Word Select (WS) input in slave mode or WS output in master mode (I<br>I2S is not used, this pin should be grounded).<br>Or, can be configured as a GPIO pin.                                                                                     |

| 7             | I <sup>2</sup> S_SDO/<br>GPIO4 | 0   | Serial Data Output of the I <sup>2</sup> S Interface (If I2S is not used, this pin should be left unconnected).<br>Or, can be configured as a GPIO pin.                                                                                           |

| 8             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                              |

| 9             | NC                             |     | This pin should be left unconnected.                                                                                                                                                                                                              |

| 10            | V <sub>SSD</sub>               | I   | Digital Ground.                                                                                                                                                                                                                                   |

| 11            | V <sub>CCD</sub>               | Ι   | Digital power supply.                                                                                                                                                                                                                             |

| 12            | VREG                           | 0   | A 1.8V regulator to supply the internal logic. A 0.1uF capacitor should be connected to this pin for supply decoupling and stability.                                                                                                             |

| 13            | MISO                           | 0   | Master-In-Slave-Out. Serial output from the ISD3900 to the host. This pin is in tri-state when SSB=1.                                                                                                                                             |

| 14            | SCLK                           | I   | Serial Clock input to the ISD3900 from the host.                                                                                                                                                                                                  |

| 15            | SSB                            | I   | Slave Select input to the ISD3900 from the host. When SSB is low device is selected and responds to commands on the SPI interface.                                                                                                                |

| 16            | MOSI                           | I   | Master-Out-Slave-In. Serial input to the ISD3900 from the host.                                                                                                                                                                                   |

| 17 🤇          | V <sub>CCD</sub> _PWM          |     | Digital Power for the PWM Driver.                                                                                                                                                                                                                 |

# nuvoTon

| Pin<br>Number | Pin Name              | I/O | Function                                                                                                                                                                             |  |  |

|---------------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18            | SPK+                  | 0   | PWM driver positive output. This SPK+ output, together with SPK- pir provide a differential output to drive $8\Omega$ speaker or buzzer. During power down this pin is in tri-state. |  |  |

|               |                       |     | Or, can be configured as BTL which, together with SPK- pin, provide a differential voltage output.                                                                                   |  |  |

|               |                       |     | Or, can independently switch to AUDOUT or AUXOUT.                                                                                                                                    |  |  |

| 19            | V <sub>SSD</sub> _PWM | I   | Digital Ground for the PWM Driver.                                                                                                                                                   |  |  |

| 20            | SPK-                  | 0   | PWM driver negative output. This SPK- output, together with SPK+ pin, provides a differential output to drive $8\Omega$ speaker or buzzer. During power down this pin is tri-state.  |  |  |

|               |                       |     | Or, can be configured as BTL which, together with SPK+ pin, provide a differential voltage output.                                                                                   |  |  |

|               |                       |     | Or, can independently switch to AUDOUT or AUXOUT.                                                                                                                                    |  |  |

| 21            | V <sub>CCD</sub> PWM  | I   | Digital Power for the PWM Driver.                                                                                                                                                    |  |  |

| 22            | NC                    |     | This pin should be left unconnected.                                                                                                                                                 |  |  |

| 23            | NC                    |     | This pin should be left unconnected.                                                                                                                                                 |  |  |

| 24            | NC                    |     | This pin should be left unconnected.                                                                                                                                                 |  |  |

| 25            | INTB                  | 0   | Active low interrupt request pin. This pin is an open-drain output.                                                                                                                  |  |  |

| 26            | RDY/BSYB              | 0   | An output pin to report the status of data transfer on the SPI interface.<br>"High" indicates that ISD3900 is ready to accept new SPI commands<br>or data.                           |  |  |

| 27            | RESET                 | I   | Applying power to this pin will reset the chip. (A high pulse of 50ms or more will reset the chip.)                                                                                  |  |  |

| 28            | DO                    | 0   | Serial data output of the external serial flash interface. Connects to data input (DI) of external serial flash.                                                                     |  |  |

| 29            | CLK                   | 0   | Serial data CLK of the external serial flash interface.                                                                                                                              |  |  |

| 30            | GPIO3                 | I/O | GPIO                                                                                                                                                                                 |  |  |

| 31            | GPIO2                 | I/O | GPIO                                                                                                                                                                                 |  |  |

| 32            | GPIO1                 | I/O | GPIO                                                                                                                                                                                 |  |  |

| 33            | NC                    |     | This pin should be left unconnected.                                                                                                                                                 |  |  |

| 34            | NC                    |     | This pin should be left unconnected.                                                                                                                                                 |  |  |

| 35            | XTALOUT               | 0   | Crystal interface output pin.                                                                                                                                                        |  |  |

# nuvoTon

| Number | Pin Name         | I/O                                          | Function                                                                                                                                                                                                                                                                                                                                             |

|--------|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36     | XTALIN           | I                                            | The CLK_CFG register determines one of the following three configurations: (1) A crystal or resonator connected between the XTALOUT and XTALIN pins. (2) A resistor connected to GND as a reference current to the internal oscillator and left the XTALOUT unconnected. (3) An external clock input to the device and left the XTALOUT unconnected. |

| 37     | NC               |                                              | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 38     | GPIO0            | I/O                                          | GPIO                                                                                                                                                                                                                                                                                                                                                 |

| 39     | NC               |                                              | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 40     | NC               |                                              | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

| 41     | AUDOUT           | 0                                            | Audio Out. This pin can be either a voltage output or a current output configured by the internal registers via SPI command.<br>If AUDOUT is not used, this pin should be left unconnected.                                                                                                                                                          |

| 42     | AUXOUT           | 0                                            | Aux Out. This pin is an analog voltage output.<br>If AUXOUT is not used, this pin should be left unconnected.                                                                                                                                                                                                                                        |

| 43     | V <sub>CCA</sub> | I                                            | Analog power supply pin.                                                                                                                                                                                                                                                                                                                             |

| 44     | V <sub>SSA</sub> | I                                            | Analog ground pin.                                                                                                                                                                                                                                                                                                                                   |

| 45     | ANAOUT/<br>MIC-  | 0                                            | Variable gain analog output with the gain set by feedback resistance to<br>ANAIN.<br>Or, can be configured as MIC- which, together with MIC+, provides a<br>microphone differential input.<br>If ANAIN/ANAOUT is not used, this pin should be left unconnected.                                                                                      |

| 46     | ANAIN/<br>MIC+   | I                                            | Variable gain analog input.<br>Or, can be configured as MIC+ which, together with MIC-, provides a<br>microphone differential input.<br>If ANAIN/ANAOUT is not used, this pin should be left unconnected.                                                                                                                                            |

| 47     | AUXIN            | I                                            | Auxiliary input with the gain set by SPI command<br>If AUXIN is not used, this pin should be left unconnected.                                                                                                                                                                                                                                       |

| 48     | NC               | <u>†                                    </u> | This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                 |

#### **6 SPI INTERFACE**

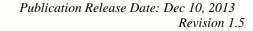

This is a standard four-wire interface used for communication between ISD3900 and the host. It consists of an active low slave-select (SSB), a serial clock (SCLK), a data input (Master Out Slave In - MOSI), and a data output (Master In Slave Out - MISO). In addition, for some transactions requiring data flow control, a RDY/BSYB signal (pin) is available.

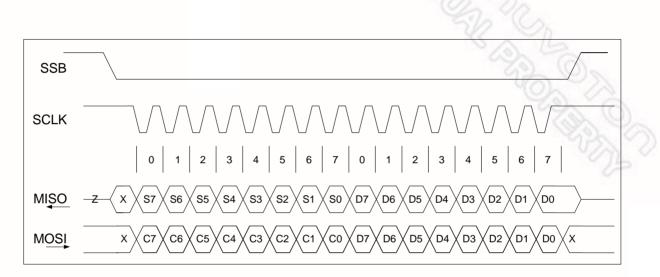

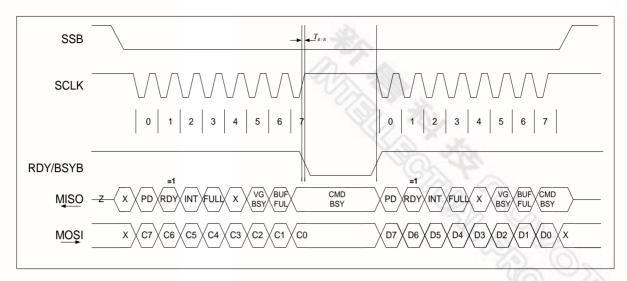

The ISD3900 supports SPI mode 3: (1) SCLK must be high when SPI bus is inactive, and (2) data is sampled at SCLK rising edge. A SPI transaction begins on the falling edge of SSB and its waveform is illustrated below:

Figure 6-1 SPI Data Transaction.

A transaction begins with sending a command byte (C7-C0) with the most significant bit (MSB – C7) sent in first. During the byte transmission, the status (S7-S0) of the device is sent out via the MISO pin. After the byte transmission, depending upon the command sent, one or more bytes of data will be sent via the MISO pin.

RDY/BSYB pin is used to handshake data into or out of the device. Upon completion of a byte transmission, RDY/BSYB pin could change its state after the rising edge of the SCLK if the built-in 32byte data buffer is either full or empty. At this point, SCLK must remain high until RDY/BSYB pin returns to high, indicating that the ISD3900 is ready for the next data transmission. See below for timing diagram.

### nuvoTon

Figure 6-2 R/B Timing for SPI Writing Transactions.

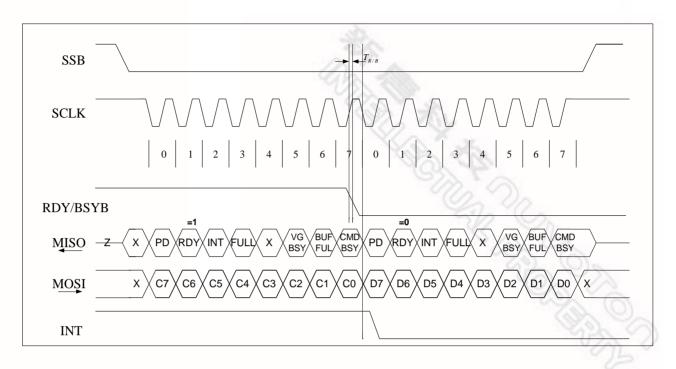

If the SCLK does not remain high, RDY bit of the status register will be set to zero and be reported via the MISO pin so the host can take the necessary actions (i.e., terminate SPI transmission and retransmit the data when the RDY/BSYB pin returns to high).

For commands (i.e., DIG\_READ, SPI\_PCM\_READ and SPI\_RCV\_ENC) that read data from ISD3900, MISO is used to read the data; therefore, the host must monitor the status via the RDY/BSYB pin and take the necessary actions.

The INT pin will go low to indicate (1) data overrun/overflow when sending data to the ISD3900; or (2) invalid data from ISD3900. See Figure 6-3 for the timing diagram.

### nuvoTon

Figure 6-3 SPI Transaction Ignoring RDY/BSYB

### 7 ANALOG AND DIGITAL SIGNAL PATH

#### 7.1 ANALOG SIGNAL PATH

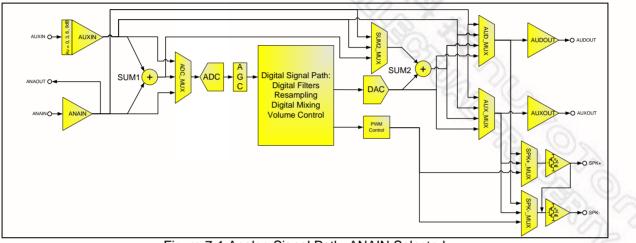

Analog signal path provides a configurable set of two analog inputs and three analog outputs along with multiplexing and summation blocks to route signals between analog blocks and the digital signal path.

Figure 7-1 Analog Signal Path, ANAIN Selected

Analog inputs consist of variable gain input amplifiers:

- AUXIN can be configured by SPI command

- ANAIN is determined by a selection of external resistors. ANAIN can also be configured as MICIN (ANAIN/ANAOUT becomes MIC+/MIC-), which provides a microphone differential input.

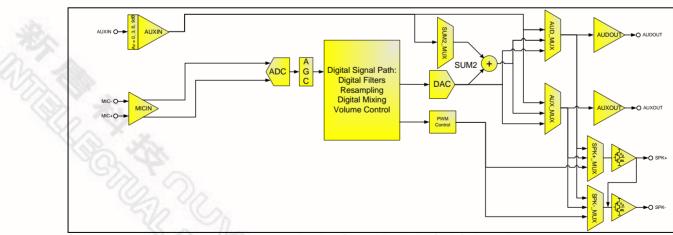

Figure 7-2 Analog Signal Path, MICIN Selected

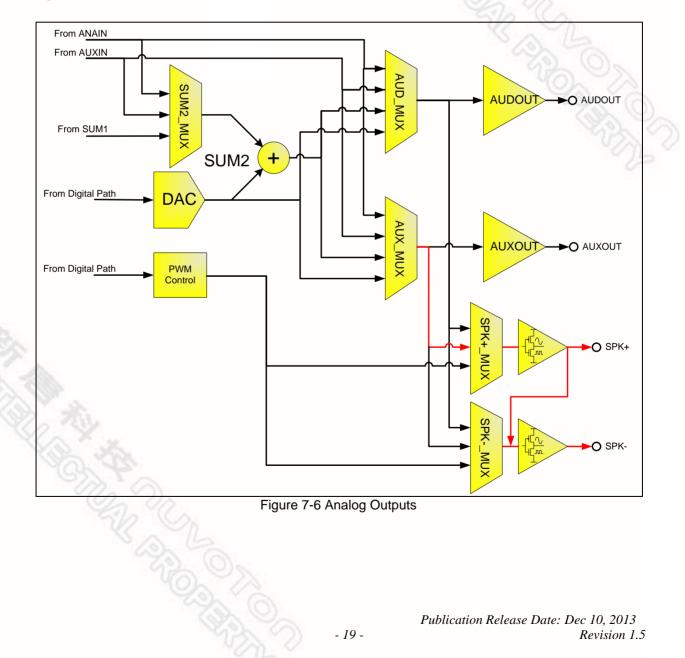

Analog outputs consist of:

- AUXOUT is a single-ended voltage output

- AUDOUT can be configured as a single-ended voltage output or a single-ended current output. When configured as a voltage output, AUDOUT is exactly the same as the AUXOUT.

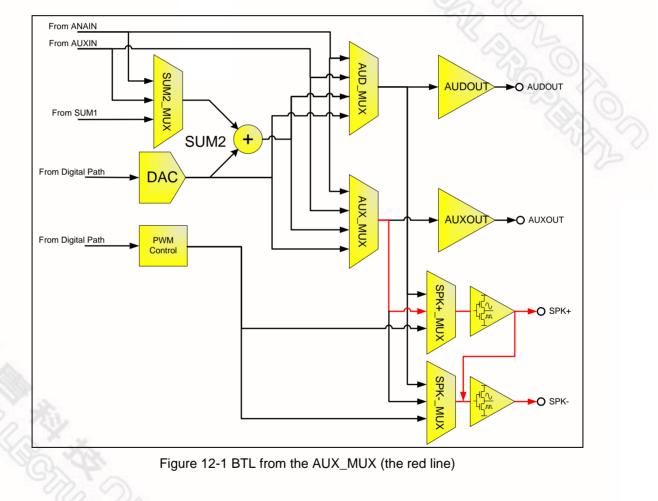

- BTL (bridge-tied-load) is a differential voltage output, which shares the same two pins of PWM (SPK+/SPK-). Signal source of BTL could be either from AUD\_MUX or AUX\_MUX.

- o Besides BTL, SPK+ and/or SPK- can also be configured individually:

- SPK+ can switch to AUDOUT or AUXOUT

- SPK- can switch to AUDOUT or AUXOUT

The analog path consists of the following blocks: AUXIN, ANAIN (or MICIN), SUM1, ADC\_MUX (SUM1 and ADC\_MUX are ineffective when MICIN is selected), SUM2, SUM2\_MUX, AUD\_MUX, AUX\_MUX, SPK+\_MUX, and SPK-\_MUX. The summation blocks, SUM1 and SUM2, are able to mix two signals together. SUM1 mixes the two analog inputs (AUXIN and ANAIN) for input into the digital signal path. SUM2 mixes the analog input (AUXIN, or ANAIN, or AUXIN plus ANAIN) with the digital signal path output. ADC\_MUX provides input selection into the ADC. AUD\_MUX and AUX\_MUX provide input selection into the AUDOUT and AUXOUT blocks. SPK+\_MUX and SPK-\_MUX provide input selection into the SPK+ and SPK- blocks. The configuration registers, CFG5-CFG9 & CFG18, control the active path features, allow individual power control of each block and enable the muting of certain path inputs. The details of the path configuration registers are described in Section 12.3.

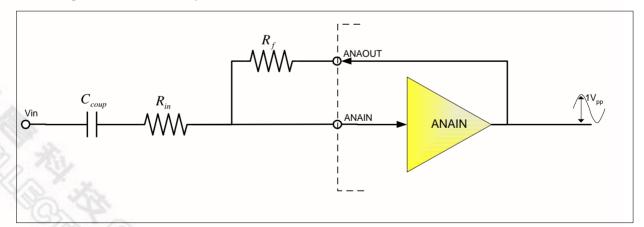

#### 7.1.1 ANAIN & MICIN Analog Input

#### Single-ended ANAIN Input

#### Figure 7-3 ANAIN Input Amplifier

The ANAIN input amplifier is designed to allow a variable gain set via two external resistors. The goal of gain selection is to produce a  ${}^{1}V_{pp}$  signal into the ISD3900 audio path. Voltage gain is:

#### nuvoton

$A_{v} = R_{f} / R_{in}$

ANAIN supports gain settings from 1 to 100 according to  $A_v = R_f / R_{in}$ .  $R_f$  should satisfy  $40k\Omega \le Rf \le 100k\Omega$ . To achieve a gain of 100,  $R_f$  can be set to  $100 k\Omega$ , and  $R_{in}$  set to  $1 k\Omega$ .

$C_{\it coup}$  AC couples signals into the ISD3900, forming a single pole high pass filter. The 3dB frequency is given by:

$f_{pass} = \frac{1}{2\pi R_{in} C_{coup}}$

For  $C_{coup} = 1\mu F$  ,  $R_{in} = 1k\Omega$  , signals above 160Hz will be fed into the audio path.

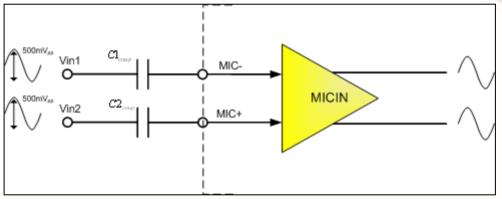

#### **Differential MICIN Input**

Figure 7-4 Differential MIC Input Amplifier

The ISD3900 allows the use of pins ANAIN and ANAOUT as differential MIC inputs. In this mode, the ANAIN and ANAOUT pins become MIC+ and MIC- and allow a differential input to be applied to the ADC. This configuration is designed to be used in conjunction with the AGC to amplify microphone signals while achieving good common mode rejection of supply noise. No mixing with AUXIN is possible in this mode.

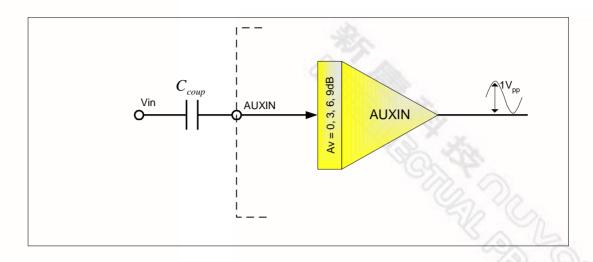

#### 7.1.2 AUX Analog Input

The AUX Analog Input amplifies input signals with a fixed gain of 0dB, 3dB, 6dB, or 9dB, selectable via SPI command. Similar to ANAIN, the gain setting should be configured so that the output signal has a 1Vpp swing.

# nuvoTon

#### Figure 7-5 AUXIN Input Amplifier

The coupling capacitor,  $C_{coup}$ , like in the case of ANAIN, should be set according to the value of to allow signals above a certain frequency to pass through. The relationship repeated here is:

$$f_{pass} = \frac{1}{2\pi R_{in} C_{coup}}$$

R

$R_{in}$  is the input impedance of the AUXIN amplifier and is dependent upon the gain setting as shown in Table 7-1 below.

| Setting | Gain dB | Gain | Rin (kOhms) |

|---------|---------|------|-------------|

| 00      | 0       | 1.00 | 40.0        |

| 01      | 3       | 1.41 | 33.2        |

| 10      | 6       | 2.00 | 26.7        |

| 11      | 9       | 2.82 | 21.0        |

| Table 7-1 | Gain Setting | g Vs. Rin |

|-----------|--------------|-----------|

|-----------|--------------|-----------|

The minimum value of  $R_{in}$  is approximately 20kOhms, so a  $C_{coup}$  of 1µF will allow audio signals to pass through under all possible gain settings.

# ηυνοτοη

#### 7.1.3 AUX & AUD Analog Output

AUXOUT is a single-ended voltage output. It needs an external amplifier to drive the speaker. AUXOUT together with the external amplifier is usually used when loud volume like 1 watt output is needed.

AUDOUT can be configured as a single-ended voltage output or a single-ended current output. When configured as a voltage output, AUDOUT is exactly the same as the AUXOUT. When configured as a current output, it uses a transistor to drive the speaker. Please note that the signal coming out of AUD\_MUX is always voltage regardless configured as a voltage or current output; if configured as a current output, the AUDOUT block that follows the AUD\_MUX converts the voltage signal to current signal.

#### 7.1.4 BTL Analog Output

BTL (bridge-tied-load) is a differential voltage output, which shares the same two pins of PWM (SPK+ and SPK-). As a differential output, BTL is naturally better than AUXOUT, the single-ended output, in terms of noise rejection.

BTL can directly drive a speaker or drive a speaker via an external amplifier. Since BTL direct-drive cannot reach the volume level that most users require, a usage together with an external amplifier is recommended. Below is a table comparing the BTL, AUXOUT, and PWM:

|                 | BTL                                                                                              | AUXOUT                                   | PWM            |

|-----------------|--------------------------------------------------------------------------------------------------|------------------------------------------|----------------|

| Driving Method  | Can direct drive, but an<br>external amplifier is<br>required to reach<br>adequate volume level. | Need an external amplifier.              | Direct drive.  |

| Driving Ability | High: depends on the external amplifier.                                                         | High: depends on the external amplifier. | 360 mW.        |

| Quality         | Typical 80dB with good noise rejection.                                                          | Typical 80dB.                            | Typical 60dB   |

| Cost            | Extra cost of the external amplifier.                                                            | Extra cost of the external amplifier.    | No extra cost. |

Table 7-2 Comparison of BTL, AUXOUT, and PWM

Signal source of BTL could be either from AUD\_MUX or AUX\_MUX. Figure 7-6 (the red line) shows an example of BTL setting from the AUX\_MUX.

Besides BTL, SPK+ and/or SPK- can also be configured individually:

- SPK+ can switch to AUDOUT or AUXOUT

- SPK- can switch to AUDOUT or AUXOUT

For detailed settings, please refer to 12.3 Device Configuration Registers, CFG18.

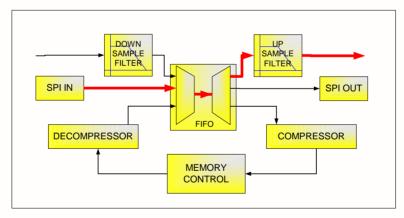

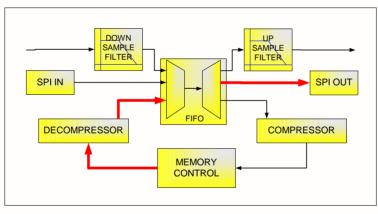

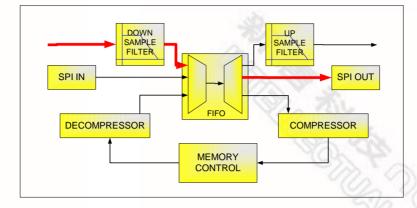

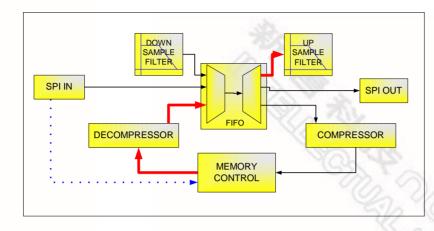

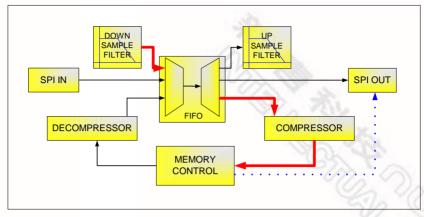

#### 7.2 DIGITAL SIGNAL PATH

The digital signal path performs filtering, sample rate conversion, mixing, volume control and compression. A block diagram of the digital signal path is shown in Figure 7-7.

Figure 7-7The digital signal path operates at a master sample rate Fs (nominally 32kHz) set by the master clock source (see Section 10). It has the ability to up-sample or down-sample to a lower sample-rate, Fsub for record, playback and audio transfer to/from the SPI interface. Audio input at Fs into the signal path comes either from the ADC path or the I<sup>2</sup>S digital audio interface. Audio at Fsub is up-sampled and can be mixed with the input and level adjusted via VOLA, VOLB and VOLC before going out on the DAC, I<sup>2</sup>S or PWM driver paths. The FIFO synchronizes audio sources at the sub-sampled bandwidth. One input and one output can be active at a time. The possible combinations are:

$\begin{array}{l} {\sf SPI\_IN} \rightarrow {\sf COMPRESS} \ ({\sf SPI} \ {\sf record}) \\ {\sf SPI\_IN} \rightarrow {\sf UPSAMPLE} \ ({\sf SPI} \ {\sf feed-through}) \\ {\sf DOWNSAMPLE} \rightarrow {\sf COMPRESS} \ ({\sf record}) \\ {\sf DOWNSAMPLE} \rightarrow {\sf SPI\_OUT} \ ({\sf feed-through} \ {\sf SPI}) \\ {\sf DECOMPRESS} \ \rightarrow {\sf SPI\_OUT} \ ({\sf SPI} \ {\sf playback}) \\ {\sf DECOMPRESS} \ \rightarrow {\sf UPSAMPLE} \ ({\sf Playback}) \\ \end{array}$

Figure 7-7 Digital Signal Path

#### 8 ISD3900 MEMORY MANAGEMENT

The ISD3900 employs several memory management techniques to make audio recording and playback transparent to the host controller. The address space of the ISD3900 starts at address zero of the external memory. This external memory size can range from 1M to 128M with an erasable sector size of 4kBytes. Please note that Digital Read and Digital Write commands can access up to 64Mbit (0x000000 ~ 0x7FFFFF), while Play, Record, and Erase commands can access up to 128Mbit (0x000000 ~ 0xFFFFFF). The following sections will describe the ISD3900 memory management architecture and the message management functions.

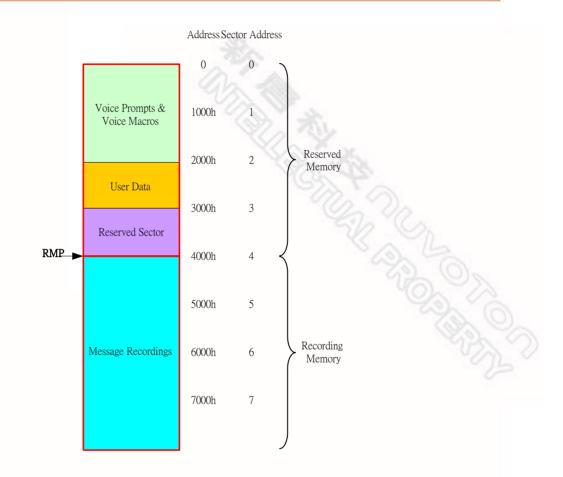

#### 8.1 ISD3900 MEMORY FORMAT

The Recording Memory Pointer (RMP) divides the ISD3900 memory address space into two blocks, Reserved Memory and Recording Memory. The RMP is a two-byte address pointer pointing to a 4kByte memory sector which is the first sector available to users for recording messages. Memory between address zero and the RMP pointer is considered the Reserved Memory for pre-recorded audio (Voice Prompts), pre-programmed macro scripts (Voice Macros), digital read/write access for other applications (User Data) and memory sectors reserved for the first sector of the message recordings and re-recordable pre-recorded messages (Reserved Sectors). The memory between the RMP and the end of memory is considered the Recording Memory allocated for recording messages (Message Recordings).

Figure 8-1 illustrates the memory format with the RMP set at address 4000h or sector 4. Section 8.3 will provide more detail regarding the setting of the RMP.

Figure 8-1 ISD3900 Memory Format

#### 8.2 MESSAGE MANAGEMENT

nuvoton

The message management schemes implemented on the ISD3900 are:

- 1. Voice Prompts: A collection of pre-recorded audio that can be played back using the PLAY\_VP SPI command or Voice Macros.

- 2. Voice Macros: A powerful voice script allowing users to create custom macros to play Voice Prompts, play message recordings, insert silence and configure the device. Voice Macros are executed with a single SPI command.

- 3. User Data: Memory sectors defined and allocated by the users for use in other applications

- 4. Reserved Sectors: Memory sectors reserved for the first sector of the message recordings (Empty Message) and re-recordable pre-recorded messages (Re-recordable Message).

- 5. Message Recordings: Messages recorded, played and erased "on the fly" by the users.

#### 8.2.1 Voice Prompts

Voice prompts are pre-recorded audio of any length, from short words, phrases or sound effects to long passages of music. These Voice Prompts can be played back in any order as determined by the users and applications. A Voice Prompt consists of two components:

- 1. An index pointing to the pre-recorded audio

- 2. Pre-recorded audio

To play a Voice Prompt, the ISD3900 use the index of the Voice Prompt to locate and play the pre-recorded audio. This approach allows users to easily manage the pre-recorded audio without the need to update the code on the host controller. In addition, the users can store a multitude of pre-recorded audio without the overhead of maintaining a complicated lookup table. To assist customers in creating the Voice Prompts, a software tool, the ISD3900 Voice Prompt Editor and writer are available for development purposes.

#### 8.2.2 Voice Macros

Voice Macros are a powerful voice script that allows users to customize their own play patterns such as play Voice Prompts, play message recordings, insert silence, change the master sample clock, power-down the device and configure the signal path, including gain and volume control. Voice Macros are executed using a single SPI command and are accessed using the same index structure as Voice Prompts. This means that a Voice Macro (or Voice Prompt) can be updated on the ISD3900 without the need to update code on the host micro-controller since absolute addresses are not needed.

The following locations have been reserved for two special Voice Macros: Index 0: Power-On Initialization (POI) Index 1: Power-Up (PU)

These Voice Macros allow the users to customize the ISD3900 power-on and power-up procedures and are executed automatically when utilized. The built-in voice macros will be used when they are not utilized. Please see Section 11 for details.

Here is an example to illustrate the usage of the PU Voice Macro.

- SET\_CLK\_CFG(0x37)

- WR\_CFG\_REG(0x05,0x01)

- WR\_CFG\_REG (0x06,0x02)

- FINISH

The above PU Voice Macro will perform the following:

- Choose a 2.048MHz crystal as a clock source

- Set up a feed-through path from ANAIN to AUDOUT

The following is the complete list of the commands for Voice Macro:

- SET\_CLK\_CFG(n) Set clock configuration register to n.

- WR\_CFG\_REG(reg,n) Set configuration register reg to value n.

- PWR\_DN Power down the ISD3900.

- PLAY\_VP(i) Play Voice Prompt index i.

- PLAY\_MSG@(sec-addr) Play message starting at sector address sec-addr

- PLAY\_SIL(n) Play silence for n units. A unit is 32ms at master sampling rate of 32 kHz.

- WAIT\_INT Wait until current play command finishes before executing next macro instruction.

- FINISH Finish the voice macro and exit.

#### 8.2.3 User Data

User Data consist of 4kByte chunks of erasable sectors defined and allocated by the users for use in other applications. The users have the freedom not to allocate or reserve any memory sectors. A software tool, the ISD3900 Voice Prompt Editor is available to assist customers in allocating such memory.

#### 8.2.4 Reserved Sectors

Reserved sectors consist of 4kByte chunks of erasable sectors reserved for the Empty Messages and Re-recordable Messages. The Empty Message is an empty sector made of a 4kByte memory sector reserved for message recordings. A SPI record command pointing to the Empty Message starts the message recording into the Empty Message and will continue to record messages in the free memory located in Recording Memory if the message recording is over 4kBytes. The users can send a play, erase or record command pointing to the Empty Message to play, erase the entire message or re-record a brand new message.

The Re-recordable Message, a 4kByte memory sector contains message recordings and a sector address pointer (see Section 8.3 for details) pointing to the message sector located in Recording Memory. Unlike the Empty Message where no message has been recorded, the users can play back a complete message by issuing a SPI play command pointing to the Re-recordable Message. The users can also send an erase or record command pointing to the Re-recordable Message to erase the entire message or re-record a brand new message.

#### 8.2.5 Message Recordings

Message Recordings are messages that can be recorded, played and erased "on the fly" by the users. These messages are recorded in 4kByte chunks of erasable sectors with each message sector containing a header pointing to the next message sector. The ISD3900's unique message management architecture allows users to record messages without specifying an address. The ISD3900 will start recording at the first available sector in Recording Memory and continue to record into free memory until memory is full or a STOP command is issued. Upon completion of the record operation, the users need to read back the message sector start address for subsequent playback.

To playback the message recordings, the users need to send a play command pointing to the message sector start address. For partial message playback, the users can send a play command with a sector offset.

To erase the message recordings, the users need to send an erase command pointing to the message sector start address.

A list of commands for Message Recordings are detailed below:

- REC\_MSG starts a record operation.

- STOP stops current record operation.

- READ\_STATUS wait until record operation is finished as indicated by the CMD\_FIN bit.

- READ\_INT clear the interrupt.

- READ\_MSG\_ADD This command returns a three byte starting address (A) of the message along with a two byte sector length. Use A to address the message in subsequent playback operations.

- PLAY\_MSG@(A) Play back the message.

- READ\_STATUS poll status until CMD\_FIN bit is set indicating play has finished.

- READ\_INT clear the interrupt.

- ERASE\_MSG@(A) erase the message.

- READ\_STATUS poll status until CMD\_FIN bit is set indicating erase has finished.

- READ\_INT clear the interrupt.

#### 8.3 MEMORY AND MESSAGE HEADERS

The Memory and Message headers are located at the initial bytes of the 4kByte memory sector used to determine the format or function of the memory. The Memory Header stores users' configurable information including the memory protection scheme, the RMP and PMP pointers and the index table including POI, PU and other Voice Macros defined by the users. The Message Header located in both Reserved Sectors and Recording Memory stores the information for the device to determine what memory is available for recording and where the subsequent messages are stored.

#### 8.3.1 Memory Header

| Initial Bytes of the Memory Header |                                                                |          |        |       |          |          |  |

|------------------------------------|----------------------------------------------------------------|----------|--------|-------|----------|----------|--|

| Byte0                              | Byte0 Byte1-2 Byte3-4 Bytes5-10 Bytes11-16 Byte17-22 Byte23-28 |          |        |       |          |          |  |

| 0xCX                               | RMP[7:0]                                                       | PMP[7:0] | POI_VM | PU_VM | VM/VP[2] | VM/VP[3] |  |

Table 8-1Memory Header

The Memory Header contains at least seventeen bytes located at the beginning of the memory space. Byte0 determines whether or not the memory contains a Reserved Memory block as well as the memory protection scheme is used. Byte1-2 and Byte3-4 store the RMP and PMP pointers respectively. After the PMP, it is the start of the Voice Prompt/Voice Macro index table defined by the users. This table consists of six byte entries that are the start and end address of Voice Prompt or Voice Macro. Byte5-10 & Byte11-15 are reserved for the POI and PU Voice Macro which are the first two entries in this table (index 0 and index 1) to be executed on power-on initialization and power-up respectively. If this function is not desired, these entries should be left erased (0xFFFFFF,0xFFFFFF). When a PLAY\_VP(i) or

EXE\_VM(i) command is sent to the ISD3900, it reads the index table entry at address 6i+5 and executes the VP or VM at the address present in the table.

If the first byte Byte0 of the memory header is 0xFF, it means that no Reserved Memory is allocated, no memory protection is enabled and the whole memory will be available for record and playback only. To allocate the Reserve Memory, the bit4 of the Byte0 has to be set to zero. When Reserved Memory is allocated and memory protection is enabled upon users' definition, the both RMP (Recording Memory Pointer) and PMP (Protected Memory Pointer) will then created and stored at Byte1-2 and Byte3-4 of the Memory Header respectively. The ISD3900 will not attempt to use memory before the RMP for message recordings. This memory thus can be used for Voice Prompts, Voice Macros, User Data and Reserved Sectors. The PMP points to the boundary of protected memory and is used in conjunction with the RP, WP and CEP bits to set memory protection indicated below (also see Section 8.6 for details).

| Memory Header Byte |       |       |       |       |       |       |       |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7              | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 1                  | 1     | 0     | 0     | 1     | RP    | WP    | CEP   |

|  | Table 8-2 | The first by | yte of the | Memory | / Header |

|--|-----------|--------------|------------|--------|----------|

|--|-----------|--------------|------------|--------|----------|

#### 8.3.2 Message Header

Table 8-3 Message Header

| Message Header Byte |       |       |       |       |       |       |       |

|---------------------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7               | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| BOM                 | EOM   | RSVD  | -     | -     | -     | -     | -     |

The ISD3900 adopts a sector-based message management scheme that treats each 4kByte sector as a message frame. Each sector has a header indicating the state of the frame:

- BOM: "0" indicates that this sector is the beginning of a message.

- EOM: "0" indicates that this sector is the end of a message.

- RSVD: "0" indicates that there is a message recorded in this sector or this sector has been reserved for User Data.

Thus the number of the BOMs counted by scanning the Message Header of the Recording Memory will tell the number of the messages recorded in the ISD3900.

When a sector is not an EOM sector, the next two bytes in the frame are the sector address pointing to the subsequent message. Thus the whole message can be re-composed by tracing sector address until an EOM is found.

It is not recommended to reserve the User Data inside the Recording Memory. However, for those instances where User Data needs to be allocated inside the Recording Memory, it is

imperative that the RVSD has set and maintained at "0". Otherwise, there is a risk that the User Data may be over-written by subsequent recordings.

#### 8.4 DIGITAL ACCESS OF MEMORY

ISD3900 memory can be accessed as conventional digital memory using the DIG\_READ and DIG\_WRTIE SPI commands. This allows the user to:

- Reserve areas of memory for use as digital non-volatile memory as User Data

- Update Voice Prompts and macros (pre-recorded audio) in system.

- Read and verify Voice Prompt memory.

- Read sector headers of memory to determine memory usage.

The digital read and write commands can be issued even while an audio record or playback is in progress. The RDY/BSYB pin governs the flow control for all digital operations.

#### 8.5 DEVICE ERASE COMMANDS

ISD3900 provides several ways to erase the flash memory. The flash memory has a minimum erasable sector size of 4kBytes. The sector erase command is sent with a start and stop sector address. The ISD3900 also has commands to mass erase the memory.

#### 8.6 MEMORY CONTENTS PROTECTION

Under certain circumstances, it is desirable for the users to protect portions of the external memory from write/erase or interrogation (read). The ISD3900 provides a method to achieve this by setting a protection memory pointer (PMP) that allows the users to protect external memory for an address range from the beginning of memory to this sector where PMP is pointed. The type of protection is set by three bits in the memory header byte.

- The **CEP** (Chip Erase Protect) bit set to zero enables chip erase protection. This prevents a mass erase function, allowing the device to be configured as a write-once part. With the **CEP** bit set to one, even with write protection enabled, the part can be mass erased. After mass erasure, the initial sector byte defaults to no protection so the device can be re-programmed.

- The **WP** (Write Protect) bit set to zero enables write protection of the external memory below the sector pointed to by the PMP. Write protection means that digital write or erase commands will not function in this memory area. This can be used to ensure that audio or data is not inadvertently erased or overwritten. The **WP** bit does not stop the execution of a REC\_MSG@ or ERASE\_MSG@ to messages with BOM headers in this memory.

- The **RP** (Read Protect) bit set to zero enables read protection of the external memory below the sector pointed to by the PMP. Read protection means that digital read or audio playback commands through SPI or I<sup>2</sup>S will not function in this memory area. This can be used to ensure that external memory contents cannot be digitally copied or read.

Memory protection is activated on power-up of the chip. Therefore, each time the user changes the setting of memory protection, the new setting will not be effective until the chip is reset.

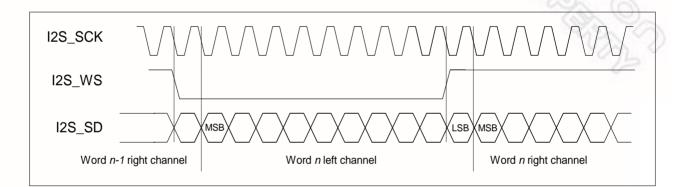

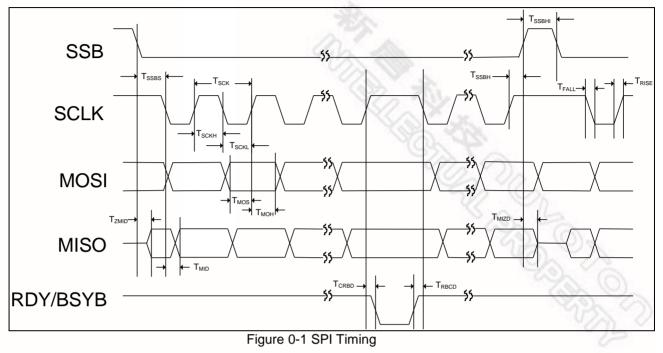

### 9 I<sup>2</sup>S INTERFACE

The I<sup>2</sup>S interface is a digital audio interface that allows the transfer of the audio data between other digital audio devices such as multimedia processors, audio amplifiers or DSPs. The ISD3900 acts as either a master or a slave device on an I<sup>2</sup>S bus. As a slave the ISD3900 accepts SCK and WS clock and frame signals from a bus master. In master mode the ISD3900 generates SCK and WS. It is capable of both data input and output depending upon configuration. The ISD3900 is configurable to accept data from either the left or right audio channel or a mono mix of both. It can output data to either the left, right or both channels. It is also capable of feeding through a stereo signal and mixing a playback operation into the signal. In slave mode, to synchronize data transfer, the ISD3900 must derive its master clock from the I<sup>2</sup>S SCK or be operating from a synchronous external clock source.

I<sup>2</sup>S is for high bandwidth audio input/output. High bandwidth audio input comes either from the ADC path or the I<sup>2</sup>S. High bandwidth audio output goes out on the DAC, I<sup>2</sup>S or PWM driver paths. It all depends on how you configure the path. However, commanding the ISD3900 is through SPI commands. For instance, the user could configure the path, through the SPI commands, as: "I<sup>2</sup>S input -> ADPCM-4bit Compression -> Memory Control", then the user can feed the audio data from I<sup>2</sup>S.

Figure 9-1 I<sup>2</sup>S Protocol

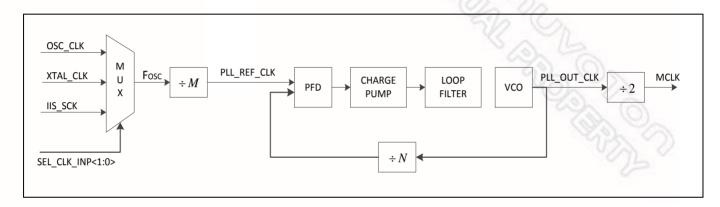

#### **10 CLOCK GENERATION**

The ISD3900 can derive its master clock from five sources:

- 1. An external crystal (or resonator) oscillator interface.

- 2. An external clock input (applied to pin XTALIN and left the XTALOUT unconnected)

- 3. An internal oscillator controlled by an external resistor (attached to pin XTALIN and GND).

- 4. An internal oscillator with internal reference.

- 5. The SCK clock of the  $I^2S$  interface.

Regardless of source, the selected clock is fed to a phase-locked loop (PLL) to generate the internal master clock (MCLK) of the ISD3900.

Figure 10-1 PLL Clock Generation on ISD3900

The goal of clock generation is to generate a master clock rate (MCLK) at 512x the master sample rate (Fs). A table of supported master clock and sample rates is shown below. The master sample frequency can be expressed by the formula:

$$F_{MCLK} = F_{OSC} \frac{N}{2M}$$

where  $M = \{1, 2, 3\}$  and  $N = \{8, 16, 32\}$

$$F_s = F_{MCLK} \frac{1}{512}$$

Table 10-1 Master Clock and Sample Rates

| MCLK (MHz) | Fs (kHz) |

|------------|----------|

| 16.384     | 32       |

| 24.576     | 48       |

| 22.5792    | 44.1     |

For the above master sample rates, Fs, record and playback is available at fixed ratios of the master sample rate.

| Sub-          | Master S |        |      |                         |

|---------------|----------|--------|------|-------------------------|

| Sampled ratio | 32       | 44.1   | 48   |                         |

| 8             | 4        | 5.5125 | 6    | Av                      |

| 6             | 5.333    | 7.35   | 8    | Available               |

| 5             | 6.4      | 8.82   | 9.6  | ble :                   |

| 4             | 8        | 11.025 | 12   | San<br>kHz              |

| 2.5           | 12.8     | 17.64  | 19.2 | )<br>)                  |

| 2             | 16       | 22.05  | 24   | e Sample Rates<br>(kHz) |

| 1             | 32       | 44.1   | 48   | tes                     |

Table 10-2 Sub-Sample Rates available.

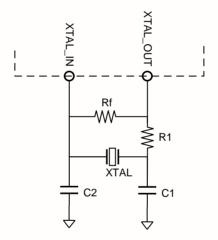

#### 10.1 EXTERNAL CRYSTAL OSCILLATOR

The external circuit for attaching a quartz crystal or ceramic resonator is shown in Figure 10-2. In this circuit, Rf is several M $\Omega$  and is used to DC bias the internal amplifier. R1, C1 and C2 are chosen so as not to overdrive the crystal and to suppress oscillation at higher crystal harmonics.

Figure 10-2 Crystal Oscillator

Some common crystal frequencies to achieve desired Fs are shown in Table 10-3.

### nuvoton

| Xtal (MHz) | М | Ν  | Fs (kHz) |

|------------|---|----|----------|

| 1.024      | 1 | 32 | 32       |

| 2.048      | 2 | 32 | 32       |

| 3.072      | 3 | 32 | 32       |

| 4.096      | 2 | 16 | 32       |

| 6.144      | 3 | 16 | 32       |

| 8.192      | 2 | 8  | 32       |

| 12.288     | 3 | 8  | 32       |

| 1.4112     | 1 | 32 | 44.1     |

| 2.8224     | 2 | 32 | 44.1     |

| 4.2336     | 3 | 32 | 44.1     |

| 5.6448     | 2 | 16 | 44.1     |

| 8.4672     | 3 | 16 | 44.1     |

| 11.2896    | 2 | 8  | 44.1     |

| 16.9344    | 3 | 8  | 44.1     |

| 1.536      | 1 | 32 | 48       |

| 3.072      | 2 | 32 | 48       |

| 4.608      | 3 | 32 | 48       |

| 6.144      | 2 | 16 | 48       |

| 9.216      | 3 | 16 | 48       |

| 12.288     | 2 | 8  | 48       |

| 18.432     | 3 | 8  | 48       |

Table 10-3 Common Crystal Frequency Settings

In addition to the above crystals, to achieve standard audio sampling rates, other frequencies could be used that would produce different sample rates. For instance if the user wishes to use the standard USB clock rates of 6 or 12MHz the following master sample rates could be achieved.

| Xtal (MHz) | М | Ν  | Fs (kHz) |

|------------|---|----|----------|

| 12         | 2 | 8  | 46.875   |

| 12         | 3 | 8  | 31.25    |

| 6          | 3 | 16 | 31.25    |

| 6          | 2 | 16 | 46.875   |

Table 10-4 USB Crystal Master Sample Rates

### nuvoton

#### 10.2 I<sup>2</sup>S CLOCK USAGE

The SCK clock of the I<sup>2</sup>S interface must be used to synchronize the ISD3900 if an I<sup>2</sup>S interface is used. The ISD3900 accepts I<sup>2</sup>S\_SCK clock rates of 32xFs or 64xFs.

| I <sup>2</sup> S_SCK (MHz) | М | Ν  | Fs (kHz) |

|----------------------------|---|----|----------|

| 1.024                      | 1 | 32 | 32       |

| 2.048                      | 2 | 32 | 32       |

| 1.4112                     | 1 | 32 | 44.1     |

| 2.8224                     | 2 | 32 | 44.1     |

| 1.536                      | 1 | 32 | 48       |

| 3.072                      | 2 | 32 | 48       |

|                            |   |    |          |

| Table 10-5 Supporte | d I <sup>2</sup> S Clock Rates with PLI | Settings  |

|---------------------|-----------------------------------------|-----------|

|                     |                                         | - Octango |

#### 10.3 INTERNAL OSCILLATOR

The ISD3900 also provides an internal oscillator. For reference the internal oscillator uses an internal resistor or an external resistor. If the device is configured to use internal oscillator with external resistor, then the resistor should be connected between XTALIN pin and GND. The internal oscillator with external resistor has an accuracy of  $\pm 5\%$  and gives a master sample rate of:

$F_s = \frac{32 \times 80 \times 10^3 \times \alpha}{R_{osc}} \text{ (kHz) for } M = 2, N = 32, \alpha = 0.98375$

So if the user connects an 78.7kohm resistor to the XTALIN and GND, a 32 kHz sample frequency is fed-through the analog path.  $\alpha$  is the adjustment factor which has value of 0.98375.

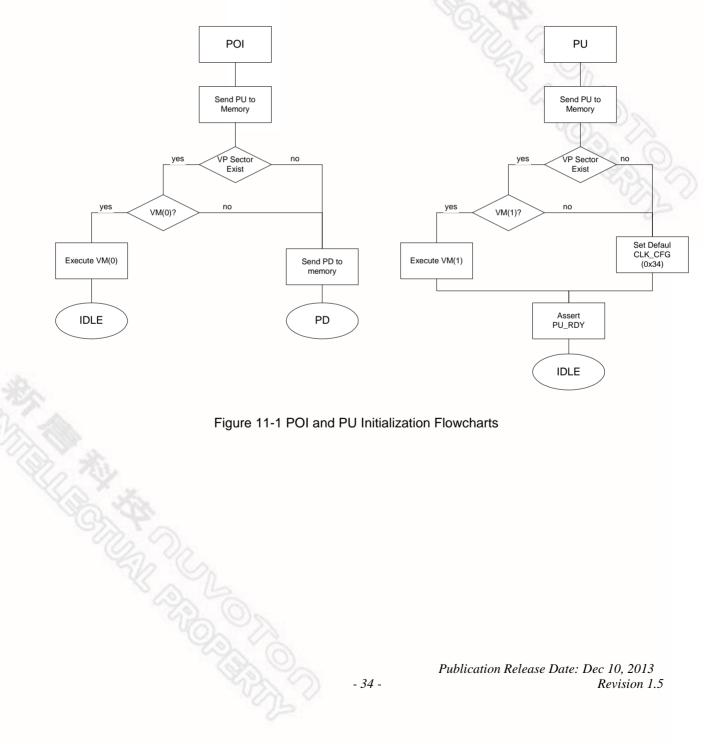

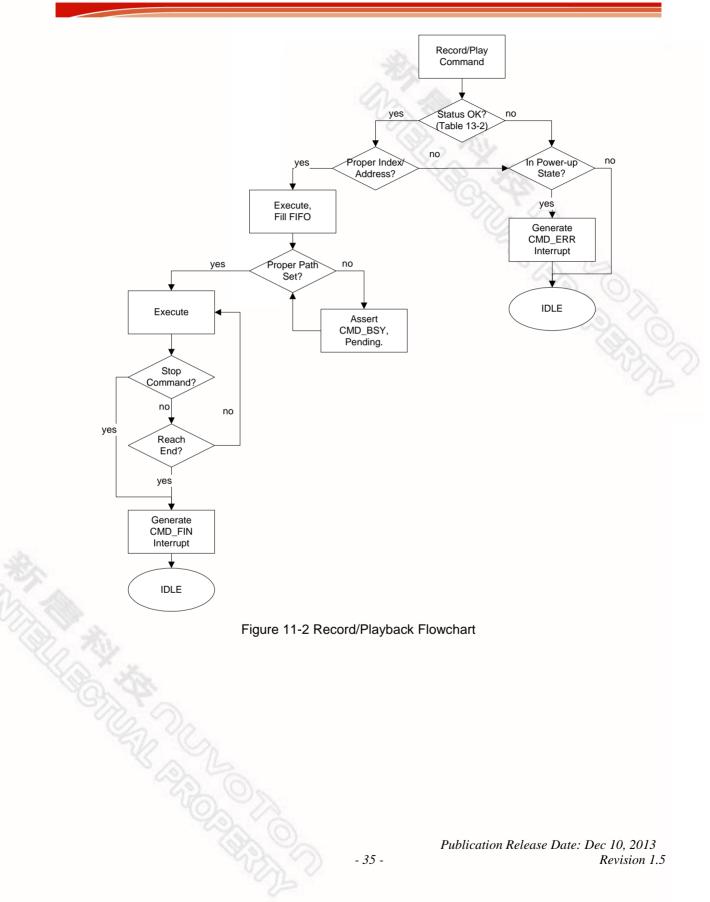

#### 11 INITIALIZATION & RECORD/PLAY FLOWCHART

Whenever the ISD3900 detect as power-on reset condition or a high on the RESET pin of the device it begins a power-on initialization (POI) sequence. Whenever the ISD3900 receives a power up command (PU) when it is in a power down state, it begins a power-up initialization (PU) sequence. Voice Macros VM(0) and VM(1) are reserved for POI and PU initialization routines. If no reserved memory exists or if the vectors VM(0) or VM(1) are not set, then a default routine is executed. The default sequence for POI is to power-down the ISD3900. The default PU sequence is to select a clock configuration of internal oscillator with PLL active for Fs=32kHz.

ηυνοτοη

#### 12 DEVICE CONFIGURATION AND STATUS

#### 12.1 CLOCK CONFIGURATION

The clock configuration register is accessed via the SET\_CLK\_CFG command. It configures the clock source of the ISD3900. The default state of the clock configuration register is0x34, that is internal clock with internal reference, PLL active for 32kHz sample rate and no external clock output. When PLL\_BYPASS is set, the PLL is powered down and PLL\_REF\_CLK is fed directly to MCLK. The CLK\_OUT control bits configure the I<sup>2</sup>S clock pin, SCK, as a clock output to allow the ISD3900 to provide an oscillator output to another device such as the host microcontroller.

| Table 12-1 Clo | ock Configuratior | Register | Description |

|----------------|-------------------|----------|-------------|

|                |                   |          |             |

| CLK_CFG |         |        |          |        |          |          |          |

|---------|---------|--------|----------|--------|----------|----------|----------|

| Bit 7   | Bit 6   | Bit 5  | Bit 4    | Bit 3  | Bit 2    | Bit 1    | Bit 0    |

| CLK_O   | UT[1:0] | CLK_N_ | DIV[1:0] | CLK_M_ | DIV[1:0] | CLK_INP_ | SEL[1:0] |

| 0       | 0       | 1      | 1        | 01     | 1        | 00       | Ca la    |

Default 0x34:

- Internal clock with internal reference

- PLL active for F<sub>s</sub>=32khz sample rate

- No external clock output

#### Table 12-2 Clock Configuration Source

| CLK_INP_SEL      |                                             |  |  |  |

|------------------|---------------------------------------------|--|--|--|

| CLK_INP_SEL[1:0] | Clock Source                                |  |  |  |

| 00               | Internal Oscillator with Internal Reference |  |  |  |

| 01               | IIS SCK Clock                               |  |  |  |

| 10               | Internal Oscillator with Rext               |  |  |  |

| 11               | XTAL Interface                              |  |  |  |

#### Table 12-3 Clock PLL M Divisor

| CLK_M_DIV        |     |  |  |  |

|------------------|-----|--|--|--|

| CLK_M_DIV[1:0] M |     |  |  |  |

| 00               | 1   |  |  |  |

| 01               | 2   |  |  |  |

| 10               | 3   |  |  |  |

| 11               | N/A |  |  |  |

| CLK_N_DIV |                |  |  |  |  |

|-----------|----------------|--|--|--|--|

| N         | CLK_N_DIV[1:0] |  |  |  |  |

| _BYPASS   | 00             |  |  |  |  |

| 8         | 01             |  |  |  |  |

| 16        | 10             |  |  |  |  |

| 32        | 11             |  |  |  |  |

|           | 11             |  |  |  |  |

#### Table 12-4 Clock PLL N Divisor

#### Table 12-5 External Clock Output

| EXT Clock    |             |  |  |  |  |

|--------------|-------------|--|--|--|--|

| CLK_OUT[1:0] |             |  |  |  |  |

| 00           | NONE – OFF  |  |  |  |  |

| 01           | Fosc        |  |  |  |  |

| 10           | PLL_REF_CLK |  |  |  |  |

| 11           | MCLK        |  |  |  |  |

#### 12.2 DEVICE STATUS REGISTER

Whenever the ISD3900 receives an SPI command it also returns its current status via MISO. The details of the status byte are shown below. For commands that are not reading digital data from the device this status byte is sent via MISO for every byte of data sent to the ISD3900.

| Table 12-6 Status Register Description |

|----------------------------------------|

|----------------------------------------|

| Status Byte |          |       |        |       |        |          |         |  |

|-------------|----------|-------|--------|-------|--------|----------|---------|--|

| Bit 7       | Bit 6    | Bit 5 | Bit 4  | Bit 3 | Bit 2  | Bit 1    | Bit 0   |  |

| PD          | DBUF_RDY | INT   | RM_FUL | -     | VM_BSY | CBUF_FUL | CMD_BSY |  |

The individual bits of the status register refer to the following conditions:

- **PD** If this bit is high then the device is powered down. The DBUF\_RDY bit will be low, but all device output pins will be high impedance. When PD is high only the READ\_STATUS, READ\_INT and PWR\_UP commands are accepted. If any other command is sent, it is ignored and no interrupt for an error is generated.

- **DBUF\_RDY** in PD this bit is low indicating the device can only accept a PWR\_UP (power up) command. When PD is low this bit reflects the state of the RDY/BSY pin.

- **INT** an interrupt has been generated. The interrupt is cleared by the READ\_INT command. Interrupt type can be determined by the bits of the Interrupt Status Byte.

- **RM\_FUL** Recording Memory is full. This bit will be set if a record command fills the memory. This bit is reset by an ERASE\_MSG@, ERASE\_MEM, or CHIP\_ERASE operation.

- VM\_BSY indicates the device is processing a voice macro. The device will not respond to a

new audio command until this bit returns low.

- **CBUF\_FUL** indicates that the command buffer is full. No more commands can be queued for execution until this bit returns low.

- **CMD\_BSY** indicates the device is processing a command. Device will not respond to a new command until this bit returns low. If CMD\_BSY=1 and CBUF\_FUL=0 and VM\_BSY=0, a new command will go into the command buffer and execute when the current command finishes. If CMD\_BSY=1 and CBUF\_FUL=1 or VM\_BSY=1 any new audio command will be ignored and generate a command error. For erasing commands like ERASE\_MSG@, ERASE\_MEM and CHIP\_ERASE, the user has to poll this bit to see if the erasing is done.

Whenever the ISD3900 generates an interrupt the Interrupt Status register holds flags that indicate what type of interrupt was generated. These flags will remain set until a READ\_INT command clears them and the interrupt pin.

|        | Interrupt Status Byte |        |         |         |         |          |          |  |

|--------|-----------------------|--------|---------|---------|---------|----------|----------|--|

| Bit 7  | Bit 6                 | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1    | Bit 0    |  |

| PK_INT | MPT_ERR               | WR_FIN | CMD_ERR | OVF_ERR | CMD_FIN | ADDR_ERR | FULL_ERR |  |

Table 12-7 Interrupt Status Register Description

The individual bits of the status register refer to the following conditions:

**INT** – an interrupt has been generated. The interrupt is cleared by the READ\_INT command.

- **PK\_INT** Indicates a peak detection interrupt has occurred. Input peak detector can be configured to generate an interrupt when signal level exceeds a certain threshold.

- MPT\_ERR Indicates a memory protection error. Digital access attempted for protected memory.

- WR\_FIN indicates a digital write command has finished writing to the flash memory.

- **CMD\_ERR** an invalid command was sent to the device. Command was ignored because the command buffer was full, a voice macro was active or the device was not ready to respond to an erase command.

- OVF\_ERR This error is generated if host illegally tries to read or write data while RDY/BSYB pin is low. It is also generated if a digital read or write attempts to read or write past the end of memory.

- CMD\_FIN This bit indicates an interrupt was generated because a command finished executing. A CMD\_FIN interrupt will be generated each time an audio play, record or voice macro finishes.

- ADDR\_ERR Indicates an address error. This bit will be set to one if a PLAY\_MSG@ command is sent at a non-valid header, a REC\_MSG@ is sent at a non-blank memory location or an ERASE\_MSG command is sent to a sector that is not the beginning of message.

- **FULL\_ERR** Record Block is full. This bit will be set and an interrupt generated if a record command fills the memory.

#### 12.3 DEVICE CONFIGURATION REGISTERS

The configuration of the ISD3900 is achieved by forty-eight configuration registers, CFG0-CFG2F as detailed below.

Please note that registers 0x19-0x1F have no default value, and user should configure these registers in both POI VM and PU VM to customized value or suggested initial value to avoid undesired consequences. See register 0x19 - 0x1F configuration for details.<sup>2</sup>

| CFG0 Configuration Register |         |       |          |       |       |       |       |  |  |

|-----------------------------|---------|-------|----------|-------|-------|-------|-------|--|--|

| Bit 7                       | Bit 6   | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|                             | SR[2:0] |       | CMP[4:0] |       |       |       |       |  |  |

|                             | 011     |       | 00100    |       |       |       |       |  |  |

Table 12-8 CFG0 Register

Default 0x64:

- 4-bit ADPCM

- Ratio to Fs = 4

ISD provides a powerful software tool, Voice Prompt Editor, to help the user build their project and ease the configuration of the ISD3900.

Configuration register CFG0 controls the sample rate and compression algorithm during message record operations. It can also override sample rate setting for playback by setting bit 0 of CFG1 high. SR[2:0]=CFG0[7:5] controls the sample rate and CMP[4:0]=CFG0[4:0] controls the compression. An explanation of these follows below.

| Compression | Bit rate      | СМР   | [4:0] |

|-------------|---------------|-------|-------|

| Туре        | (bits/sample) | (Dec) | (Hex) |

| ADPCM       | 2             | 2     | 0x02  |

| ADPCM       | 3             | 3     | 0x03  |

| ADPCM       | 4             | 4     | 0x04  |

| ADPCM       | 5             | 5     | 0x05  |

| µ-Law       | 6             | 16    | 0x10  |

| µ-Law       | 7             | 17    | 0x11  |

| µ-Law       | 8             | 18    | 0x12  |

| Dµ-Law      | 6             | 20    | 0x14  |

| 152         |               |       |       |

<sup>2</sup> Note: Register 0x1C and 0x1E are excluded because register 0x1C is read-only and register 0x1E doesn't exist.

### nuvoTon

| Dµ-Law     | 7       | 21       | 0x15         |

|------------|---------|----------|--------------|

| Dµ-Law     | 8       | 22       | 0x16         |

| PCM        | 8       | 24       | 0x18         |

| PCM        | 10      | 25       | 0x19         |

| PCM        | 12      | 27       | 0x1B         |

| PCM<br>PCM | 8<br>10 | 24<br>25 | 0x18<br>0x19 |

| Ratio | Sample Rate (kHz) | Code    | CFG0[7:0] |       |  |

|-------|-------------------|---------|-----------|-------|--|

| to Fs | (for Fs=32kHz)    | SR[2:0] | (Dec)     | (Hex) |  |

| 8     | 4                 | 0       | 0         | 0x00  |  |

| 6     | 5.333             | 1       | 32        | 0x20  |  |

| 5     | 6.4               | 2       | 64        | 0x40  |  |

| 4     | 8                 | 3       | 96        | 0x60  |  |

| 2.5   | 12.8              | 4       | 128       | 0x80  |  |