**NUC505**

ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit Microcontroller

# NuMicro<sup>®</sup> Family NUC505 Series Technical Reference Manual

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

#### TABLE OF CONTENTS

| 1 | GEN  | ERAI  | L DESCRIPTION                                              |

|---|------|-------|------------------------------------------------------------|

| 2 | FEAT | FURE  | ES                                                         |

|   | 2.1  | NUC   | 505 Features                                               |

| 3 | ABBF | REVI  | ATIONS                                                     |

|   | 3.1  | Abbr  | eviations19                                                |

| 4 | PAR1 | TS IN | IFORMATION LIST AND PIN CONFIGURATION                      |

|   | 4.1  | Sele  | ction Guide20                                              |

|   | 4.   | 1.1   | NuMicro <sup>®</sup> NUC505 Base Series Selection Guide    |

|   | 4.   | 1.2   | NuMicro <sup>®</sup> NUC505 Base Series Naming Rule        |

|   | 4.2  | Pin C | Configuration                                              |

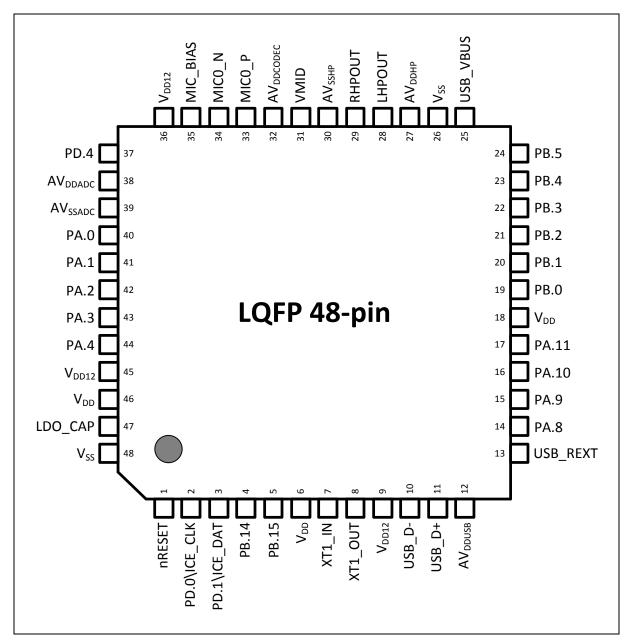

|   | 4.   | 2.1   | NuMicro <sup>®</sup> NUC505DLA LQFP 48-pin                 |

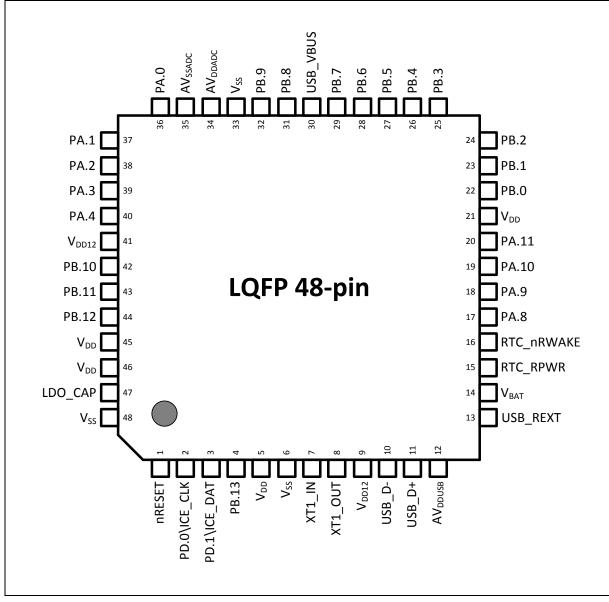

|   | 4.   | 2.2   | NuMicro <sup>®</sup> NUC505DL13Y LQFP 48-pin23             |

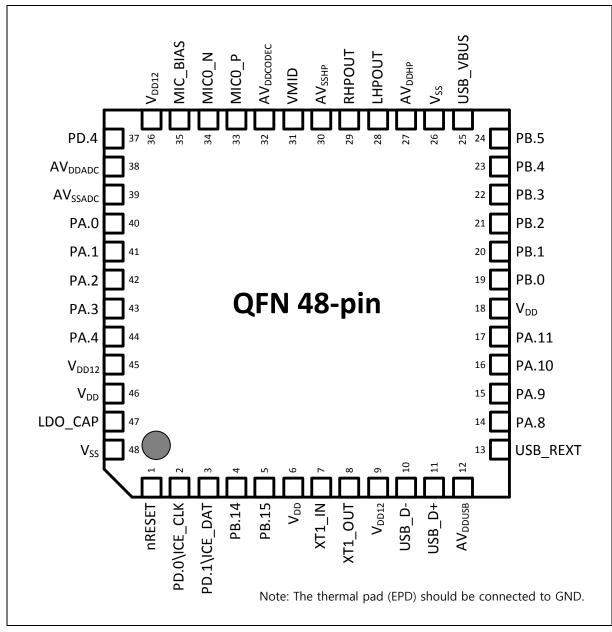

|   | 4.   | 2.3   | NuMicro <sup>®</sup> NUC505YLA QFN 48-pin                  |

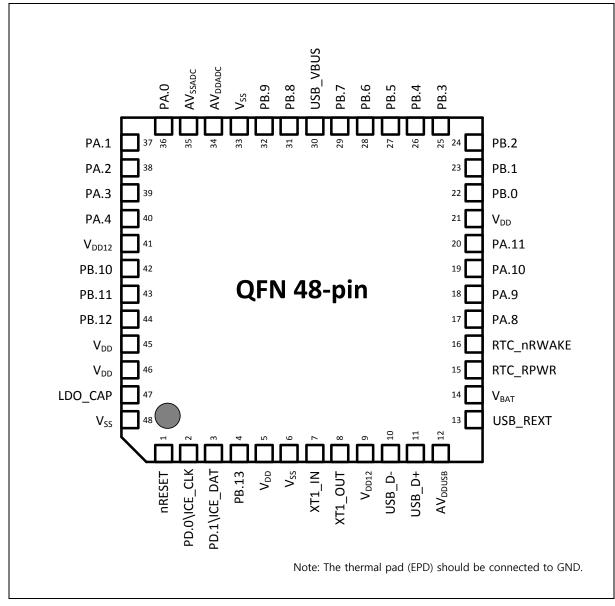

|   | 4.   | 2.4   | NuMicro <sup>®</sup> NUC505YLA2Y QFN 48-pin25              |

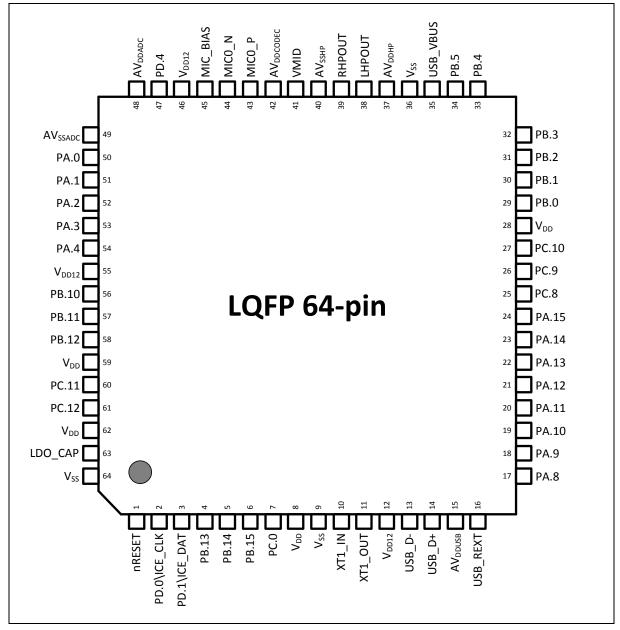

|   | 4.   | 2.5   | NuMicro <sup>®</sup> NUC505DSA LQFP 64-pin                 |

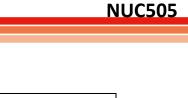

|   | 4.   | 2.6   | NuMicro <sup>®</sup> NUC505DS13Y LQFP 64-pn27              |

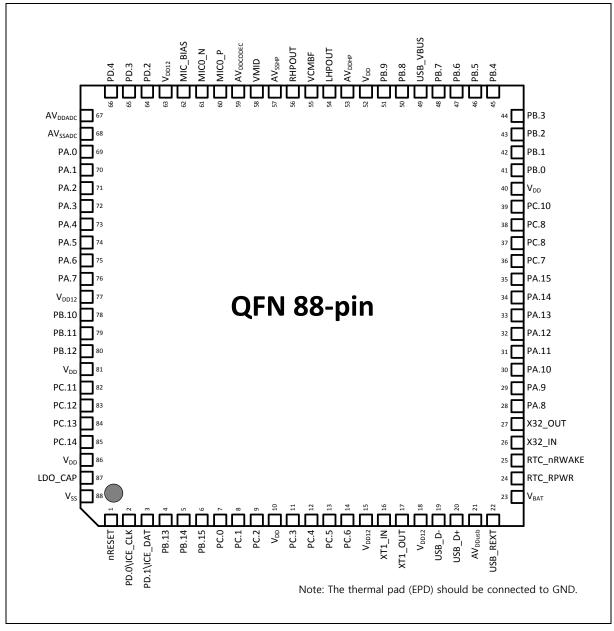

|   | 4.   | 2.7   | NuMicro <sup>®</sup> NUC505YO13Y QFN 88-pin                |

|   | 4.3  | Pin D | Description                                                |

|   | 4.   | 3.1   | NuMicro <sup>®</sup> NUC505DLA LQFP 48-pin Description     |

|   | 4.   | 3.2   | NuMicro <sup>®</sup> NUC505DL13Y LQFP 48-pin Description   |

|   | 4.   | 3.3   | NuMicro <sup>®</sup> NUC505YLA QFN 48-pin Description      |

|   | 4.   | 3.4   | NuMicro <sup>®</sup> NUC505YLA2Y QFN 48-pin Description    |

|   | 4.   | 3.5   | NuMicro <sup>®</sup> NUC505DSA LQFP 64-pin Description     |

|   | 4.   | 3.6   | NuMicro <sup>®</sup> NUC505DS13Y LQFP 64-pin Description53 |

|   | 4.   | 3.7   | NuMicro <sup>®</sup> NUC505YO13Y QFN 88-pin Description    |

|   | 4.   | 3.8   | Summary GPIO Multi-function Pin Description                |

|   | 4.   | 3.9   | GPIO Multi-function Pin Summary                            |

| 5 | BLOC | CK D  | IAGRAM                                                     |

|   | 5.1  | NuM   | icro <sup>®</sup> NUC505 Series Block Diagram73            |

| 6 | FUNC | стю   | NAL DESCRIPTION                                            |

|   | 6.1  | ARM   | 1 <sup>®</sup> Cortex <sup>®</sup> -M4 Core74              |

|   | 6.2  | Syste | em Manager                                                 |

|     | 6.2.1  | Overview                                     |

|-----|--------|----------------------------------------------|

|     | 6.2.2  | System Reset                                 |

|     | 6.2.3  | System Power-on Setting                      |

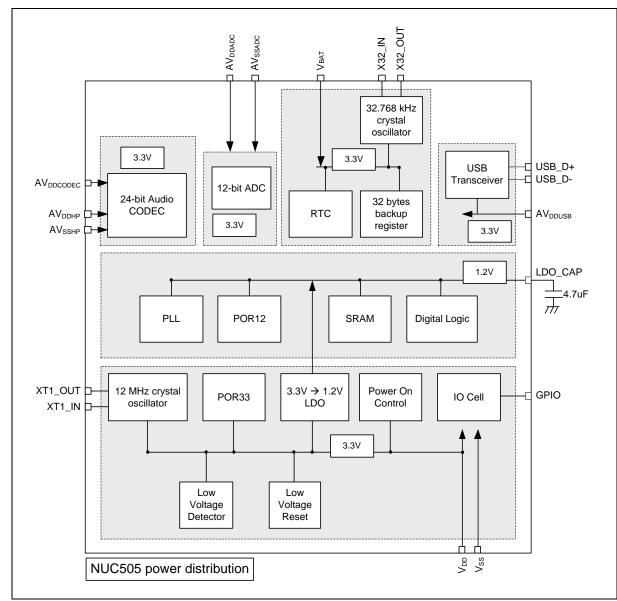

|     | 6.2.4  | System Power Distribution                    |

|     | 6.2.5  | System Memory Mapping                        |

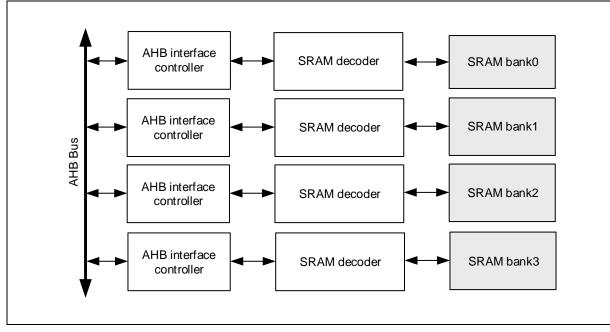

|     | 6.2.6  | SRAM Memory Organization                     |

|     | 6.2.7  | AHB Bus Arbitration                          |

|     | 6.2.8  | Registers Map                                |

|     | 6.2.9  | Register Description                         |

|     | 6.2.10 | System Timer (Systick) 125                   |

|     | 6.2.11 | Nested Vectored Interrupt Control (NVIC) 130 |

|     | 6.2.12 | System Control Register Map and Description  |

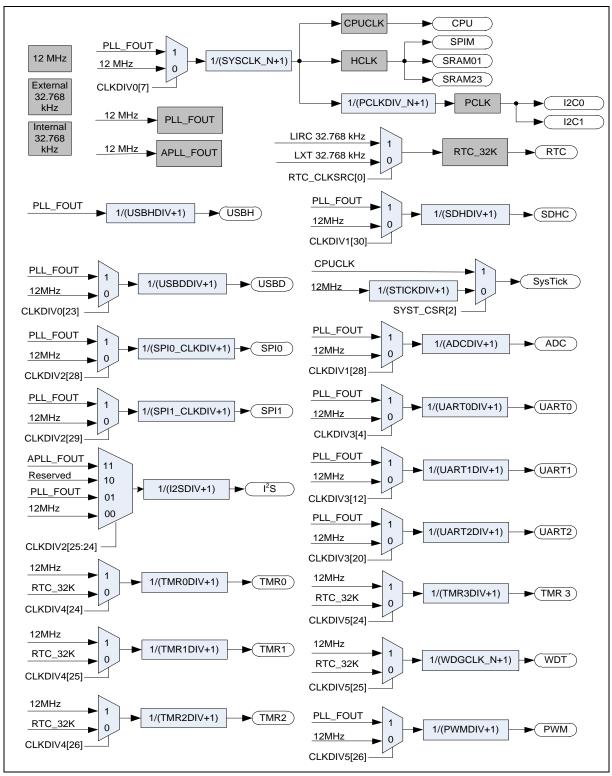

| 6.3 | Cloc   | k Controller150                              |

|     | 6.3.1  | Overview                                     |

|     | 6.3.2  | Clock Diagram                                |

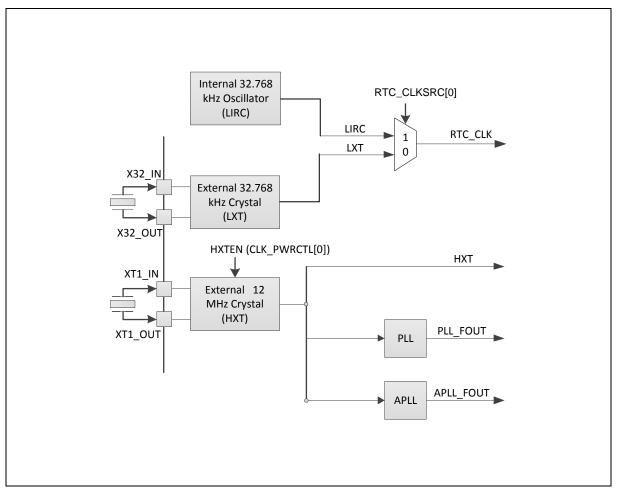

|     | 6.3.3  | Clock Generator 152                          |

|     | 6.3.4  | Power-down Mode Clock                        |

|     | 6.3.5  | Register Map154                              |

|     | 6.3.6  | Register Description                         |

| 6.4 | Gene   | eral Purpose I/O (GPIO)172                   |

|     | 6.4.1  | Overview                                     |

|     | 6.4.2  | Features                                     |

|     | 6.4.3  | Basic Configuration                          |

|     | 6.4.4  | Functional Description                       |

|     | 6.4.5  | Register Map 174                             |

|     | 6.4.6  | Register Description                         |

| 6.5 | Time   | er Controller (TIMER)                        |

|     | 6.5.1  | Overview                                     |

|     | 6.5.2  | Features                                     |

|     | 6.5.3  | Block Diagram                                |

|     | 6.5.4  | Functional Description                       |

|     | 6.5.5  | Register Map 193                             |

|     | 6.5.6  | Register Description                         |

| 6.6 | PWN    | A Generator and Capture Timer (PWM)          |

| 6.6.1   | Overview                        |

|---------|---------------------------------|

| 6.6.2   | Features                        |

| 6.6.3   | Block Diagram                   |

| 6.6.4   | Functional Description          |

| 6.6.5   | Register Map 213                |

| 6.6.6   | Register Description            |

| 6.7 Wa  | atchdog Timer (WDT)             |

| 6.7.1   | Overview                        |

| 6.7.2   | Features                        |

| 6.7.3   | Block Diagram                   |

| 6.7.4   | Functional Description          |

| 6.7.5   | Register Map 236                |

| 6.7.6   | Register Description            |

| 6.8 Wi  | ndow Watchdog Timer (WWDT)241   |

| 6.8.1   | Overview                        |

| 6.8.2   | Features                        |

| 6.8.3   | Block Diagram                   |

| 6.8.4   | Functional Description          |

| 6.8.5   | Register Map 244                |

| 6.8.6   | Register Description            |

| 6.9 Re  | al Time Clock (RTC)251          |

| 6.9.1   | Overview                        |

| 6.9.2   | Features                        |

| 6.9.3   | Block Diagram                   |

| 6.9.4   | Basic Configuration             |

| 6.9.5   | Functional Description          |

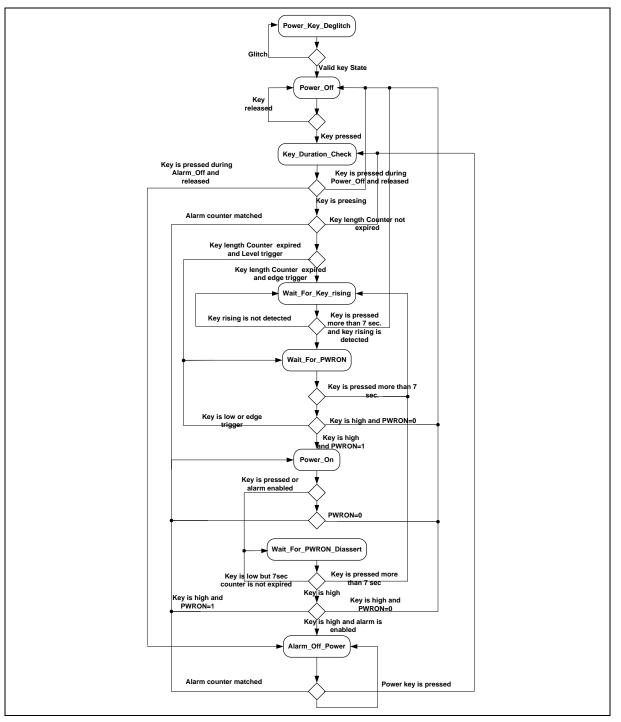

| 6.9.6   | System Power Control Flow       |

| 6.9.7   | Register Map                    |

| 6.9.8   | Register Description            |

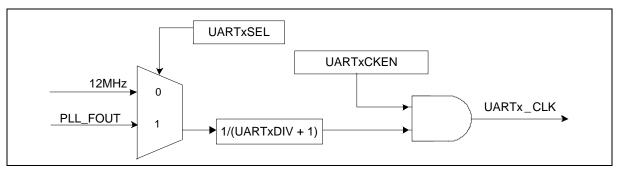

| 6.10 UA | ART Interface Controller (UART) |

| 6.10.   | 1 Overview                      |

| 6.10.   | 2 Features                      |

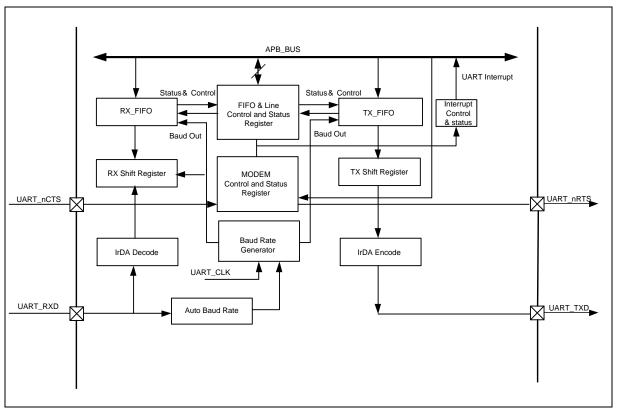

| 6.10.   | 3 Block Diagram                 |

| 6.10.   | 4 Basic Configuration           |

| 6.10.5                  | Functional Description                                     |

|-------------------------|------------------------------------------------------------|

| 6.10.6                  | Register Map 304                                           |

| 6.10.7                  | Register Description                                       |

| 6.11 I <sup>2</sup> C S | Serial Interface Controller (Master/Slave)                 |

| 6.11.1                  | Overview                                                   |

| 6.11.2                  | Features                                                   |

| 6.11.3                  | Basic Configuration                                        |

| 6.11.4                  | Functional Description                                     |

| 6.11.5                  | Operation Modes                                            |

| 6.11.6                  | Protocol Registers                                         |

| 6.11.7                  | Register Map 346                                           |

| 6.11.8                  | Register Description                                       |

| 6.12 Seria              | al Peripheral Interface (SPI)                              |

| 6.12.1                  | Overview                                                   |

| 6.12.2                  | Features                                                   |

| 6.12.3                  | Block Diagram                                              |

| 6.12.4                  | Functional Description                                     |

| 6.12.5                  | Timing Diagram                                             |

| 6.12.6                  | Programming Examples                                       |

| 6.12.7                  | Register Map 369                                           |

| 6.12.8                  | Register Description                                       |

| 6.13 SPI                | Memory Interface Controller (SPIM)                         |

| 6.13.1                  | Overview                                                   |

| 6.13.2                  | Features                                                   |

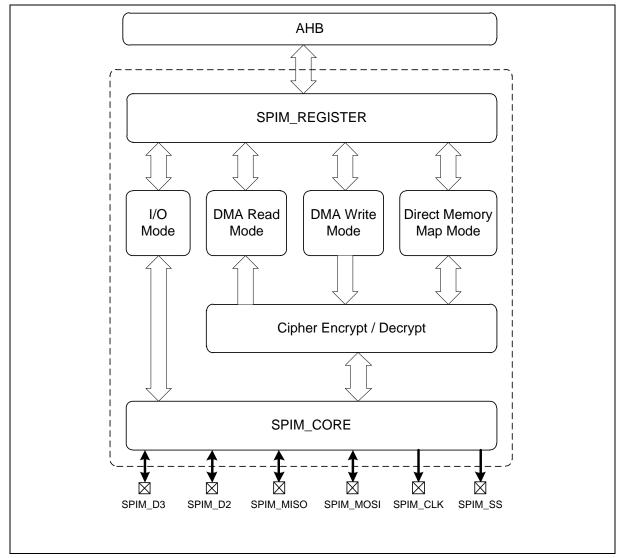

| 6.13.3                  | Block Diagram                                              |

| 6.13.4                  | Functional Description                                     |

| 6.13.5                  | Register Map 388                                           |

| 6.13.6                  | Register Description                                       |

| 6.14 I <sup>2</sup> S C | Controller with Internal Audio CODEC (I <sup>2</sup> S)401 |

| 6.14.1                  | Overview                                                   |

| 6.14.2                  | Features 401                                               |

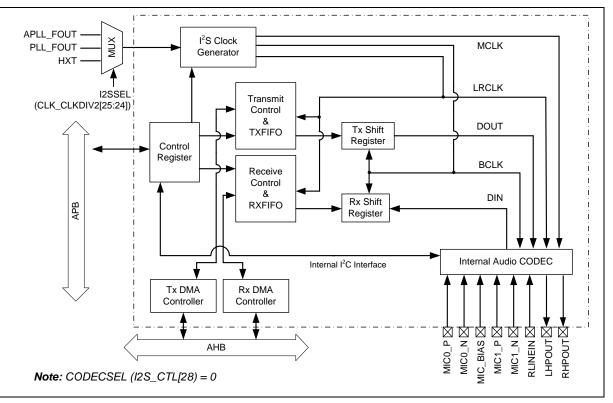

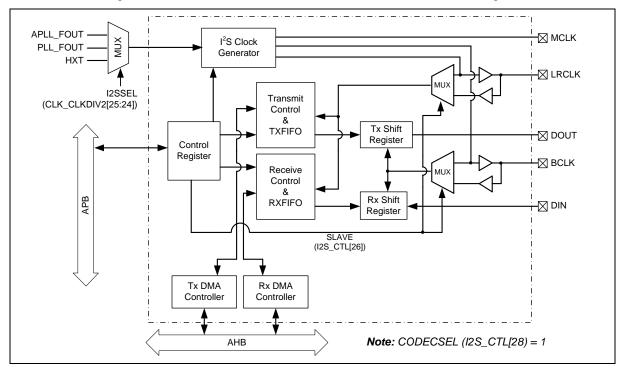

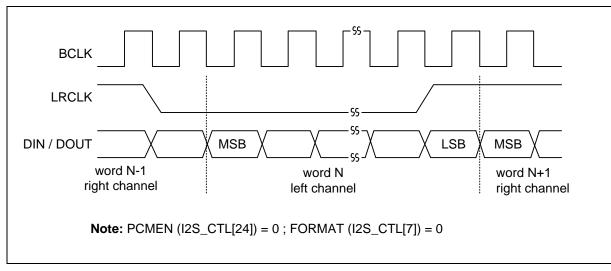

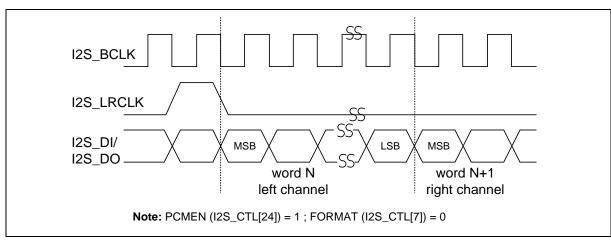

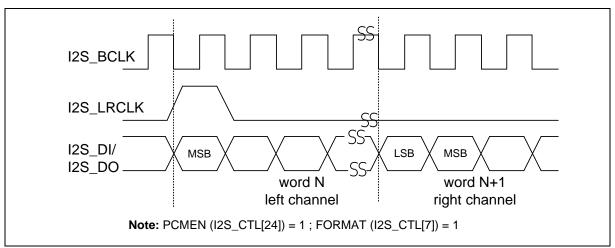

| 6.14.3                  | Block Diagram 402                                          |

| 6.14.4                  | I <sup>2</sup> S Operation Timing Diagram Description      |

| 6.14.5                  | FIFO Operation                                             |

| 6.14.6      | Functional Description                    |

|-------------|-------------------------------------------|

| 6.14.7      | Register Map                              |

| 6.14.8      | Register Description                      |

| 6.14.9      | CODEC Register Map 440                    |

| 6.14.10     | CODEC Register Description                |

| 6.15 USB    | 2.0 Device Controller (USBD)456           |

| 6.15.1      | Overview                                  |

| 6.15.2      | Features                                  |

| 6.15.3      | Block Diagram                             |

| 6.15.4      | Functional Description                    |

| 6.15.5      | Registers Map 460                         |

| 6.15.6      | Register Description                      |

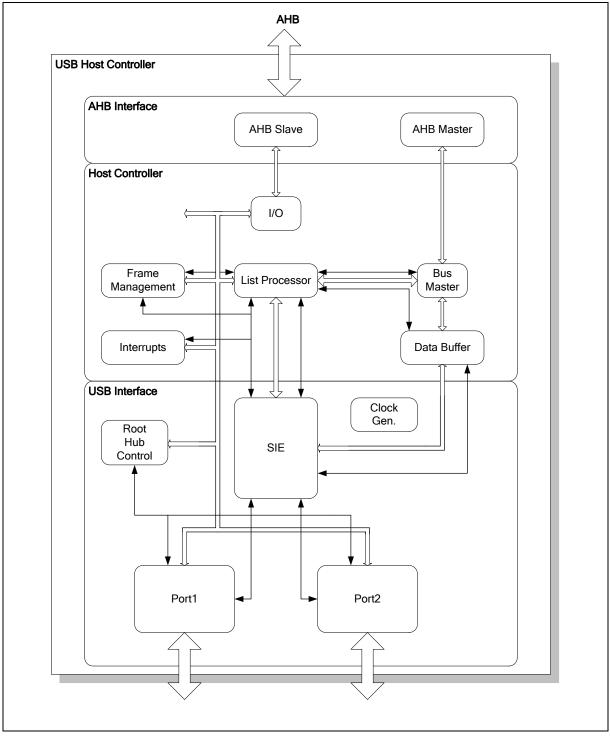

| 6.16 USB    | 1.1 Host Controller (USBH)519             |

| 6.16.1      | Overview                                  |

| 6.16.2      | Features                                  |

| 6.16.3      | Block Diagram                             |

| 6.16.4      | Basic Configuration                       |

| 6.16.5      | Functional Description                    |

| 6.16.6      | Register Map 523                          |

| 6.16.7      | Register Description                      |

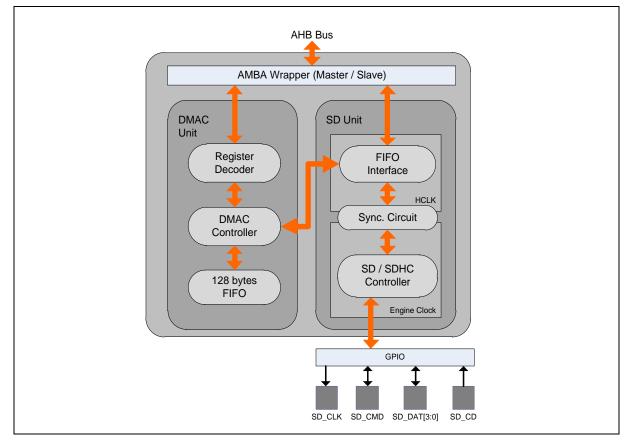

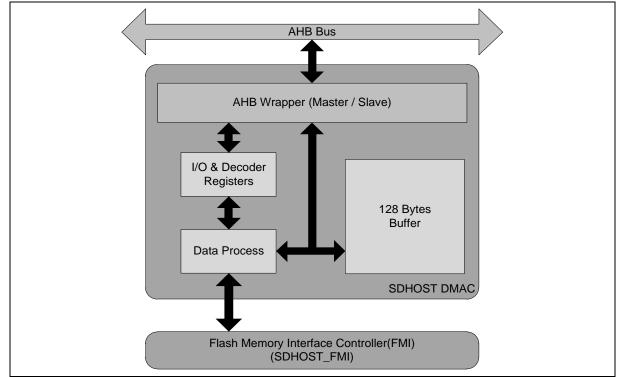

| 6.17 Secu   | re-Digital Host Controller (SDHC)556      |

| 6.17.1      | Overview                                  |

| 6.17.2      | Features 556                              |

| 6.17.3      | Block Diagram and Card Pad Assignment 557 |

| 6.17.4      | SD HOST DMA Controller 558                |

| 6.17.5      | Secure-Digital SD/SDHC Controller 559     |

| 6.17.6      | Register Map                              |

| 6.17.7      | Register Description                      |

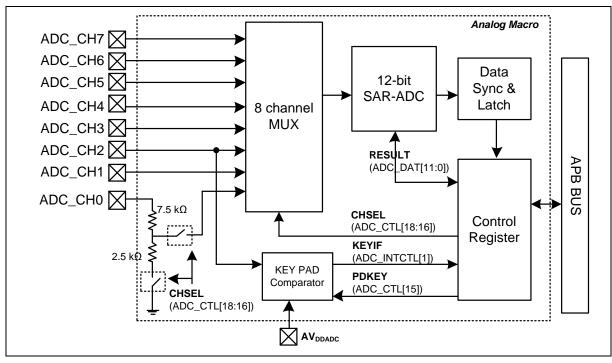

| 6.18 12-bit | Analog-to-Digital Converter (ADC)         |

| 6.18.1      | Overview                                  |

| 6.18.2      | Features                                  |

| 6.18.3      | Block Diagram                             |

| 6.18.4      | Operation Description                     |

| 6.18.5      | Register Map                              |

|   | 6   | 6.18.6 Register Description          | 589 |

|---|-----|--------------------------------------|-----|

| 7 | ELE | CTRICAL CHARACTERISTICS              | 593 |

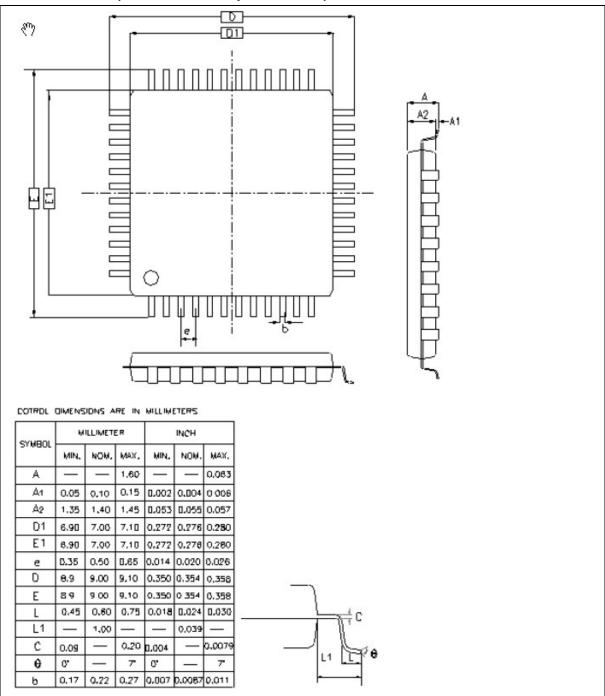

| 8 | PAC | CKAGE DIMENSIONS                     | 594 |

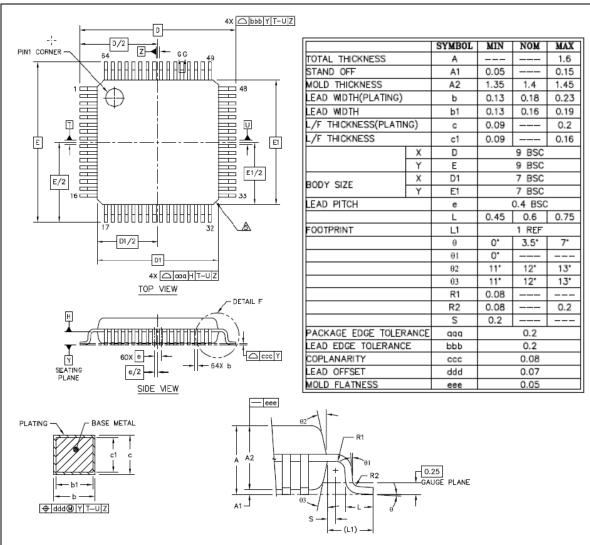

|   | 8.1 | LQFP 48L (7x7x1.4mm footprint 2.0mm) | 594 |

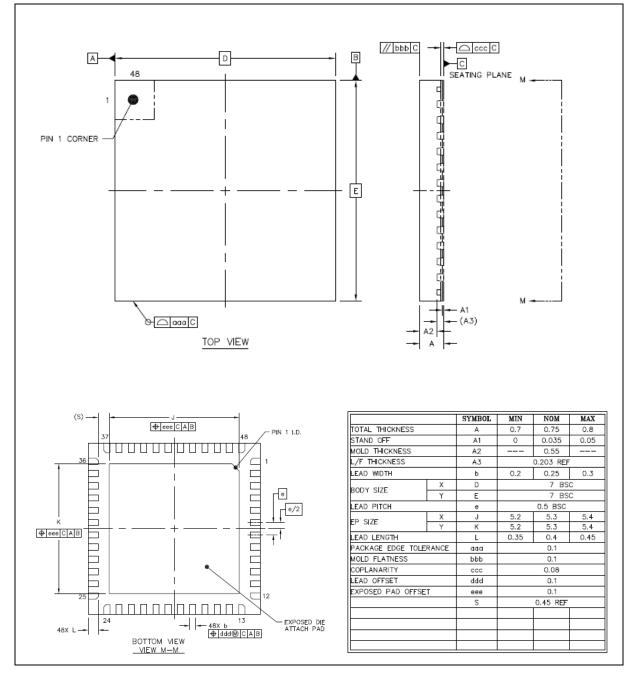

|   | 8.2 | QFN 48 (7x7x0.8mm)                   | 595 |

|   | 8.3 | LQFP 64L (7x7x1.4mm footprint 2.0mm) | 596 |

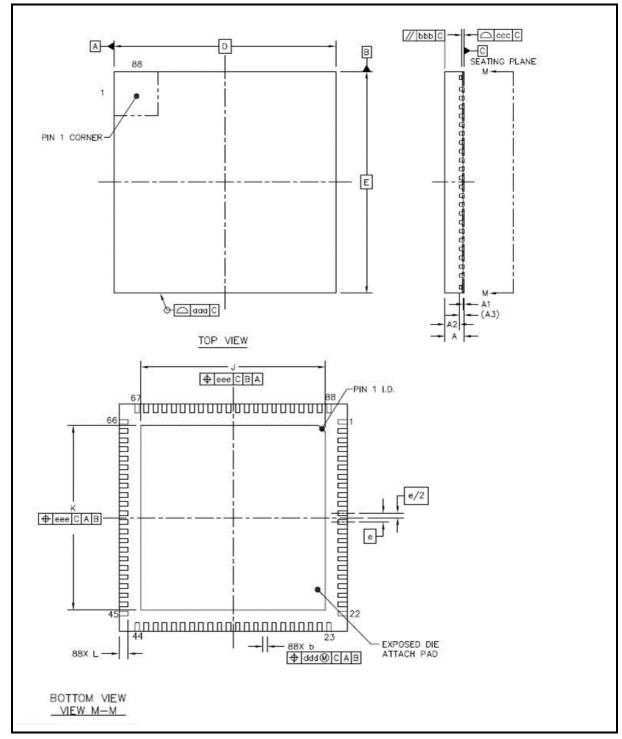

|   | 8.4 | QFN 88 (10x10x0.9mm)                 | 597 |

| 9 | REV | /ISION HISTORY                       | 599 |

### List of Figures

| Figure 4.1-1 NuMicro <sup>®</sup> NUC505 Base Series Selection Code | . 21 |

|---------------------------------------------------------------------|------|

| Figure 4.2-1 NuMicro <sup>®</sup> NUC505DLA LQFP 48-pin Diagram     | . 22 |

| Figure 4.2-2 NuMicro <sup>®</sup> NUC505DL13Y LQFP 48-pin Diagram   | . 23 |

| Figure 4.2-3 NuMicro <sup>®</sup> NUC505YLA QFN 48-pin Diagram      | . 24 |

| Figure 4.2-4 NuMicro <sup>®</sup> NUC505YLA2Y QFN 48-pin Diagram    | . 25 |

| Figure 4.2-5 NuMicro <sup>®</sup> NUC505DSA LQFP 64-pin Diagram     | . 26 |

| Figure 4.2-6 NuMicro <sup>®</sup> NUC505DS13Y LQFP 64-pin Diagram   | . 27 |

| Figure 4.2-7 NuMicro <sup>®</sup> NUC505YO13Y QFN 88-pin Diagram    | . 28 |

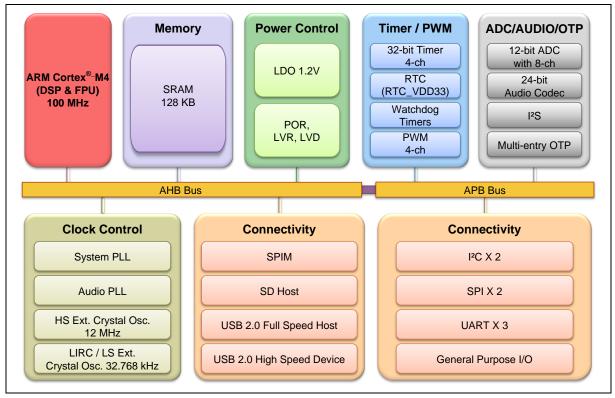

| Figure 5.1-1 NuMicro <sup>®</sup> NUC505 Block Diagram              | . 73 |

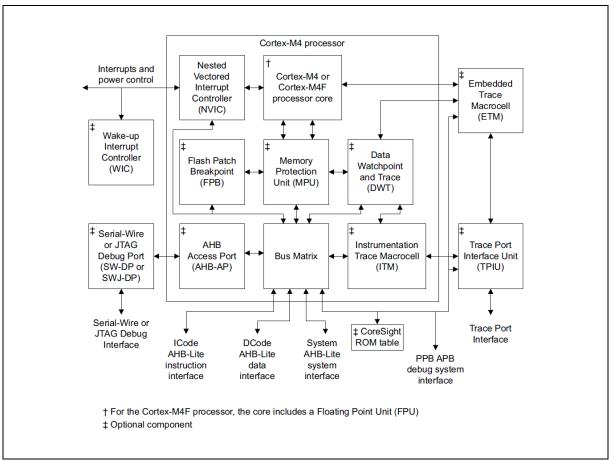

| Figure 6.1-1 Cortex <sup>®</sup> -M4 Block Diagram                  | . 74 |

| Figure 6.2-1 NuMicro <sup>®</sup> NUC505 Power Distribution Diagram | . 79 |

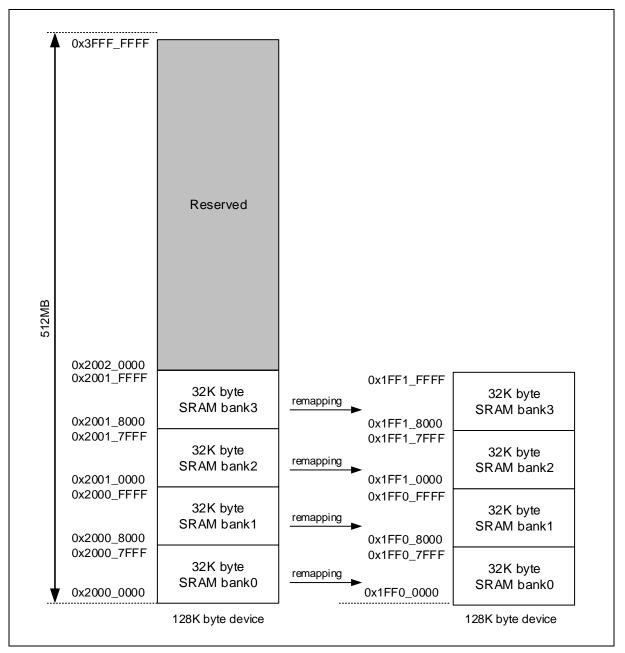

| Figure 6.2-2 SRAM Block Diagram                                     | . 81 |

| Figure 6.2-3 SRAM Memory Organization                               | . 82 |

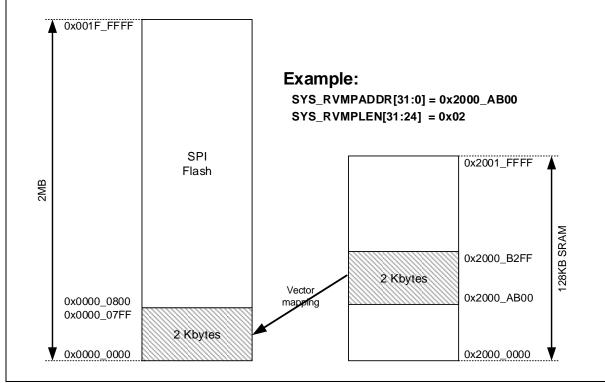

| Figure 6.2-4 Vector Map Module Block                                | . 83 |

| Figure 6.3-1 Clock Generator Global View Diagram                    | 151  |

| Figure 6.3-2 Clock Generator Block Diagram                          | 152  |

| Figure 6.3-3 Crystal Oscillator Circuit                             | 153  |

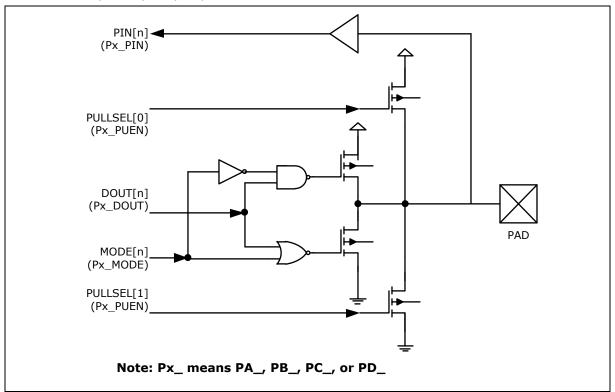

| Figure 6.4-1 I/O Pin Block Diagram                                  | 172  |

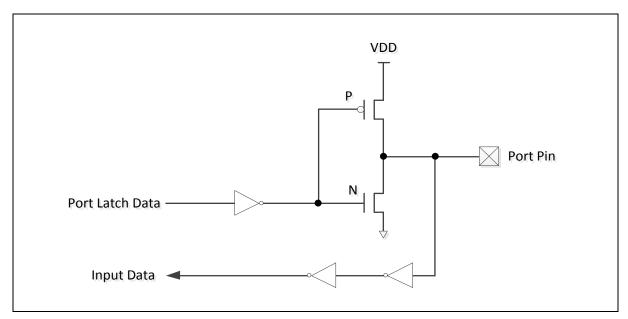

| Figure 6.4-2 Push-Pull Output                                       | 173  |

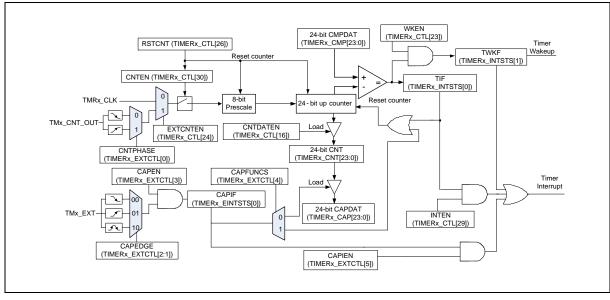

| Figure 6.5-1 Timer Controller Block Diagram                         | 189  |

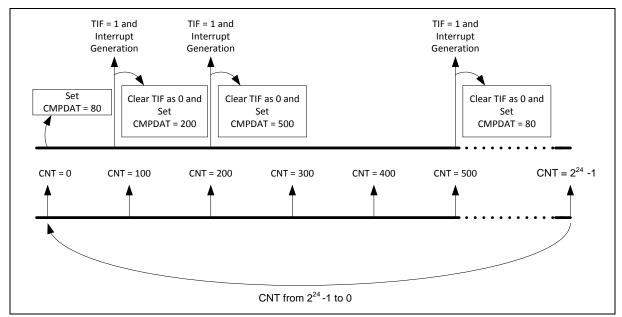

| Figure 6.5-2 Continuous Counting Mode                               | 191  |

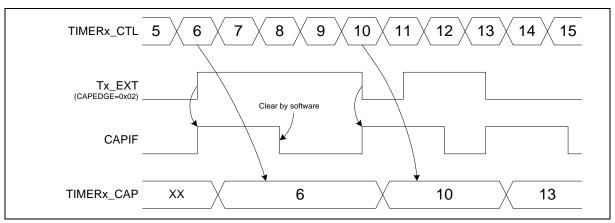

| Figure 6.5-3 External Capture Mode                                  | 192  |

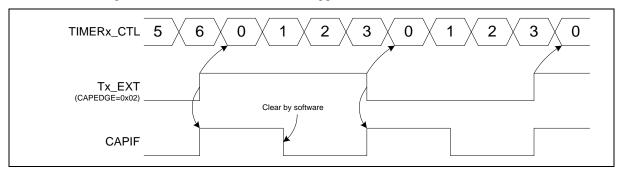

| Figure 6.5-4 External Reset Counter Mode                            | 192  |

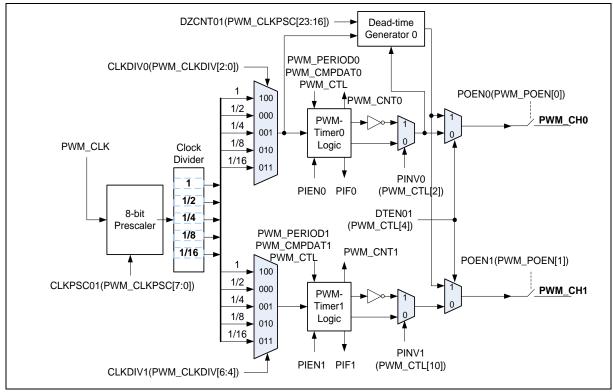

| Figure 6.6-1 PWM Generator 0 Architecture Diagram                   | 205  |

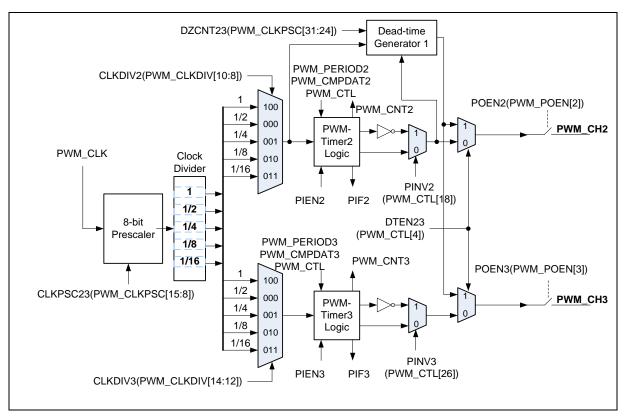

| Figure 6.6-2 PWM Generator 1 Architecture Diagram                   | 206  |

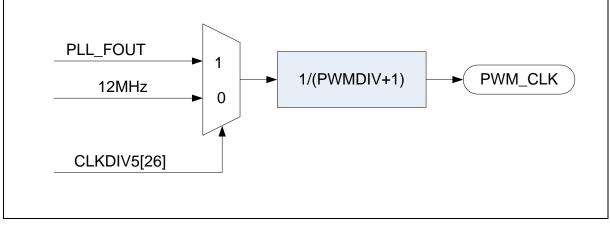

| Figure 6.6-3 PWM System Clock Source Control                        | 206  |

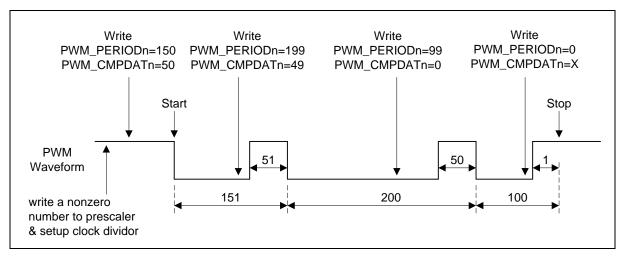

| Figure 6.6-4 PWM Waveform of Edge-aligned Type                      | 207  |

| Figure 6.6-5 PWM Double Buffering Timing Waveform                   | 208  |

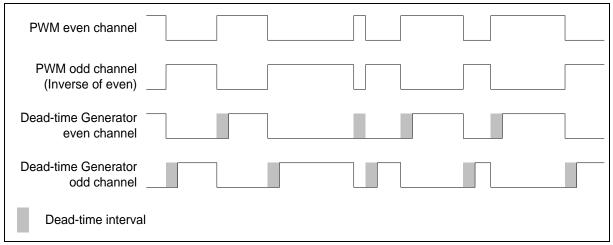

| Figure 6.6-6 PWM Paired-output with Dead-time Generation Operation  | 209  |

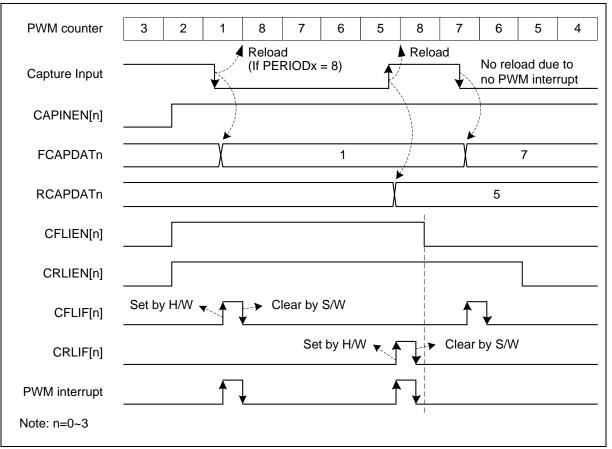

| Figure 6.6-7 Capture Operation Timing                               | 210  |

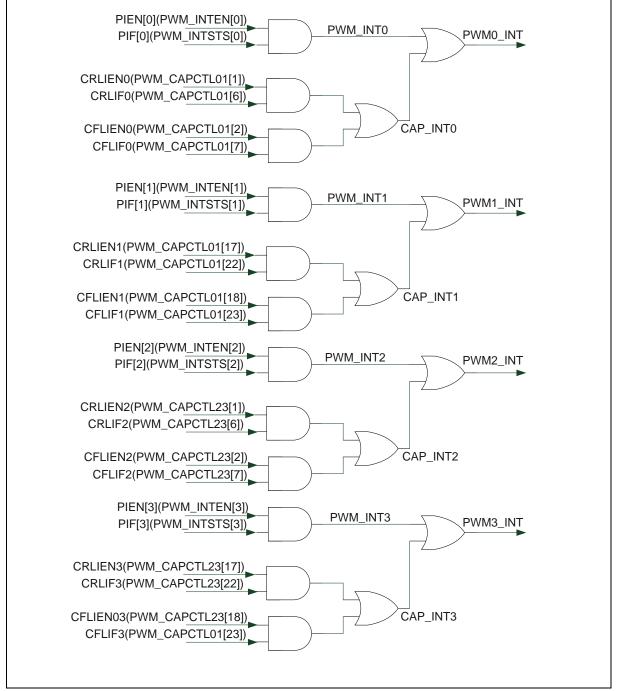

| Figure 6.6-8 PWM Interrupt Generator                                | 212  |

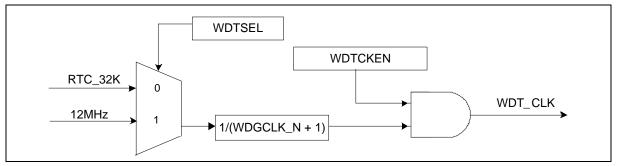

| Figure 6.7-1 Watchdog Timer Clock Control Diagram                   | 231  |

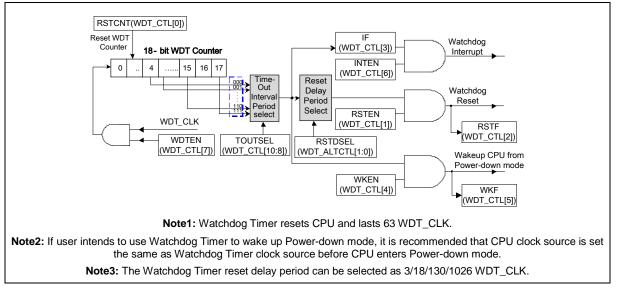

| Figure 6.7-2 Watchdog Timer Block Diagram                           | 232  |

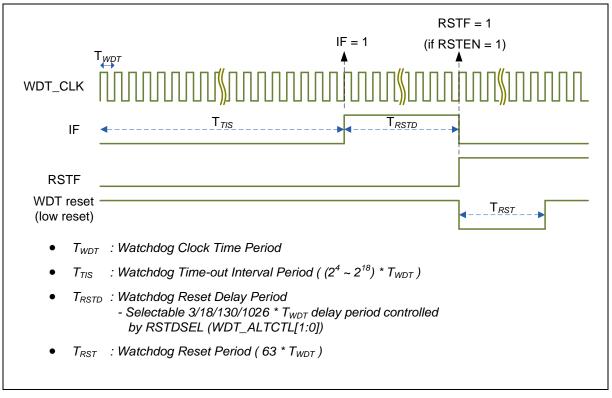

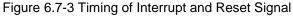

| Figure 6.7-3 Timing of Interrupt and Reset Signal                   | 235  |

| Figure 6.8-1 Window Watchdog Timer Block Diagram                    | 241  |

|                                                                     |      |

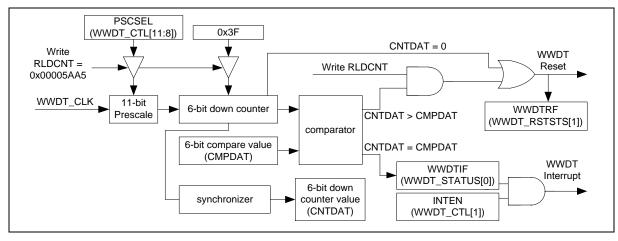

| Figure 6.8-2 Window Watchdog Timer Reset and Reload Behavior                            |

|-----------------------------------------------------------------------------------------|

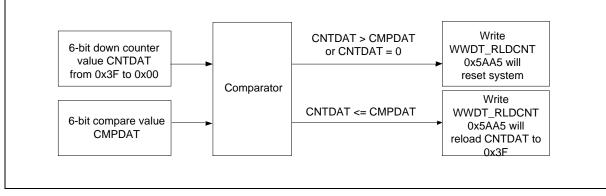

| Figure 6.9-1 RTC Block Diagram 252                                                      |

| Figure 6.9-2 System Power Control Flow Chart                                            |

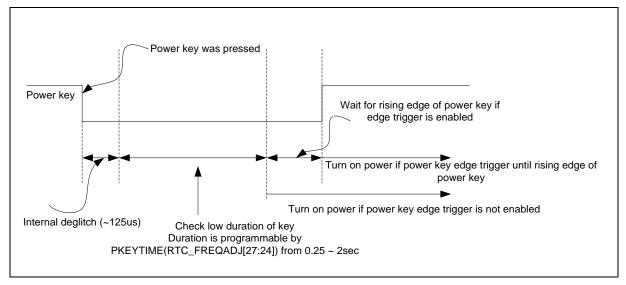

| Figure 6.9-3 Power Key Detection Mechanism                                              |

| Figure 6.10-1 UART Clock Control Diagram                                                |

| Figure 6.10-2 UART Block Diagram                                                        |

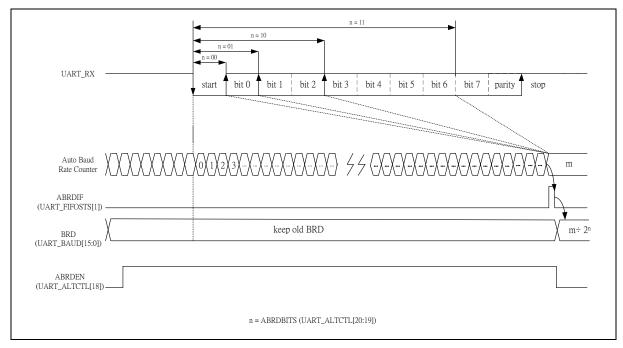

| Figure 6.10-3 Auto-Baud Rate Measurement                                                |

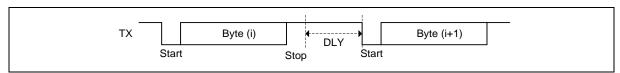

| Figure 6.10-4 Transmit Delay Time Operation                                             |

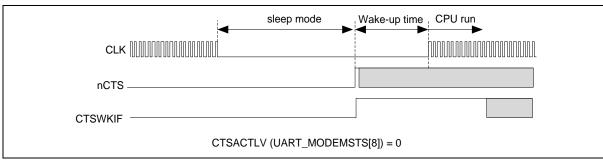

| Figure 6.10-5 UART nCTS Wake-UP Case1                                                   |

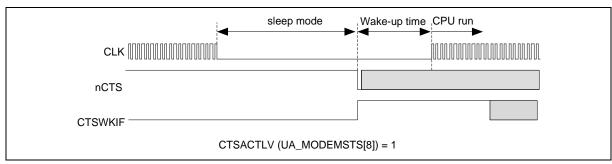

| Figure 6.10-6 UART nCTS Wake-UP Case2                                                   |

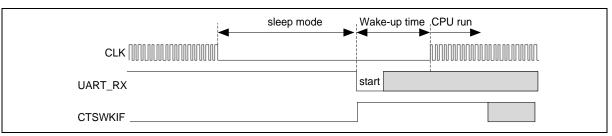

| Figure 6.10-7 UART Data Wake-Up 286                                                     |

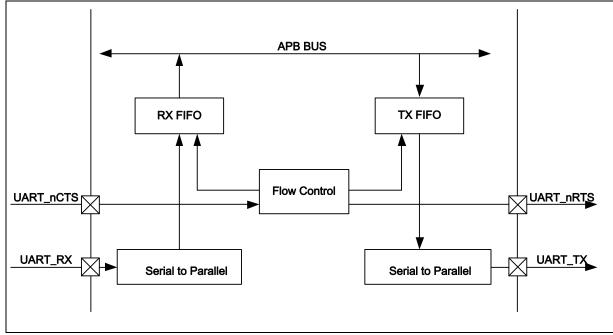

| Figure 6.10-8 Auto-Flow Control Block Diagram                                           |

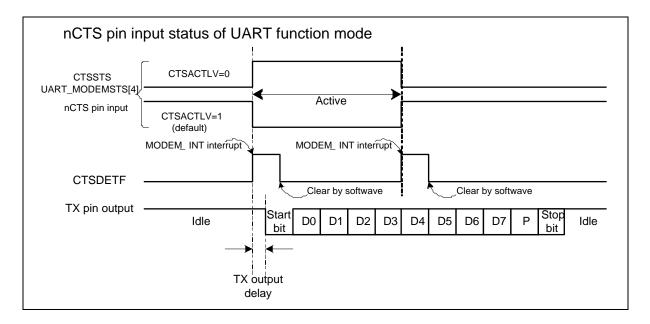

| Figure 6.10-9 UART nCTS Auto-Flow Control Enabled                                       |

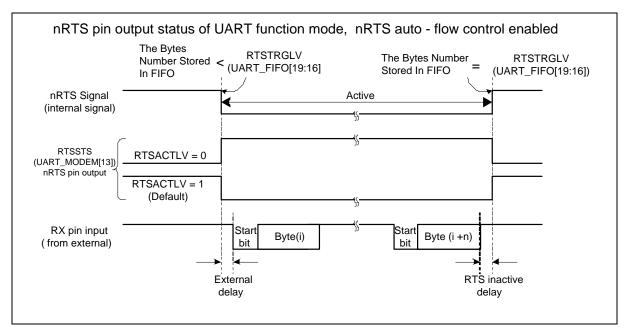

| Figure 6.10-10 UART nRTS Auto-Flow Control Enabled                                      |

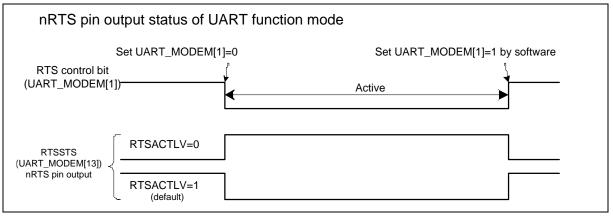

| Figure 6.10-11 UART nRTS Auto-Flow with Software Control                                |

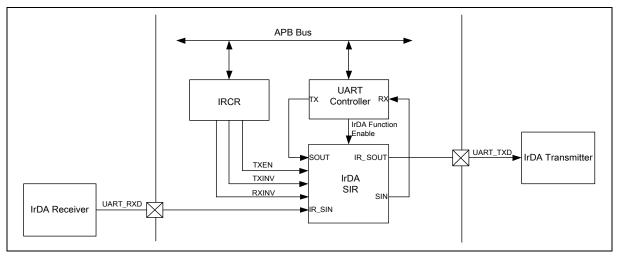

| Figure 6.10-12 IrDA Control Block Diagram                                               |

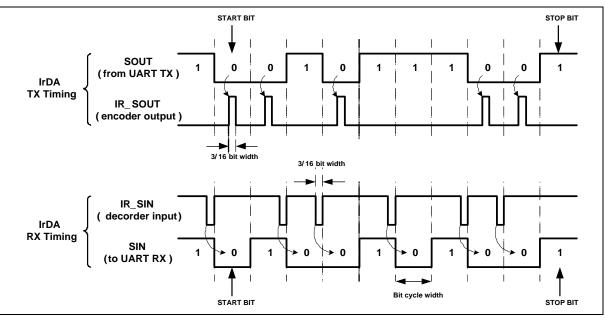

| Figure 6.10-13 IrDA TX/RX Timing Diagram                                                |

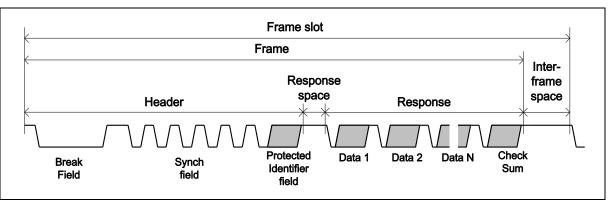

| Figure 6.10-14 Structure of LIN Frame                                                   |

| Figure 6.10-15 Structure of LIN Byte                                                    |

| Figure 6.10-16 LIN Frame ID and Parity Format                                           |

| Figure 6.10-17 Break Detection in LIN Mode                                              |

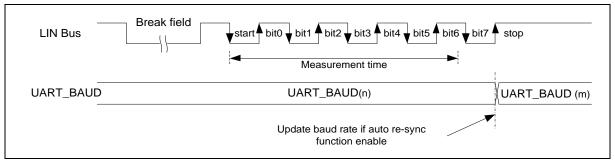

| Figure 6.10-18 LIN Sync Field Measurement                                               |

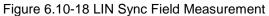

| Figure 6.10-19 UART_BAUD Update Sequence in AR mode if SLVDUEN is 1                     |

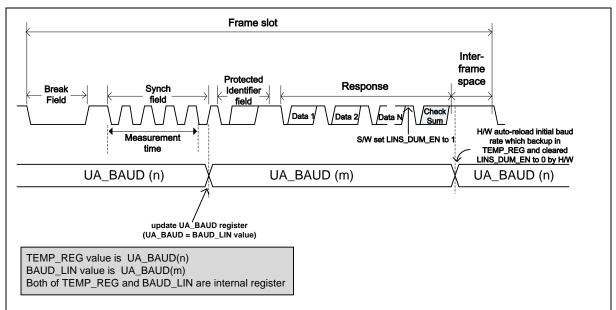

| Figure 6.10-20 UART_BAUD Update Sequence in AR mode if SLVDUEN is 0                     |

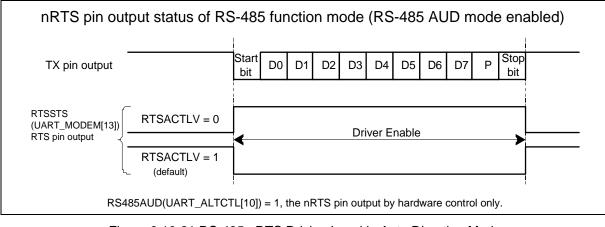

| Figure 6.10-21 RS-485 nRTS Driving Level in Auto Direction Mode                         |

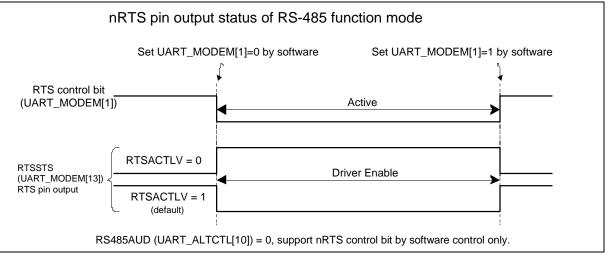

| Figure 6.10-22 RS-485 nRTS Driving Level with Software Control                          |

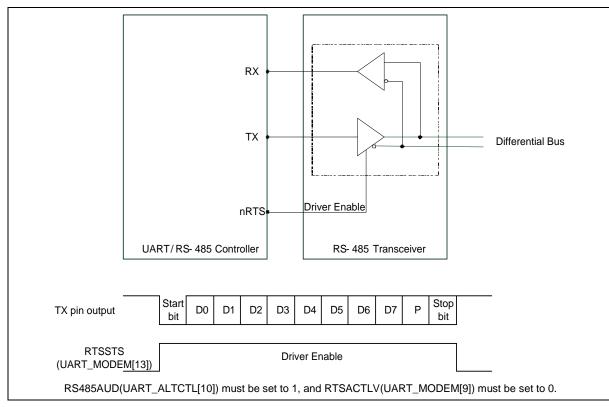

| Figure 6.10-23 Structure of RS-485 Frame                                                |

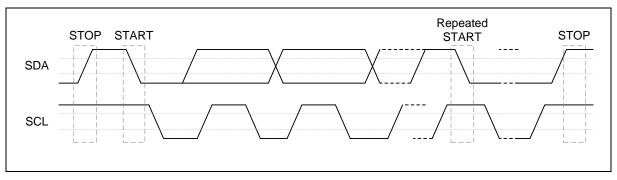

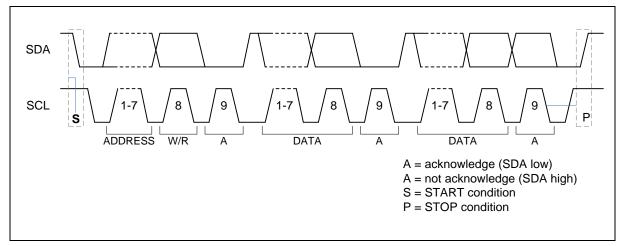

| Figure 6.11-1 I <sup>2</sup> C Bus Timing                                               |

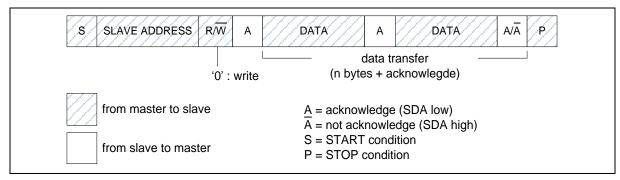

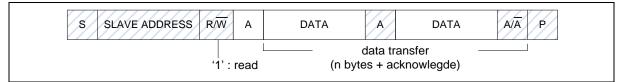

| Figure 6.11-2 I <sup>2</sup> C Protocol                                                 |

| Figure 6.11-3 Master Transmits Data to Slave                                            |

| Figure 6.11-4 Master Reads Data from Slave                                              |

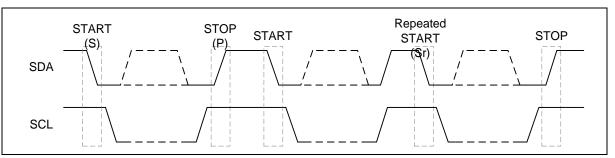

| Figure 6.11-5 START and STOP Condition                                                  |

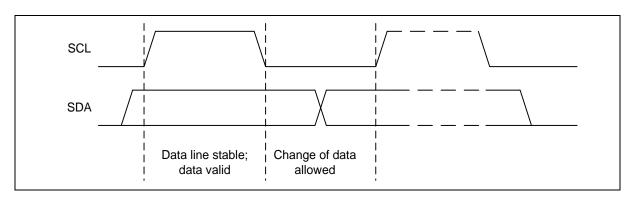

| Figure 6.11-6 Bit Transfer on I <sup>2</sup> C Bus                                      |

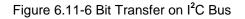

| Figure 6.11-7 Acknowledge on I <sup>2</sup> C Bus                                       |

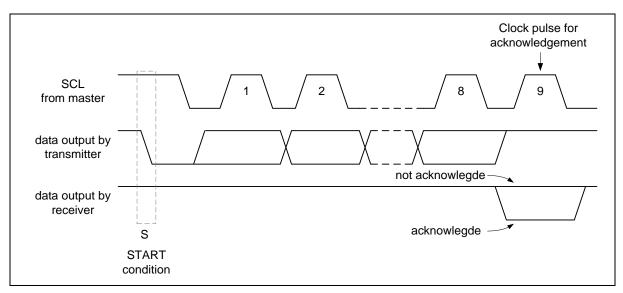

| Figure 6.11-8 Control I <sup>2</sup> C Bus according to Current I <sup>2</sup> C Status |

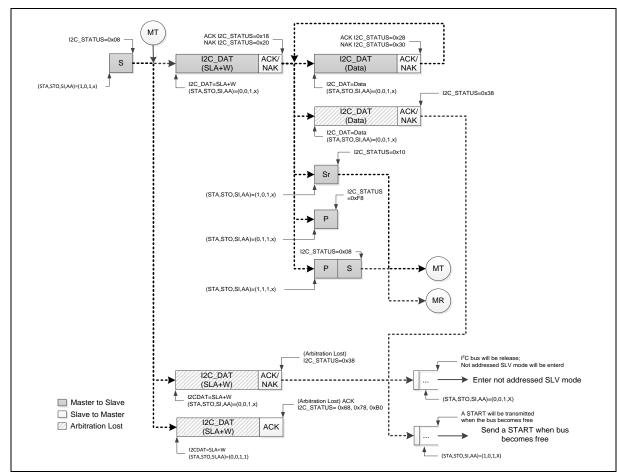

| Figure 6.11-9 Master Transmitter Mode Control Flow                                      |

|                                                                                         |

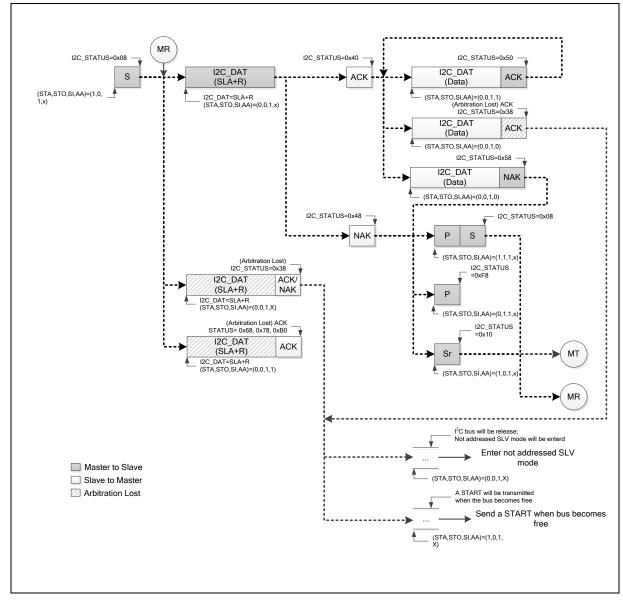

| Figure 6.11-10 Master Receiver Mode Control Flow                                  |       |  |

|-----------------------------------------------------------------------------------|-------|--|

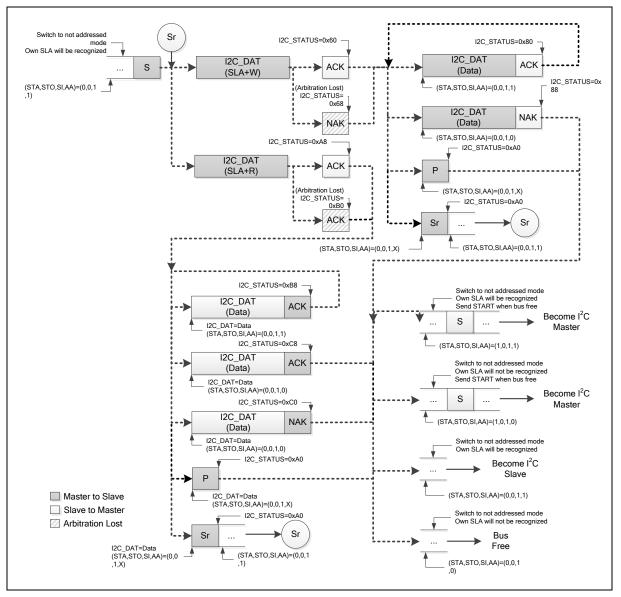

| Figure 6.11-11 Slave Mode Control Flow                                            |       |  |

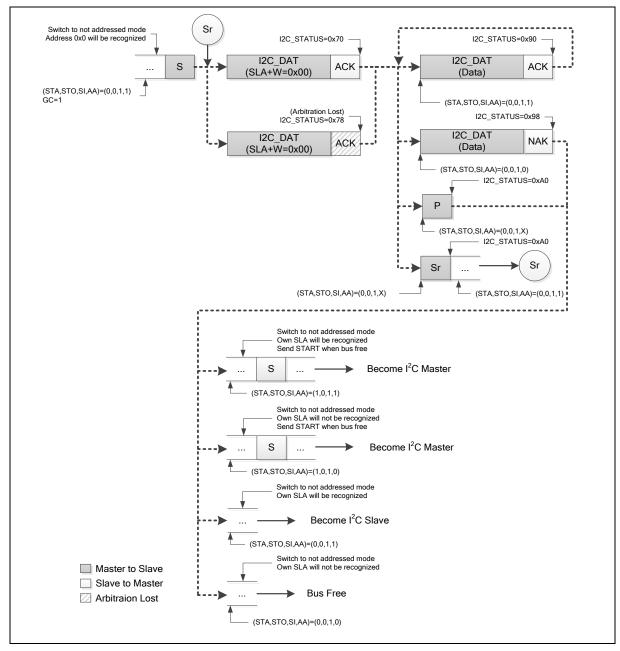

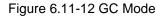

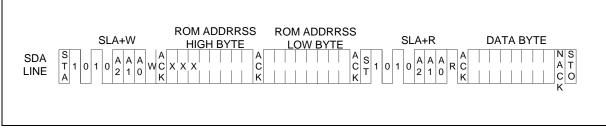

| Figure 6.11-12 GC Mode                                                            |       |  |

| Figure 6.11-13 EEPROM Random Read                                                 |       |  |

| Figure 6.11-14 Protocol of EEPROM Random Read                                     | . 341 |  |

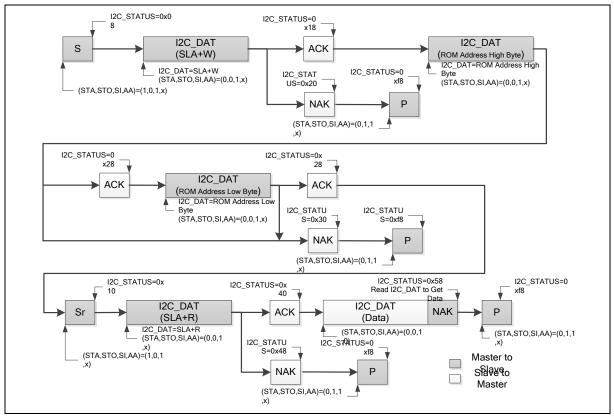

| Figure 6.11-15 I <sup>2</sup> C Data Shifting Direction                           | . 343 |  |

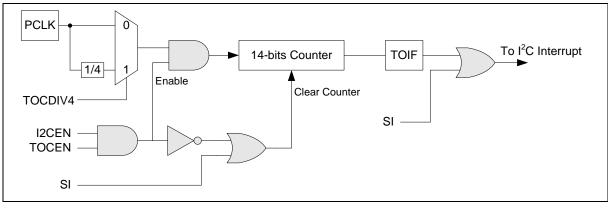

| Figure 6.11-16 I <sup>2</sup> C Time-out Count Block Diagram                      | . 345 |  |

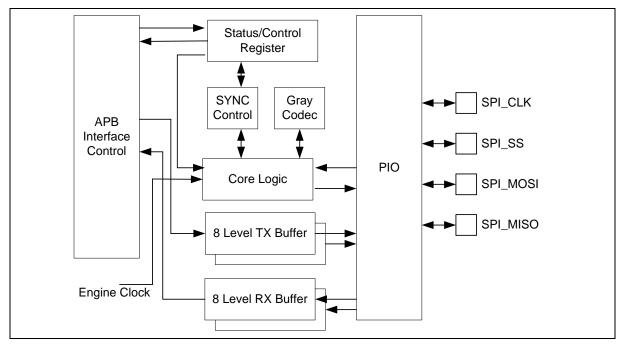

| Figure 6.12-1 SPI Block Diagram                                                   | . 357 |  |

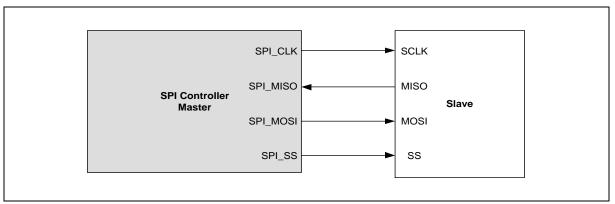

| Figure 6.12-2 SPI Master Mode Application Block Diagram                           | . 358 |  |

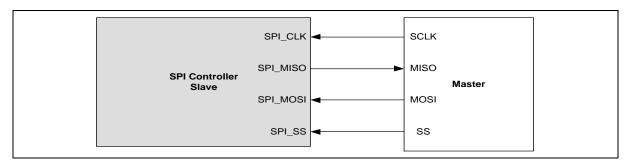

| Figure 6.12-3 SPI Slave Mode Application Block Diagram                            | . 358 |  |

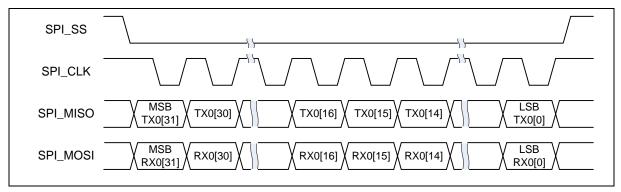

| Figure 6.12-4 Bit in One Transaction                                              | . 359 |  |

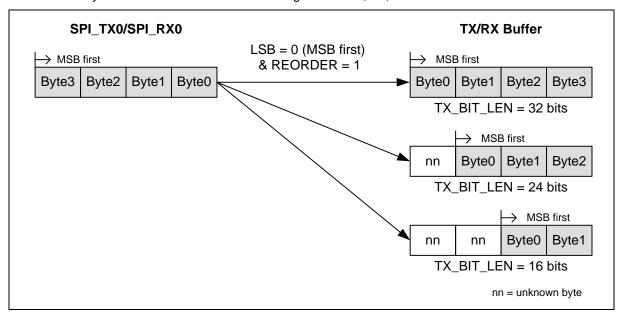

| Figure 6.12-5 Byte Reorder Function                                               | . 360 |  |

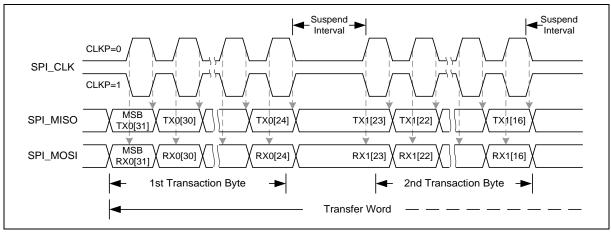

| Figure 6.12-6 Timing Waveform for Byte Suspend                                    | . 361 |  |

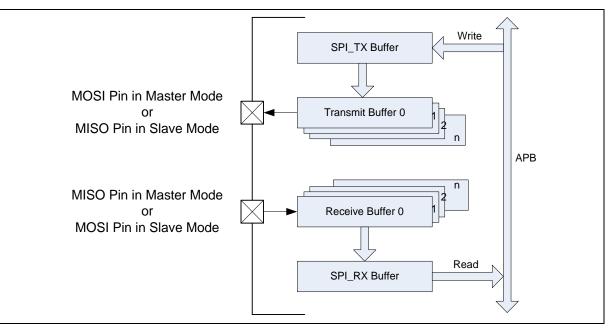

| Figure 6.12-7 FIFO Mode Block Diagram                                             | . 362 |  |

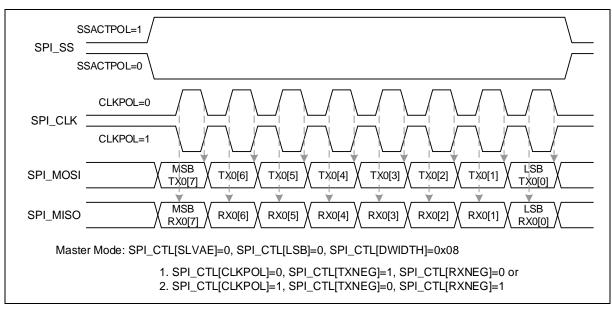

| Figure 6.12-8 SPI Timing in Master Mode                                           | . 365 |  |

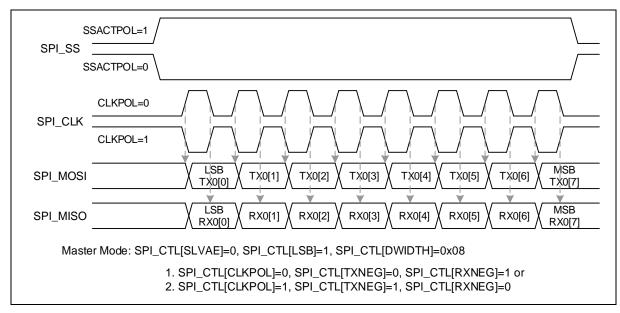

| Figure 6.12-9 SPI Timing in Master Mode (Alternate Phase of SPICLK)               | . 365 |  |

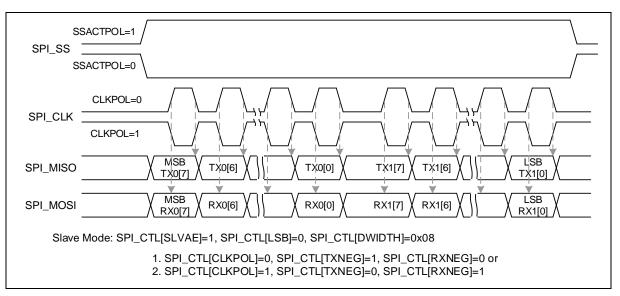

| Figure 6.12-10 SPI Timing in Slave Mode                                           | . 366 |  |

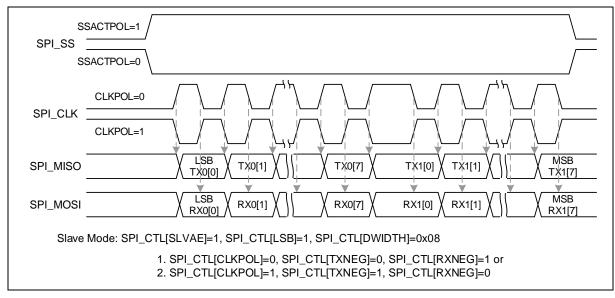

| Figure 6.12-11 SPI Timing in Slave Mode (Alternate Phase of SPICLK)               | . 366 |  |

| Figure 6.13-1 SPIM Block Diagram                                                  | . 383 |  |

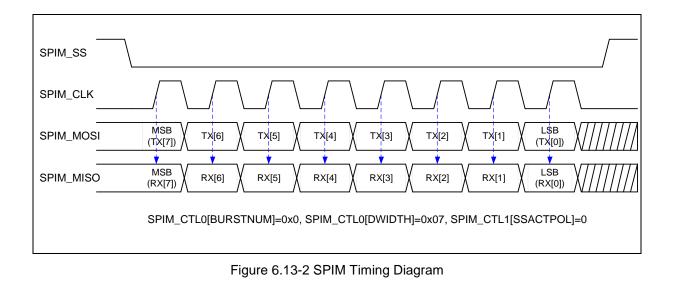

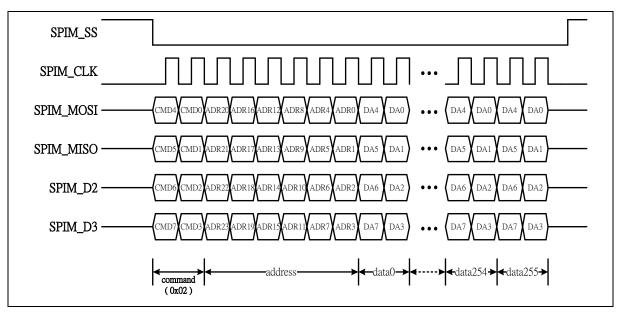

| Figure 6.13-2 SPIM Timing Diagram                                                 | . 384 |  |

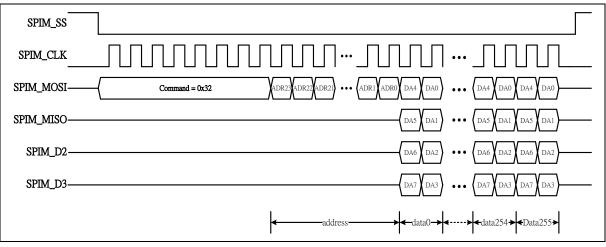

| Figure 6.13-3 TYPE_1 Program Command Flow with Quad Mode Write.                   | . 386 |  |

| Figure 6.13-4 TYPE_2 Program Command Flow with Quad Mode Write.                   | . 386 |  |

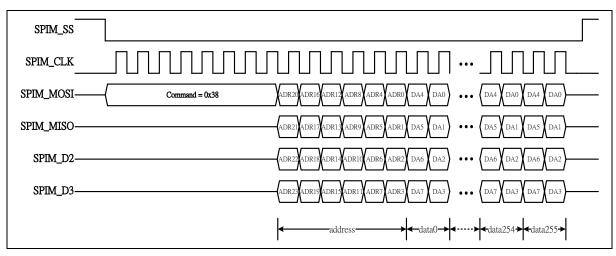

| Figure 6.13-5 TYPE_3 Program Command Flow with Quad Mode Write.                   | . 387 |  |

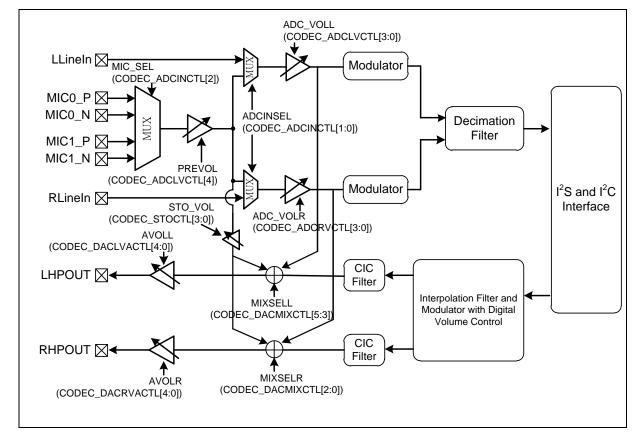

| Figure 6.14-1 I <sup>2</sup> S Controller with Internal Audio CODEC Block Diagram | . 402 |  |

| Figure 6.14-2 I <sup>2</sup> S Controller with External Audio CODEC Block Diagram | . 402 |  |

| Figure 6.14-3 Internal CODEC Block Diagram                                        | . 403 |  |

| Figure 6.14-4 I <sup>2</sup> S Bus Timing Diagram                                 | . 404 |  |

| Figure 6.14-5 MSB Justified Timing Diagram                                        | . 404 |  |

| Figure 6.14-6 PCM-A Audio Timing Diagram                                          |       |  |

| Figure 6.14-7 PCM-B Audio Timing Diagram                                          | . 405 |  |

| Figure 6.14-8 FIFO Contents for Various I <sup>2</sup> S Modes                    |       |  |

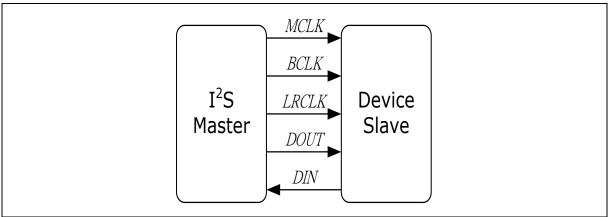

| Figure 6.14-9 Master Mode Interface Block Diagram                                 |       |  |

| Figure 6.14-10 Slave Mode Interface Block Diagram                                 |       |  |

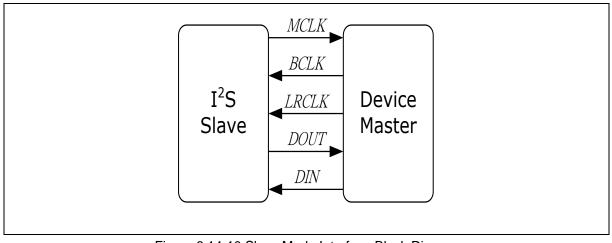

| Figure 6.14-11 I <sup>2</sup> S Controller Interrupts                             |       |  |

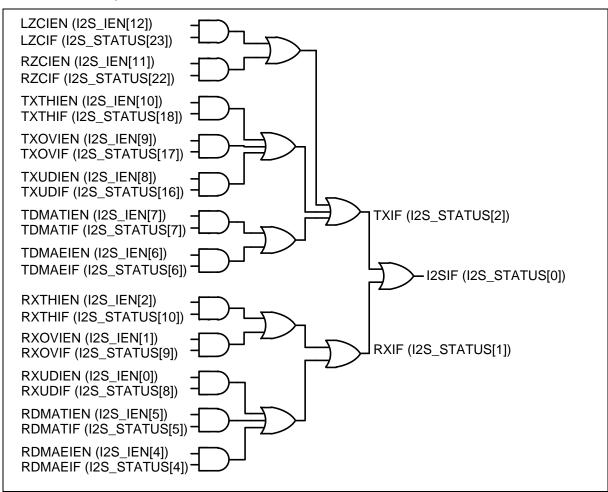

| Figure 6.15-1 USB Device Controller Block Diagram                                 |       |  |

| Figure 6.16-1 USB 1.1 Host Controller Block Diagram                               |       |  |

| с                                                                                 |       |  |

| Figure 6.17-1 SDH Controller Block Diagram      | . 557 |

|-------------------------------------------------|-------|

| Figure 6.17-2 DMA Controller Block Diagram      | . 558 |

| Figure 6.17-3 Format of PAD Table               | . 565 |

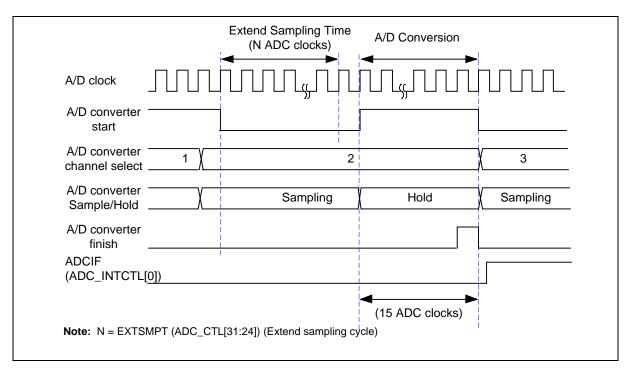

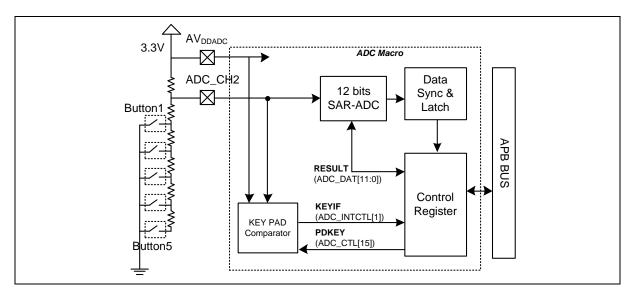

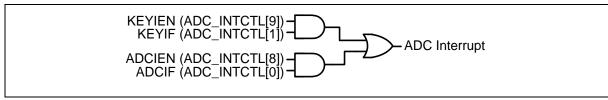

| Figure 6.18-1 ADC Control Block Diagram         | . 585 |

| Figure 6.18-2 Conversion Timing Diagram         | . 586 |

| Figure 6.18-3 Key-Pad Application Block Diagram | . 586 |

| Figure 6.18-4 ADC Controller Interrupts         | . 587 |

#### List of Tables

| Table 3.1-1 List of Abbreviations                                     |  |

|-----------------------------------------------------------------------|--|

| Table 4.1-1 NuMicro <sup>®</sup> NUC505 Base Series Selection Guide   |  |

| Table 4.3-1 NUC505 GPIO Multi-function Table                          |  |

| Table 6.2-1 System Power-on Setting Guide                             |  |

| Table 6.2-2 Address Space Assignments for On-Chip Controllers         |  |

| Table 6.2-3 AHB Bus Priority Order in Fixed Priority Mode             |  |

| Table 6.2-4 Exception Model                                           |  |

| Table 6.2-5 Interrupt Number Table                                    |  |

| Table 6.2-6 Priority Grouping                                         |  |

| Table 6.3-1 Recommended Load Capacitance Values and Resistance Values |  |

| Table 6.3-2 Power-down Mode Control Table                             |  |

| Table 6.7-1 Watchdog Timer Interval Selection                         |  |

| Table 6.8-1 Window Watchdog Prescaler Value Selection                 |  |

| Table 6.8-2 CMPDAT Setting Limitation                                 |  |

| Table 6.10-1 UART Interface Controller Pin                            |  |

| Table 6.10-2 UART Controller Baud Rate Equation Table                 |  |

| Table 6.10-3 UART Controller Interrupt Source and Flag List           |  |

| Table 6.10-4 UART Line Control of Word and Stop Length Setting        |  |

| Table 6.10-5 UART Line Control of Parity Bit Setting                  |  |

| Table 6.10-6 LIN Header Selection in Master Mode                      |  |

| Table 6.11-1 I <sup>2</sup> C Status Code Description Table           |  |

| Table 6.14-1 Clock Reference with Internal Audio CODEC                |  |

| Table 6.14-2 Clock Reference with External Audio CODEC                |  |

| Table 6.17-1 SD/SDHC/MMC Pad Assignment                               |  |

#### 1 GENERAL DESCRIPTION

The NuMicro<sup>®</sup> NUC505 series 32-bit microcontrollers are embedded with ARM<sup>®</sup> Cortex<sup>®</sup>-M4F core for consumer and industrial applications which need high computing power and rich communication interfaces.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4F core within NuMicro<sup>®</sup> NUC505 series can run up to 100 MHz and support DSP extensions and Floating Point Unit (FPU) function. The NuMicro<sup>®</sup> NUC505 series supports 128 Kbytes embedded SRAM with zero-wait state and 512 KB/ 2 Mbytes embedded SPI Flash memory, and is equipped with plenty of high performance peripheral devices, such as 24-bit Audio CODEC, USB2.0 High-speed Device, USB2.0 Full-speed Host, and other peripheral.

The NuMicro<sup>®</sup> NUC505 series is suitable for a wide range of applications such as:

- Audio and Wireless Audio Applications

- Thermal printerDid not find any incorrect format

- GPS Tracker / VTDR (Vehicle Travelling Data Recorder)

- Others high performance or data intensive computing applications

#### **Key Features:**

- Core

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4F core running up to 100 MHz (with DSP and FPU)

- Memory

- 128 KB of SRAM with zero-wait state

- 512 KB/ 2 MB of SPI Flash

- Security for code protection

- 128-bit key for code protection against pirating

- Up to 15 times programming the key

- Clock Control

- 12 MHz crystal oscillator input

- Up to two PLLs for system clock and Audio

- Up to 12 Communication interfaces

- USB 2.0 HS Device interface

- Up to two USB 2.0 FS Host interfaces

- Up to three UARTs

- Up to three SPIs

- Up to two I<sup>2</sup>C interfaces (up to 1 MHz)

- SD Host

- GPIO

- Supports up to 25/35/52 GPIOs for QFN88/LQFP64/LQFP48 respectively

- Timer

- Supports four sets of 32-bit timers

- Supports two watchdog timers

- (Independent and Window)

- RTC

- Supports external power pin V<sub>BAT</sub>

- 32 bytes spare registers

- Internal 32.768 kHz RC with calibration

- I<sup>2</sup>S

- Supports Master or Slave mode operation

- Supports PCM mode A, PCM mode B, I<sup>2</sup>S and MSB justified data format

- Supports DMA mode

- Audio CODEC

- Embedded Stereo 24-bit Sigma-Delta CODEC

- MIC/LINE-In-THDN: -80 dB, Dynamic Range SNR: 90 dB (A-Weighted)

- Headphone Output-THDN:-60dB, Dynamic Range SNR: 93 dB (A-Weighted)

- Sample Rate: 8 kHz to 96 kHz

- 12-bit ADC

- Analog input voltage range:  $0 \sim AV_{DD}$

- Supports single 12-bit SAR ADC conversion

- Up to 8 channels

- Up to 1 MSPS conversion with ADC\_CH1, and up to 200 kSPS with other channels (except ADC\_CH0).

- Built-in LDO with operating voltage 3.3V

- Low Voltage Detector (LVD) – With 2 levels: 2.8V / 2.6V

- Low Voltage Reset (LVR)

- Threshold voltage level: 2.4 V

- Packages

- LQFP48, LQFP64, QFN88

- Temperature range: -40°C~+85°C

#### 2 FEATURES

#### 2.1 NUC505 Features

#### Core

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4F core running up to 100 MHz

- Supports DSP extension with hardware divider

- Supports IEEE 754 compliant Floating Point Unit (FPU)

- Supports Memory Protection Unit (MPU)

- One 24-bit system timer

- Supports Power-down mode by WFI and WFE instructions

- Single-cycle 32-bit hardware multiplier

- Supports programmable 16 level priorities of Nested Vectored Interrupt Controller (NVIC)

- Supports programmable mask-able interrupts

- Boots from SPI Flash Memory or USB Device

- SRAM Memory

- 128 KB embedded SRAM with zero-wait state

- Supports byte-, half-word- and word-access

- •SPI Memory Interface Controller

- Supports external SPI Flash memory

- Supports code protection

- Supports DMA mode for code transfer from SPI Flash memory to SRAM

- Supports CPU direct read from SPI Flash memory.

- Supports standard (1-bit), dual (2-bit), and quad (4-bit) I/O transfer mode

- Supports general SPI master interface protocol

- Embedded SPI Flash

- 512 KB/ 2 MB SPI Flash

- Configurable program code/data allocation

- Supports 2-wired ICP update through SWD/ICE interface

- Supports ISP update

- Supports standard (1-bit), dual (2-bit), and quad (4-bit) I/O transfer mode

- Supports 100 MHz clock for standard I/O transfer mode

- Supports 80 MHz clock for dual and quad I/O transfer mode

- Security for code protection

- 128-bit key for code protection against pirating

- Up to 15 times programming of the key

- Clock Control

- Built-in 32.768 kHz internal low speed RC oscillator (LIRC) for RTC function,

Watchdog timer and wake-up operation

- Supports 32.768 kHz external low speed crystal oscillator (LXT) for RTC function and low-power system operation

- Supports 12 MHz external high speed crystal oscillator (HXT) for precise timing operation

- Supports one PLL up to 240 MHz for high performance system operation. The external high speed crystal oscillator (HXT) is used as the clock source for the PLL.

●l<sup>2</sup>S

- Supports Master or Slave mode operation

- Internal PLL for frequency adjustment

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports Mono and Stereo audio data

- Supports PCM mode A, PCM mode B, I<sup>2</sup>S and MSB justified data format

- Each provides two 16-word FIFO data buffers, one for transmitting and the other for receiving

- Generates interrupt requests when buffer levels cross a programmable boundary

- Supports DMA mode

- Interface with internal or external audio CODEC

- Audio CODEC

- Embedded Stereo 24-bit Sigma-Delta CODEC output

- ADC-THDN: -80 dB, Dynamic Range SNR: 90 dB (A-Weighted)

- Headphone Output-THDN:-60dB, Dynamic Range SNR: 93 dB (A-Weighted)

- Sample Rate: 8 kHz to 96 kHz

- USB 2.0 High-speed device

- 12 programmable endpoints for Control, Bulk IN/OUT, Interrupt and Isochronous transfers

- 2K-byte buffer

- Auto suspend function

- Remote wake-up capability

- USB 2.0 Full-speed host

- Fully compliant with USB revision 1.1 specification

- Open Host Controller Interface (OHCI) revision 1.0 compatible

- Full-speed (12Mbps) and Low-speed (1.5Mbps) device supported

- Control, Bulk, Interrupt and Isochronous transfers supported

- SD Host Interface

- Supports SD (Secure Digital) card and SD\_HOST interface

- Compliant with SD Memory Card Specification Version 2.0

## ηυνοτοη

- Supports 1 and 4-bit modes

- Supports 50 MHz to achieve 200 Mbps at 3.3V operation

- Supports DMA master

- ●Timer

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit prescale counter

- Independent clock source for each timer

- Provides One-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function to count the event from external pin

- Supports input capture function to capture or reset counter value

- Watchdog Timer

- Supports multiple clock sources from LIRC (default selection), HXT and LXT

- 8 selectable time-out period from 1.6ms ~ 26.0sec (depending on clock source)

- Interrupt or reset selectable on watchdog time-out

- Window Watchdog Timer

- Supports multiple clock sources from LIRC (default selection), HXT and LXT

- Window set by 6-bit counter with 11-bit prescale

- Interrupt or reset selectable on time-out

- ●GPIO

- Four I/O modes

- CMOS/Schmitt trigger input selectable

- I/O pin configured as interrupt source with edge trigger setting

- Supports 5V-tolerance function (except PA.7~PA.0 and PD.4~PD.2 only support 3.3 V)

- Supports up to 52/35(34)/25(18) GPIOs for QFN88/LQFP64/LQFP48 respectively

- ●UART

- Supports up to three UARTs UART0, UART1 and UART2

- Supports 16-byte FIFOs with programmable level trigger with UART0

- Supports 64-byte FIFOs with programmable level trigger with UART1 and UART2

- Supports auto flow control (nCTS and nRTS) with UART1 and UART2

- Supports IrDA (SIR) function

- Supports RS-485 9-bit mode and direction control

- UART1 and UART2 support LIN function

- Programmable baud-rate generator up to 1/16 system clock

- Supports nCTS and data wake-up function

- ●SPI

- Supports two sets of SPI controller SPI0 and SPI1

- Supports Master or Slave mode operation

- Supports 1-bit Transfer mode

- Configurable bit length of a transfer word from 8 to 32-bit

- Provides separate 8-level depth transmit and receive FIFO buffers

- Supports MSB first or LSB first transfer sequence

- Supports the byte reorder function

- Supports Byte or Word Suspend mode

- Supports 3-wired, no slave select signal, bi-direction interface

- Supports up to 50 MHz

●l<sup>2</sup>C

- Supports up to two sets of I<sup>2</sup>C devices

- Supports Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow versatile rate control

- Supports multiple address recognition (four slave address with mask option)

- Supports SMBus and PMBus

- Supports speed up to 1Mbps

- Supports multi-address Power-down wake-up function

- ●PWM

\_

- Four 16-bit timers

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Capture and compare function

- •RTC

- Supports external power pin RTC\_VDD33

- Supports 32.768 kHz crystal oscillation circuit

- Supports RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Supports Alarm registers (second, minute, hour, day, month, year)

- Supports 32 bytes spare registers

- Wake up from Deep Power-down mode or from Power-down mode

- Supports wake up from Power-down mode by input pin

## ηυνοτοη

- Supports chip Power-off by register setting

- Supports Power-on time-out for low battery protection

- Analog to Digital Converter

- Analog input voltage range: 0~ AV<sub>DD</sub>

- Supports single 12-bit SAR ADC conversion

- 12-bit resolution and 10-bit accuracy is guaranteed

- Up to 1MSPS conversion with ADC\_CH1, and up to 200 kSPS with others (except ADC\_CH0).

- Up to 8 external single-ended analog input channels

- Supports single ADC interrupt

- An A/D conversion can be triggered by software control

- •Built-in LDO with operating voltage 3.3V

- •Low Voltage Detector (LVD)

- With 2 levels: 2.8V / 2.6V

- •Low Voltage Reset (LVR)

- Threshold voltage level: 2.4 V

- Power Management

- Advanced power management including Deep Power-down, Power-down, Idle and Normal Operating modes

- Normal Operating mode

- CPU runs normally and all clocks on; the current consumption is around 46 mA (at 96 MHz CPU clock)

- Idle mode

- CPU clock stop, and all other clocks on

- Power-down mode

- All clocks stop, except LXT and LIRC, with SRAM retention; the current consumption is around 700 uA

- Deep Power-down mode

- All clocks stop, except LXT and LIRC, without SRAM retention; the current consumption is around 7 uA

- ●Operating Temperature: -40°C ~+85°C

- Packages

- All Green package (RoHS)

- QFN 88-pin (10mm x 10mm)

- LQFP 64-pin (7mm x 7mm)

- LQFP 48-pin (7mm x 7mm)

- QFN 48-pin (7mm x 7mm)

#### **3 ABBREVIATIONS**

#### 3.1 Abbreviations

| Acronym | Description                                      |

|---------|--------------------------------------------------|

| ADC     | Analog-to-Digital Converter                      |

| АРВ     | Advanced Peripheral Bus                          |

| АНВ     | Advanced High-Performance Bus                    |

| DMA     | Direct Memory Access                             |

| FIFO    | First In, First Out                              |

| FPU     | Floating Point Unit                              |

| GPIO    | General-Purpose Input/Output                     |

| HCLK    | The Clock of Advanced High-Performance Bus       |

| НХТ     | 12 MHz External High Speed Crystal Oscillator    |

| ICP     | In Circuit Programming                           |

| ISP     | In System Programming                            |

| LDO     | Low Dropout Regulator                            |

| LIN     | Local Interconnect Network                       |

| LIRC    | 32.768 kHz Internal Low Speed RC Oscillator      |

| LXT     | 32.768 kHz External Low Speed Crystal Oscillator |

| LVD     | Low Voltage Detection                            |

| MPU     | Memory Protection Unit                           |

| NVIC    | Nested Vectored Interrupt Controller             |

| PCLK    | The Clock of Advanced Peripheral Bus             |

| PLL     | Phase-Locked Loop                                |

| PWM     | Pulse Width Modulation                           |

| SD      | Secure Digital                                   |

| SPI     | Serial Peripheral Interface                      |

| SPIM    | Serial Master Interface Controller               |

| SPS     | Samples per Second                               |

| TMR     | Timer Controller                                 |

| UART    | Universal Asynchronous Receiver/Transmitter      |

| USB     | Universal Serial Bus                             |

| WDT     | Watchdog Timer                                   |

| WWDT    | Window Watchdog Timer                            |

Table 3.1-1 List of Abbreviations

#### **4** PARTS INFORMATION LIST AND PIN CONFIGURATION

#### 4.1 Selection Guide

#### 4.1.1 NuMicro<sup>®</sup> NUC505 Base Series Selection Guide

[1]:  $\sqrt[*]{}$  marked in the table means that only NUC505DS13Y supports Headphone Out.

[2]: The packages are not pin-to-pin compatible even though they are the same packages.

LQFP64\*: 7x7mm

| ē           | (KB)              | 3)        | (B)          |     | 8it)           |     | Conn    | ectivit | y    |     | Device       | Host         | it)          | CODEC <sup>[1]</sup> | MIC       | it)          |              |              | 2]                     |

|-------------|-------------------|-----------|--------------|-----|----------------|-----|---------|---------|------|-----|--------------|--------------|--------------|----------------------|-----------|--------------|--------------|--------------|------------------------|

| Part Number | Serial Flash (KB) | SRAM (KB) | ISP ROM (KB) | 0/1 | Timer (32-Bit) | l²C | SD HOST | IdS     | UART | l²S | USB 2.0 HS D | USB 2.0 FS I | PWM (16-Bit) | 24-Bit Audio C0      | DIGITAL M | ADC (12-Bit) | RTC          | ISP/ICP      | Package <sup>[2]</sup> |

| NUC505DLA   | 512               | 128       | 8            | 18  | 4              | 2   | -       | 2       | 2    | 1   | 1            | -            | -            | $\checkmark$         | 1         | 5CH          | -            | $\checkmark$ | LQFP48                 |

| NUC505DL13Y | 2048              | 128       | 8            | 25  | 4              | 2   | 1       | 3       | 3    | 1   | 1            | 1            | 4            | -                    | 1         | 5CH          | $\checkmark$ | $\checkmark$ | LQFP48                 |

| NUC505YLA   | 512               | 128       | 8            | 18  | 4              | 2   | -       | 2       | 2    | 1   | 1            | -            | -            | $\checkmark$         | 1         | 5CH          | -            | $\checkmark$ | QFN48                  |

| NUC505YLA2Y | 512               | 128       | 8            | 25  | 4              | 2   | 1       | 3       | 3    | 1   | 1            | 1            | 4            | -                    | 1         | 5CH          | $\checkmark$ | $\checkmark$ | QFN48                  |

| NUC505DSA   | 512               | 128       | 8            | 34  | 4              | 2   | 1       | 3       | 3    | 1   | 1            | 1            | 4            | $\checkmark$         | 1         | 5CH          | -            | $\checkmark$ | LQFP64*                |

| NUC505DS13Y | 2048              | 128       | 8            | 35  | 4              | 2   | 1       | 3       | 3    | 1   | 1            | 1            | 4            | √*                   | 1         | 8CH          | $\checkmark$ | $\checkmark$ | LQFP64*                |

| NUC505YO13Y | 2048              | 128       | 8            | 52  | 4              | 2   | 1       | 3       | 3    | 1   | 1            | 2            | 4            | $\checkmark$         | 1         | 8CH          | $\checkmark$ | $\checkmark$ | QFN88                  |

Table 4.1-1 NuMicro® NUC505 Base Series Selection Guide

### 4.1.2 NuMicro<sup>®</sup> NUC505 Base Series Naming Rule

| Nuvoton       32-bit Microcontroller       CPU Core       Cortex®-M4F       Package Type                   | Packaging Materi<br>G: Pb-free<br>N: Green package<br>Y: MCP<br>T: For testing |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| B: BGA<br>D: LQFP<br>Y: QFN                                                                                | Elash ROM                                                                      |

| B: BGA<br>D: LQFP<br>Y: QFN<br>Package Dimension                                                           | Flash ROM<br>1: 2MByte 2: 4MByte                                               |

| B: BGA<br>D: LQFP<br>Y: QFN<br>Package Dimension<br>L: 48pin 7x7mm S: 64pin 7X7mm                          | 1: 2MByte 2: 4MByte                                                            |

| B: BGA<br>D: LQFP<br>Y: QFN<br>Package Dimension<br>L: 48pin 7x7mm<br>R: 64pin 10x10mm<br>O: 88pin 10x10mm | 1: 2MByte 2: 4MByte<br>3: 8MByte 4: 16MByte                                    |

| B: BGA<br>D: LQFP<br>Y: QFN<br>Package Dimension<br>L: 48pin 7x7mm S: 64pin 7X7mm                          | 1: 2MByte 2: 4MByte                                                            |

Figure 4.1-1 NuMicro® NUC505 Base Series Selection Code

#### 4.2 Pin Configuration

### 4.2.1 NuMicro<sup>®</sup> NUC505DLA LQFP 48-pin

Figure 4.2-1 NuMicro<sup>®</sup> NUC505DLA LQFP 48-pin Diagram

### 4.2.2 NuMicro<sup>®</sup> NUC505DL13Y LQFP 48-pin

Figure 4.2-2 NuMicro<sup>®</sup> NUC505DL13Y LQFP 48-pin Diagram

#### 4.2.3 NuMicro<sup>®</sup> NUC505YLA QFN 48-pin

Figure 4.2-3 NuMicro® NUC505YLA QFN 48-pin Diagram

### **NUC505**

### 4.2.4 NuMicro<sup>®</sup> NUC505YLA2Y QFN 48-pin

Figure 4.2-4 NuMicro<sup>®</sup> NUC505YLA2Y QFN 48-pin Diagram

### 4.2.5 NuMicro<sup>®</sup> NUC505DSA LQFP 64-pin

Figure 4.2-5 NuMicro® NUC505DSA LQFP 64-pin Diagram

## ηυνοΤοη

### 4.2.6 NuMicro<sup>®</sup> NUC505DS13Y LQFP 64-pn

Figure 4.2-6 NuMicro<sup>®</sup> NUC505DS13Y LQFP 64-pin Diagram

#### 4.2.7 NuMicro® NUC505YO13Y QFN 88-pin

Figure 4.2-7 NuMicro® NUC505YO13Y QFN 88-pin Diagram

#### 4.3 Pin Description

#### 4.3.1 NuMicro<sup>®</sup> NUC505DLA LQFP 48-pin Description

MFP\* = Multi-function pin. (Refer to section SYS\_GPx\_MFPL and SYS\_GPx\_MFPH)

PA.0 MFP0 means SYS\_GPA\_MFPL[2:0]=0x0.

PA.9 MFP5 means SYS\_GPA\_MFPH[6:4]=0x5.

| Pin No. | Pin Name            | Туре | MFP* | Description                                                                                          |

|---------|---------------------|------|------|------------------------------------------------------------------------------------------------------|

| 1       | nRESET              | Ι    | MFP0 | External reset input: active LOW, with an internal pull-up. Set this pin low reset to initial state. |

| 2       | ICE_CLK             | 0    | MFP0 | Serial wired debugger clock pin. (In ICE mode)                                                       |

|         | PD.0                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SCL            | 0    | MFP2 | l <sup>2</sup> C0 clock pin.                                                                         |

| 3       | ICE_DAT             | I/O  | MFP0 | Serial wired debugger data pin. (In ICE mode)                                                        |

|         | PD.1                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SDA            | I/O  | MFP2 | I <sup>2</sup> C0 data input/output pin.                                                             |

| 4       | PB.14               | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | USBH1_D+            | I/O  | MFP1 | USB host-lite 1differential signal D+.                                                               |

|         | I2C1_SCL            | 0    | MFP2 | I2C1 clock pin.                                                                                      |

| 5       | PB.15               | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | USBH1_D-            | I/O  | MFP1 | USB host-lite 1 differential signal D                                                                |

|         | I2C1_SDA            | I/O  | MFP2 | I2C1 data input/output pin.                                                                          |

| 6       | V <sub>DD</sub>     | А    | MFP0 | Power supply for I/O ports, DC 3.3V.                                                                 |

| 7       | XT1_IN              | I    | MFP0 | External 12 MHz (high speed) crystal input pin.                                                      |

| 8       | XT1_OUT             | 0    | MFP0 | External 12 MHz (high speed) crystal output pin.                                                     |

| 9       | V <sub>DD12</sub>   | А    | MFP0 | Power supply for I/O ports, DC 1.2V                                                                  |

| 10      | USB_D-              | А    | MFP0 | USB differential signal D                                                                            |

| 11      | USB_D+              | А    | MFP0 | USB differential signal D+.                                                                          |

| 12      | AV <sub>DDUSB</sub> | А    | MFP0 | Power supply for analog USB, DC 3.3V.                                                                |

| 13      | USB_REXT            | А    | MFP0 | 12.1 K $\Omega$ used internally for USB circuitry.                                                   |

| 14 | PA.8            | I/O | MFP0     | General purpose digital I/O pin.           |

|----|-----------------|-----|----------|--------------------------------------------|

|    | SPIM_SS         | 0   | MFP1     | SPIM slave select pin.                     |

|    | I2S_LRCLK       | I/O | MFP2     | l <sup>2</sup> S left right channel clock. |

|    | UART1_TXD       | 0   | MFP3     | Data transmitter output pin for UART1.     |

| 15 | PA.9            | I/O | MFP0     | General purpose digital I/O pin.           |

|    | SPIM_CLK        | 0   | MFP1     | SPIM serial clock pin.                     |

|    | I2S_BCLK        | I/O | MFP2     | l <sup>2</sup> S bit clock pin.            |

|    | UART1_RXD       | I   | MFP3     | Data receiver input pin for UART1.         |

|    | SYSCFG[0]       | I   | MFP0     | System configuration setting bit 0.        |

| 16 | PA.10           | I/O | MFP0     | General purpose digital I/O pin.           |

|    | SPIM_MOSI       | I/O | MFP1     | SPIM MOSI (Master Out, Slave In) pin.      |

|    | I2C1_SCL        | 0   | MFP2     | I2C1 clock pin.                            |

|    | SD_CLK          | 0   | MFP4     | SD/SDH mode - clock.                       |

|    | SYSCFG[1]       | I   | MFP0     | System configuration setting bit 1.        |

| 17 | PA.11           | I/O | MFP0     | General purpose digital I/O pin.           |

|    | SPIM_MISO       | I/O | MFP1     | SPIM MISO (Master In, Slave Out) pin.      |

|    | I2C1_SDA        | I/O | MFP2     | I2C1 data input/output pin.                |

|    | SD_CMD          | I   | MFP4     | SD/SDH mode – command/response.            |

| 18 | V <sub>DD</sub> | А   | MFP0     | Power supply for I/O ports, DC 3.3V.       |

| 19 | PB.0            | I/O | MFP0     | General purpose digital I/O pin.           |

|    | I2C0_SCL        | 0   | MFP2     | I2C0 clock pin.                            |

|    | UART0_TXD       | 0   | MFP3     | Data transmitter output pin for UART0.     |

|    | SD_DAT2         | I/O | MFP4     | SD/SDH mode data line bit 2.               |

| 20 | PB.1            | I/O | MFP0     | General purpose digital I/O pin.           |

|    | I2C0_SDA        | I/O | MFP2     | I2C0 data input/output pin.                |

|    | UART0_RXD       | I   | MFP3     | Data receiver input pin for UART0.         |

|    | SD_DAT3         | I/O | MFP4     | SD/SDH mode data line bit 3.               |

|    |                 | 1/0 | IVII 7 4 |                                            |

| 21 | PB.2                  | I/O | MFP0 | General purpose digital I/O pin.                  |

|----|-----------------------|-----|------|---------------------------------------------------|

| 21 |                       |     |      |                                                   |

|    | SPI0_SS               | 0   | MFP1 | SPI0 slave select pin.                            |

|    | SD_CMD                | I   | MFP4 | SD/SDH mode – command/response.                   |

| 22 | PB.3                  | I/O | MFP0 | General purpose digital I/O pin.                  |

|    | SPI0_CLK              | 0   | MFP1 | SPI0 serial clock pin.                            |

|    | SD_CLK                | 0   | MFP4 | SD/SDH mode – clock.                              |

|    | SYSCFG[2]             | I   | MFP0 | System configuration setting bit 2.               |

| 23 | PB.4                  | I/O | MFP0 | General purpose digital I/O pin.                  |

|    | SPI0_MOSI             | 0   | MFP1 | SPI0 MOSI (Master Out, Slave In) pin.             |

|    | SYSCFG[3]             | I   | MFP0 | System configuration setting bit 3.               |

| 24 | PB.5                  | I/O | MFP0 | General purpose digital I/O pin.                  |

|    | SPI0_MISO             | I   | MFP1 | SPI0 MISO (Master In, Slave Out) pin.             |

|    | SD_nCD                | I   | MFP4 | SD/SDH mode – card detect.                        |

| 25 | USB_VBUS33            | I   | MFP0 | Detects whether USB is plug-in.                   |

| 26 | V <sub>ss</sub>       | А   | MFP0 | Ground                                            |

| 27 | AV <sub>DDHP</sub>    | А   | MFP0 | Power supply for analog CODEC headphone, DC 3.3V. |

| 28 | LHPOUT                | А   | MFP0 | Headphone left channel output pin.                |

| 29 | RHPOUT                | А   | MFP0 | Headphone right channel output pin.               |

| 30 | AV <sub>SSHP</sub>    | А   | MFP0 | Ground for analog CODEC headphone.                |

| 31 | VMID                  | А   | MFP0 | Headphone reference power.                        |

| 32 | AV <sub>DDCODEC</sub> | А   | MFP0 | Power supply for analog CODEC, DC 3.3V.           |

| 33 | MIC0_P                | А   | MFP0 | Microphone 0 positive input.                      |

| 34 | MIC0_N                | А   | MFP0 | Microphone 0 negative input.                      |

| 35 | MIC_BIAS              | А   | MFP0 | CODEC left line-in channel or Microphone bias.    |

| 36 | V <sub>DD12</sub>     | A   | MFP0 | Power supply for I/O ports, DC 1.2V               |

| 37 | PD.4                  | I/O | MFP0 | General purpose digital I/O pin.                  |

|    | RLINEIN               | А   | MFP1 | CODEC right line-in channel.                      |

|    |                       | ~   |      |                                                   |

| <b>NUC505</b> |

|---------------|

|---------------|

|    |                     |     | -    |                                           |

|----|---------------------|-----|------|-------------------------------------------|

| 38 | AV <sub>DDADC</sub> | А   | MFP0 | Power supply for analog SAR-ADC, DC 3.3V. |

| 39 | AV <sub>SSADC</sub> | А   | MFP0 | Ground pin for analog SAR-ADC.            |

| 40 | PA.0                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH0             | А   | MFP1 | ADC channel 0 analog input.               |

| 41 | PA.1                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH1             | А   | MFP1 | ADC channel 1 analog input.               |

| 42 | PA.2                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH2             | А   | MFP1 | ADC channel 2 analog input.               |

|    | I2S_MCLK            | 0   | MFP2 | I <sup>2</sup> S master clock output pin. |

| 43 | PA.3                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH3             | А   | MFP1 | ADC channel 3 analog input.               |

|    | I2S_DI              | I   | MFP2 | I <sup>2</sup> S data input.              |

| 44 | PA.4                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH4             | А   | MFP1 | ADC channel 4 analog input.               |

|    | I2S_DO              | 0   | MFP2 | l <sup>2</sup> S data output.             |

| 45 | V <sub>DD12</sub>   | А   | MFP0 | Power supply for I/O ports, DC 1.2V       |

| 46 | V <sub>DD</sub>     | А   | MFP0 | Power supply, DC 3.3V.                    |

| 47 | LDO_CAP             | А   | MFP0 | LDO output pin.                           |

| 48 | V <sub>SS</sub>     | А   | MFP0 | Ground.                                   |

### 4.3.2 NuMicro<sup>®</sup> NUC505DL13Y LQFP 48-pin Description

MFP\* = Multi-function pin. (Refer to section SYS\_GPx\_MFPL and SYS\_GPx\_MFPH)

PA.0 MFP0 means SYS\_GPA\_MFPL[2:0]=0x0.

PA.9 MFP5 means SYS\_GPA\_MFPH[6:4]=0x5.

| Pin No. | Pin Name            | Туре | MFP* | Description                                                                                          |

|---------|---------------------|------|------|------------------------------------------------------------------------------------------------------|

| 1       | nRESET              | Ι    | MFP0 | External reset input: active LOW, with an internal pull-up. Set this pin low reset to initial state. |

| 2       | ICE_CLK             | 0    | MFP0 | Serial wired debugger clock pin. (In ICE mode)                                                       |

|         | PD.0                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SCL            | 0    | MFP2 | l²C0 clock pin.                                                                                      |

| 3       | ICE_DAT             | I/O  | MFP0 | Serial wired debugger data pin. (In ICE mode)                                                        |

|         | PD.1                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SDA            | I/O  | MFP2 | l <sup>2</sup> C0 data input/output pin.                                                             |

| 4       | PB.13               | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | SPI1_MISO           | Ι    | MFP1 | SPI1 MISO (Master In, Slave Out) pin.                                                                |

|         | USBH1_D-            | I/O  | MFP2 | USB host-lite 1 differential signal D                                                                |

|         | UART2_nRTS          | 0    | MFP3 | Request to Send output pin for UART2.                                                                |

|         | PWM_CH3             | I/O  | MFP4 | PWM channel3 output/capture input.                                                                   |

| 5       | V <sub>DD</sub>     | А    | MFP0 | Power supply for I/O ports, DC 3.3V.                                                                 |

| 6       | V <sub>SS</sub>     | А    | MFP0 | Ground.                                                                                              |

| 7       | XT1_IN              | I    | MFP0 | External 12 MHz (high speed) crystal input pin.                                                      |

| 8       | XT1_OUT             | 0    | MFP0 | External 12 MHz (high speed) crystal output pin.                                                     |

| 9       | V <sub>DD12</sub>   | А    | MFP0 | Power supply for I/O ports, DC 1.2V                                                                  |

| 10      | USB_D-              | A    | MFP0 | USB differential signal D                                                                            |

| 11      | USB_D+              | А    | MFP0 | USB differential signal D+.                                                                          |

| 12      | AV <sub>DDUSB</sub> | А    | MFP0 | Power supply for analog USB, DC 3.3V.                                                                |

| 13      | USB_REXT            | А    | MFP0 | 12.1 K $\Omega$ used internally for USB circuitry.                                                   |

| 14      | V <sub>BAT</sub>    | А    | MFP0 | Power supply by batteries for RTC, DC 3.3V.                                                          |

| 15 | RTC_RPWR        | 0   | MFP0 | Enable external power control source when active high. |

|----|-----------------|-----|------|--------------------------------------------------------|

|    |                 | -   |      |                                                        |

| 16 | RTC_nRWAKE      | I   | MFP0 | System power enable trigger when active low.           |

| 17 | PA.8            | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | SPIM_SS         | 0   | MFP1 | SPIM slave select pin.                                 |

|    | I2S_LRCLK       | I/O | MFP2 | I <sup>2</sup> S left right channel clock.             |

|    | UART1_TXD       | 0   | MFP3 | Data transmitter output pin for UART1.                 |

| 18 | PA.9            | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | SPIM_CLK        | 0   | MFP1 | SPIM serial clock pin.                                 |

|    | I2S_BCLK        | I/O | MFP2 | l <sup>2</sup> S bit clock pin.                        |

|    | UART1_RXD       | I   | MFP3 | Data receiver input pin for UART1.                     |

|    | SYSCFG[0]       | I   | MFP0 | System configuration setting bit 0.                    |

| 19 | PA.10           | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | SPIM_MOSI       | I/O | MFP1 | SPIM MOSI (Master Out, Slave In) pin.                  |

|    | I2C1_SCL        | 0   | MFP2 | I2C1 clock pin.                                        |

|    | SD_CLK          | 0   | MFP4 | SD/SDH mode - clock.                                   |

|    | SYSCFG[1]       | I   | MFP0 | System configuration setting bit 1.                    |

| 20 | PA.11           | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | SPIM_MISO       | I/O | MFP1 | SPIM MISO (Master In, Slave Out) pin.                  |

|    | I2C1_SDA        | I/O | MFP2 | I2C1 data input/output pin.                            |

|    | SD_CMD          | I   | MFP4 | SD/SDH mode – command/response.                        |

| 21 | V <sub>DD</sub> | А   | MFP0 | Power supply for I/O ports, DC 3.3V.                   |

| 22 | PB.0            | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | I2C0_SCL        | 0   | MFP2 | I2C0 clock pin.                                        |

|    | UART0_TXD       | 0   | MFP3 | Data transmitter output pin for UART0.                 |

|    | SD_DAT2         | I/O | MFP4 | SD/SDH mode data line bit 2.                           |

| 23 | PB.1            | I/O | MFP0 | General purpose digital I/O pin.                       |

|    | I2C0_SDA        | I/O | MFP2 | I2C0 data input/output pin.                            |

|    | UART0_RXD   | I   | MFP3 | Data receiver input pin for UART0.                       |

|----|-------------|-----|------|----------------------------------------------------------|

|    | SD_DAT3     | I/O | MFP4 | SD/SDH mode data line bit 3.                             |

| 24 | PB.2        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | SPI0_SS     | 0   | MFP1 | SPI0 slave select pin.                                   |

|    | SD_CMD      | I   | MFP4 | SD/SDH mode – command/response.                          |

| 25 | PB.3        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | SPI0_CLK    | 0   | MFP1 | SPI0 serial clock pin.                                   |

|    | SD_CLK      | 0   | MFP4 | SD/SDH mode – clock.                                     |

|    | SYSCFG[2]   | I   | MFP0 | System configuration setting bit 2.                      |

| 26 | PB.4        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | SPI0_MOSI   | 0   | MFP1 | SPI0 MOSI (Master Out, Slave In) pin.                    |

|    | SYSCFG[3]   | I   | MFP0 | System configuration setting bit 3.                      |

| 27 | PB.5        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | SPI0_MISO   | I   | MFP1 | SPI0 MISO (Master In, Slave Out) pin.                    |

|    | SD_nCD      | I   | MFP4 | SD/SDH mode – card detect.                               |

| 28 | PB.6        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | UART1_TXD   | 0   | MFP3 | Data transmitter output pin for UART1.                   |

|    | SD_DAT0     | I/O | MFP4 | SD/SDH mode data line bit 0.                             |

| 29 | PB.7        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | UART1_RXD   | I   | MFP3 | Data receiver input pin for UART1.                       |

|    | SD_DAT1     | I/O | MFP4 | SD/SDH mode data line bit 1.                             |

| 30 | USB_VBUS33  | I   | MFP0 | Detects whether USB is plug-in.                          |

| 31 | PB.8        | I/O | MFP0 | General purpose digital I/O pin.                         |

|    | USBH_PWEN   | 0   | MFP1 | USB host mode to control an external overcurrent source. |

|    | TM1_CNT_OUT | I/O | MFP2 | Timer1 event counter input/toggle output.                |

|    | UART1_nCTS  | I   | MFP3 | Clear to Send input pin for UART1.                       |

|    | SD_DAT2     | I/O | MFP4 | SD/SDH mode data line bit 2.                             |

| 32 | PB.9                | I/O | MFP0 | General purpose digital I/O pin.          |

|----|---------------------|-----|------|-------------------------------------------|

| 02 |                     |     |      |                                           |

|    | USBH_OVD            |     | MFP1 | USB host bus power over voltage detector. |

|    | TM1_EXT             | I   | MFP2 | Timer1 external capture input.            |

|    | UART1_nRTS          | 0   | MFP3 | Request to Send output pin for UART1.     |

|    | SD_DAT3             | I/O | MFP4 | SD/SDH mode data line bit 3.              |

| 33 | V <sub>ss</sub>     | А   | MFP0 | Ground                                    |

| 34 | AV <sub>DDADC</sub> | А   | MFP0 | Power supply for analog SAR-ADC, DC 3.3V. |

| 35 | AV <sub>SSADC</sub> | А   | MFP0 | Ground pin for analog SAR-ADC.            |

| 36 | PA.0                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH0             | А   | MFP1 | ADC channel 0 analog input.               |

| 37 | PA.1                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH1             | A   | MFP1 | ADC channel 1 analog input.               |

| 38 | PA.2                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH2             | A   | MFP1 | ADC channel 2 analog input.               |

|    | I2S_MCLK            | 0   | MFP2 | I <sup>2</sup> S master clock output pin. |

| 39 | PA.3                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH3             | A   | MFP1 | ADC channel 3 analog input.               |

|    | I2S_DI              | I   | MFP2 | I <sup>2</sup> S data input.              |

| 40 | PA.4                | I/O | MFP0 | General purpose digital I/O pin.          |

|    | ADC_CH4             | А   | MFP1 | ADC channel 4 analog input.               |

|    | I2S_DO              | 0   | MFP2 | l <sup>2</sup> S data output.             |

| 41 | V <sub>DD12</sub>   | А   | MFP0 | Power supply for I/O ports, DC 1.2V       |

| 42 | PB.10               | I/O | MFP0 | General purpose digital I/O pin.          |

|    | SPI1_SS             | 0   | MFP1 | SPI1 slave select pin.                    |

|    | I2C1_SCL            | 0   | MFP2 | I2C1 clock pin.                           |

|    | UART2_TXD           | 0   | MFP3 | Data transmitter output pin for UART2.    |

|    | PWM_CH0             | I/O | MFP4 | PWM channel0 output/capture input.        |

| 43 | PB.11           | I/O | MFP0 | General purpose digital I/O pin.       |

|----|-----------------|-----|------|----------------------------------------|

|    | SPI1_CLK        | 0   | MFP1 | SPI1 serial clock pin.                 |

|    | I2C1_SDA        | I/O | MFP2 | I2C1 data input/output pin.            |

|    | UART2_RXD       | Ι   | MFP3 | Data receiver input pin for UART2.     |

|    | PWM_CH1         | I/O | MFP4 | PWM channel1 output/capture input.     |

| 44 | PB.12           | I/O | MFP0 | General purpose digital I/O pin.       |

|    | SPI1_MOSI       | 0   | MFP1 | SPI1 MOSI (Master Out, Slave In) pin.  |

|    | USBH1_D+        | I/O | MFP2 | USB host-lite 1 differential signal D+ |

|    | UART2_nCTS      | Ι   | MFP3 | Clear to send input pin for UART2.     |

|    | PWM_CH2         | I/O | MFP4 | PWM channel2 output/capture input.     |

| 45 | V <sub>DD</sub> | A   | MFP0 | Power supply for I/O ports, DC 3.3V.   |

| 46 | V <sub>DD</sub> | A   | MFP0 | Power supply, DC 3.3V.                 |

| 47 | LDO_CAP         | А   | MFP0 | LDO output pin.                        |

| 48 | V <sub>SS</sub> | А   | MFP0 | Ground.                                |

#### 4.3.3 NuMicro<sup>®</sup> NUC505YLA QFN 48-pin Description

MFP\* = Multi-function pin. (Refer to section SYS\_GPx\_MFPL and SYS\_GPx\_MFPH)

PA.0 MFP0 means SYS\_GPA\_MFPL[2:0]=0x0.

PA.9 MFP5 means SYS\_GPA\_MFPH[6:4]=0x5.

| Pin No. | Pin Name            | Туре | MFP* | Description                                                                                          |

|---------|---------------------|------|------|------------------------------------------------------------------------------------------------------|

| 1       | nRESET              | I    | MFP0 | External reset input: active LOW, with an internal pull-up. Set this pin low reset to initial state. |

| 2       | ICE_CLK             | 0    | MFP0 | Serial wired debugger clock pin. (In ICE mode)                                                       |

|         | PD.0                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SCL            | 0    | MFP2 | l²C0 clock pin.                                                                                      |

| 3       | ICE_DAT             | I/O  | MFP0 | Serial wired debugger data pin. (In ICE mode)                                                        |

|         | PD.1                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | I2C0_SDA            | I/O  | MFP2 | l <sup>2</sup> C0 data input/output pin.                                                             |

| 4       | PB.14               | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | USBH1_D+            | I/O  | MFP1 | USB host-lite 1differential signal D+.                                                               |

|         | I2C1_SCL            | 0    | MFP2 | I2C1 clock pin.                                                                                      |

| 5       | PB.15               | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|         | USBH1_D-            | I/O  | MFP1 | USB host-lite 1 differential signal D                                                                |

|         | I2C1_SDA            | I/O  | MFP2 | I2C1 data input/output pin.                                                                          |

| 6       | V <sub>DD</sub>     | А    | MFP0 | Power supply for I/O ports, DC 3.3V.                                                                 |

| 7       | XT1_IN              | I    | MFP0 | External 12 MHz (high speed) crystal input pin.                                                      |

| 8       | XT1_OUT             | 0    | MFP0 | External 12 MHz (high speed) crystal output pin.                                                     |

| 9       | V <sub>DD12</sub>   | А    | MFP0 | Power supply for I/O ports, DC 1.2V                                                                  |

| 10      | USB_D-              | А    | MFP0 | USB differential signal D                                                                            |

| 11      | USB_D+              | А    | MFP0 | USB differential signal D+.                                                                          |

| 12      | AV <sub>DDUSB</sub> | А    | MFP0 | Power supply for analog USB, DC 3.3V.                                                                |

| 13      | USB_REXT            | А    | MFP0 | 12.1 K $\Omega$ used internally for USB circuitry.                                                   |

| 14      | PA.8                | I/O  | MFP0 | General purpose digital I/O pin.                                                                     |

|    | SPIM_SS         | 0   | MFP1 | SPIM slave select pin.                     |

|----|-----------------|-----|------|--------------------------------------------|

|    | I2S_LRCLK       | I/O | MFP2 | I <sup>2</sup> S left right channel clock. |

|    | UART1_TXD       | 0   | MFP3 | Data transmitter output pin for UART1.     |

| 45 |                 | -   |      |                                            |

| 15 | PA.9            | I/O | MFP0 | General purpose digital I/O pin.           |

|    | SPIM_CLK        | 0   | MFP1 | SPIM serial clock pin.                     |

|    | I2S_BCLK        | I/O | MFP2 | I <sup>2</sup> S bit clock pin.            |

|    | UART1_RXD       | I   | MFP3 | Data receiver input pin for UART1.         |

|    | SYSCFG[0]       | I   | MFP0 | System configuration setting bit 0.        |

| 16 | PA.10           | I/O | MFP0 | General purpose digital I/O pin.           |

|    | SPIM_MOSI       | I/O | MFP1 | SPIM MOSI (Master Out, Slave In) pin.      |

|    | I2C1_SCL        | 0   | MFP2 | I2C1 clock pin.                            |

|    | SD_CLK          | 0   | MFP4 | SD/SDH mode - clock.                       |

|    | SYSCFG[1]       | I   | MFP0 | System configuration setting bit 1.        |

| 17 | PA.11           | I/O | MFP0 | General purpose digital I/O pin.           |

|    | SPIM_MISO       | I/O | MFP1 | SPIM MISO (Master In, Slave Out) pin.      |

|    | I2C1_SDA        | I/O | MFP2 | I2C1 data input/output pin.                |

|    | SD_CMD          | I   | MFP4 | SD/SDH mode – command/response.            |

| 18 | V <sub>DD</sub> | А   | MFP0 | Power supply for I/O ports, DC 3.3V.       |

| 19 | PB.0            | I/O | MFP0 | General purpose digital I/O pin.           |

|    | I2C0_SCL        | 0   | MFP2 | I2C0 clock pin.                            |

|    | UART0_TXD       | 0   | MFP3 | Data transmitter output pin for UART0.     |

|    | SD_DAT2         | I/O | MFP4 | SD/SDH mode data line bit 2.               |

| 20 | PB.1            | I/O | MFP0 | General purpose digital I/O pin.           |

|    | I2C0_SDA        | I/O | MFP2 | I2C0 data input/output pin.                |

|    | UART0_RXD       | I   | MFP3 | Data receiver input pin for UART0.         |

|    | SD_DAT3         | I/O | MFP4 | SD/SDH mode data line bit 3.               |

| 21 | PB.2            | I/O | MFP0 | General purpose digital I/O pin.           |

|    | SPI0_SS             | 0   | MFP1 | SPI0 slave select pin.                            |

|----|---------------------|-----|------|---------------------------------------------------|