## M2351 Series Hardware Design Guide

Application Note for 32-bit NuMicro<sup>®</sup> Family

#### **Document Information**

| Abstract | This M2351 hardware design guide is intended for hardware system designers who require a hardware implementation overview for a M2351 based system. |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Apply to | NuMicro <sup>®</sup> M2351 series.                                                                                                                  |  |

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

### Table of Contents

| 1 | OVERVIEW                                       |

|---|------------------------------------------------|

| 2 | M2351 FEATURES                                 |

| 3 | BLOCK DIAGRAM16                                |

| 4 | POWER SUPPLIES17                               |

|   | 4.1 Power Supply Scheme                        |

|   | 4.2 Power Modes and Wake-up Sources            |

|   | 4.3 System Power Distribution23                |

| 5 | EXTERNAL CRYSTAL CLOCK25                       |

|   | 5.1 External Crystal Sources                   |

|   | 5.2 External Crystal PCB Design Guide          |

| 6 | ADC                                            |

|   | 6.1 Analog Signals                             |

|   | 6.2 Power Supply Block                         |

|   | 6.3 ADC Voltage Reference Source               |

|   | 6.3.1V <sub>REF</sub> Pin                      |

|   | 6.3.2Internal V <sub>REF</sub>                 |

| 7 | DAC                                            |

|   | 7.1 Power Supply Block                         |

| 8 | USB                                            |

|   | 8.1 USB Device                                 |

|   | 8.1.1USB 1.1 Device Controller (USBD)          |

|   | 8.2 USB Host                                   |

|   | 8.2.1USB 2.0 Full-speed Host Controller (USBH) |

|   | 8.3 USB OTG                                    |

|   | 8.3.1USB On-The-Go (OTG)                       |

|   | 8.4 USB PCB Design Guide                       |

|    | 8.4.1 Through Hole for D+ and D- |    |

|----|----------------------------------|----|

|    | 8.4.2Signal Trace for D+ and D-  |    |

|    | 8.4.3EMI and ESD Protection      | 35 |

|    | 8.5 USB Compliance Testing       |    |

| 9  | EFT PCB LAYOUT DESIGN            |    |

|    | 9.1 PCB Layout Rule              |    |

|    | 9.2 EFT Crystal PCB Layout Guide |    |

| 10 |                                  |    |

### 1 Overview

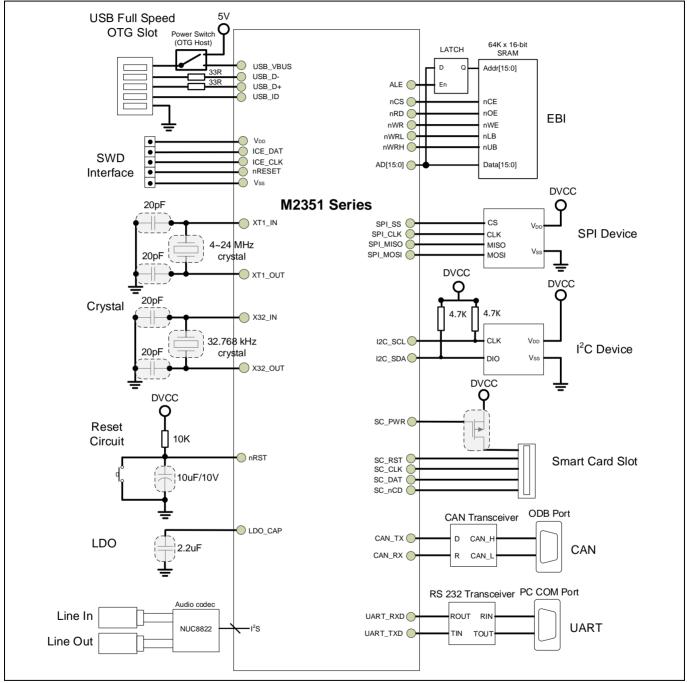

The M2351 hardware design guide is intended for hardware system designers who require a hardware implementation overview for a M2351 based system. The features include power operating modes, the external crystal, ADC and DAC reference source and USB reference circuit and EFT reference circuit. This design guide shows how to use the M2351 series and describes the minimum hardware resources required to develop a M2351 based system.

This design guide can be tailored to any other M2351 series with different package using the pins correspondingly given in the M2351 Datasheet.

## 2 M2351 Features

|                                           | <ul> <li>Arm<sup>®</sup> Cortex<sup>®</sup>-M23 processor, running up to 64 MHz</li> </ul>            |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                           | • 64MHz at 1.8V-3.6V; 48MHz at 1.7V-3.6V                                                              |

|                                           | Supports Arm <sup>®</sup> TrustZone <sup>®</sup> technology                                           |

|                                           | Built-in PMSAv8 Memory Protection Unit (MPU)                                                          |

|                                           | Built-in Security Attribution Unit (SAU)                                                              |

|                                           | Built-in Nested Vectored Interrupt Controller (NVIC)                                                  |

| Arm <sup>®</sup> Cortex <sup>®</sup> -M23 | Built-in Embedded Trace Macrocell (ETM)                                                               |

|                                           | 32-bit Single-cycle hardware multiplier and 32-bit 17-cycle hardware divider                          |

|                                           | 24-bit system tick timer                                                                              |

|                                           | Supports Programmble and maskable interrupt                                                           |

|                                           | Supports Low Power Sleep mode by WFI and WFE instructions                                             |

|                                           | Supports single cycle I/O access                                                                      |

|                                           | Configures SRAM's secure attribution block by block                                                   |

| Secure Configuration Unit                 | <ul> <li>Configures GPIO's secure attribution port by port</li> </ul>                                 |

| (SCU)                                     | <ul> <li>Monitor secure violation incident on the chip</li> </ul>                                     |

|                                           | 24-bit non-secure state monitor timer                                                                 |

|                                           |                                                                                                       |

| Brown-out Detector (BOD)                  | • Eight-level BOD with brown-out interrupt and reset option (3.0V/2.8V/2.6V/2.4V/2.2V/2.0V/1.8V/1.6V) |

| Low Voltage Reset (LVR)                   | LVR with 1.5V threshold voltage level                                                                 |

|                                           | Dual voltage regulator is available for DC-DC converter or LDO                                        |

|                                           | Supports 1.26v and 1.2v core voltage                                                                  |

|                                           | Supports Power-down mode                                                                              |

| Power Manager                             | Supports Standby Power-down mode                                                                      |

| Fower Manager                             | Supports low leakage Power-down mode                                                                  |

|                                           | <ul> <li>Supports ultra low leakage Power-down mode</li> </ul>                                        |

|                                           | Supports fast wake-up Power-down mode                                                                 |

|                                           | Supports deep Power-down mode                                                                         |

|                                           | 96-bit Unique ID (UID)                                                                                |

| Security                                  | 128-bit Unique Customer ID (UCID)                                                                     |

| •                                         | • One built-in temperature sensor with $1^{\circ}$ C resolution                                       |

| Memories                                  |                                                                                                       |

| Poet London                               | Factory pre-loaded 32 KB mask ROM for secure boot procedure                                           |

| Boot Loader                               | Root of Trust for Nuvoton Secure Microcontroller Platform                                             |

|                                           |                                                                                                       |

|                       | Dual bank 512 KB on-chip Application ROM (APROM) for Over The-Air (OTA) upgrade                                                               | ·-          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                       | 64 MHz maximum frequency, with performance at zero wait cyc continuous address read access                                                    | cle in      |

|                       | 4 KB on-chip Flash memory for user-defined loader (LDROM)                                                                                     |             |

|                       | 4 KB non-readbale Key Protection ROM (KPROM) for firmware<br>programming protection                                                           | I           |

|                       | 2 KB OTP for general-purpose control use, (2 KB data + 1 KB lo bit) easy for PLM (Product Lifecycle Management) implementat                   | ock<br>tion |

| Flash                 | Execute Only Memory (XOM) for software intelectual property protection                                                                        |             |

|                       | 32 KB Secure Boot ROM                                                                                                                         |             |

|                       | All on-chip Flash support 2 KB page erase                                                                                                     |             |

|                       | Fast Flash programming verification with CRC                                                                                                  |             |

|                       | On-chip Flash programming with In-Chip Programming (ICP), Ir<br>System Programming (ISP) and In-Application Programming (IA<br>capabilities   | n-<br>4P)   |

|                       | Configurable boot up sources including boot loader, user-define loader (LDROM) or Application ROM (APROM)                                     | ∋d          |

|                       | 2-wired ICP Flash updating through SWD interface                                                                                              |             |

|                       | 32-bit/64-bit and multi-word Flash programming function                                                                                       |             |

|                       | Up to 96 KB on-chip SRAM includes:                                                                                                            |             |

| <b>25</b> 4 4         | <ul> <li>32 KB SRAM located in bank 0 that supports hardware<br/>parity check; Exception (NMI) generated upon a parity c<br/>error</li> </ul> | check       |

| SRAM                  | - 64 KB SRAM located in bank 1                                                                                                                |             |

|                       | Byte-, half-word- and word-access                                                                                                             |             |

|                       | PDMA operation                                                                                                                                |             |

|                       | Supports CRC-CCITT, CRC-8, CRC-16 and CRC-32 polynomia                                                                                        |             |

|                       |                                                                                                                                               | 315         |

|                       | Programmable initial value and seed value<br>Programmable order reverse setting and one's complement set                                      | Itina       |

|                       | for input data and CRC checksum                                                                                                               | ung         |

| Cyclic Redundancy     | 8-bit, 16-bit, and 32-bit data width                                                                                                          |             |

| Calculation (CRC)     | 8-bit write mode with 1-AHB clock cycle operation                                                                                             |             |

|                       | 16-bit write mode with 2-AHB clock cycle operation                                                                                            |             |

|                       | 32-bit write mode with 4-AHB clock cycle operation                                                                                            |             |

|                       | Uses DMA to write data with performing CRC operation                                                                                          |             |

|                       | 16 independent and configurable channels for automatic data transfer between memories and peripherals                                         |             |

| Peripheral DMA (PDMA) | 8 channels of PDMA1 can be configured as secure or non-secu channels                                                                          | ıre         |

|                       | Supports time-out function when transfer time-out                                                                                             |             |

|                       | Basic and Scatter-Gather transfer modes                                                                                                       |             |

|                       | Each channel supports circular buffer management using Scatte                                                                                 | er-         |

Gather Transfer mode

- Stride function for rectangle image data movement

- Fixed-priority and Round-robin priorities modes

- Single and burst transfer types

- Byte-, half-word- and word tranfer unit with count up to 65536

- · Incremental or fixed source and destination address

| Clocks                |                                                                                                                                                                                                             |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       | <ul> <li>4~24 MHz High-speed external crystal oscillator (HXT) for precise<br/>timing operation</li> </ul>                                                                                                  |  |

| External Clock Source | <ul> <li>32.768 kHz Low-speed external crystal oscillator (LXT) for RTC function and low-power system operation</li> </ul>                                                                                  |  |

|                       | <ul> <li>Supports clock failure detection for external crystal oscillators and<br/>exception generation (NMI)</li> </ul>                                                                                    |  |

|                       | 12 MHz High-speed Internal RC oscillator (HIRC) trimmed to 0.25% accuracy that can optionally be used as a system clock                                                                                     |  |

|                       | <ul> <li>48 MHz High-speed Internal RC oscillator (HIRC48) trimmed to<br/>0.25% accuracy that can optionally be used as a system clock</li> </ul>                                                           |  |

| Internal Clock Source | <ul> <li>10 kHz Low-speed Internal RC oscillator (LIRC) for watchdog timer<br/>and wakeup operation</li> </ul>                                                                                              |  |

|                       | 32 kHz Low-speed Internal RC oscillator (LIRC32) for RTC function                                                                                                                                           |  |

|                       | <ul> <li>Up to 144 MHz on-chip PLL, sourced from HIRC or HXT, allowing<br/>for CPU operation up to the maximum CPU frequency without the<br/>need for a high-frequency crystal</li> </ul>                   |  |

|                       | Real-Time Clock with a separate power domain                                                                                                                                                                |  |

|                       | <ul> <li>The RTC clock source includes Low-speed external crystal<br/>oscillator (LXT) and 32kHz Low-speed Internal RC oscillator<br/>(LIRC32) and 10kHz Low-speed Internal RC oscillator (LIRC)</li> </ul> |  |

|                       | <ul> <li>The RTC block includes 80 bytes of battery-powered backup<br/>registers, which can be cleared by tamper pins</li> </ul>                                                                            |  |

|                       | Supports 6 static and dynamic tamper pins                                                                                                                                                                   |  |

| Real-Time Clock (RTC) | <ul> <li>Able to wake up CPU from any reduced power mode</li> </ul>                                                                                                                                         |  |

|                       | Supports Alarm registers (second, minute, hour, day, month, year)                                                                                                                                           |  |

|                       | <ul> <li>Supports RTC Time Tick and Alarm Match interrupt</li> </ul>                                                                                                                                        |  |

|                       | Automatic leap year recognition                                                                                                                                                                             |  |

|                       | <ul> <li>Supports 1 Hz clock output for calibration</li> </ul>                                                                                                                                              |  |

|                       | <ul> <li>Frequency of RTC clock source compensate by RTC_FREQADJ<br/>register</li> </ul>                                                                                                                    |  |

| Timers                |                                                                                                                                                                                                             |  |

|                       | TIMER                                                                                                                                                                                                       |  |

| 32-bit Timer          | <ul> <li>Four sets of 32-bit timers with 24-bit up counter and one 8-bit pre-<br/>scale counter from independent clock source</li> </ul>                                                                    |  |

|                       | <ul> <li>One-shot, Periodic, Toggle and Continuous Counting operation<br/>modes</li> </ul>                                                                                                                  |  |

|                     | <ul> <li>Supports event counting function to count the event from external<br/>pins</li> </ul>                                                                                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | <ul> <li>Supports external capture pin for interval measurement and resetting 24-bit up counter</li> </ul>                                                                            |

|                     | <ul> <li>Supports chip wake-up function, if a timer interrupt signal is generated</li> </ul>                                                                                          |

|                     | PWM                                                                                                                                                                                   |

|                     | <ul> <li>Eight 16-bit PWM counters with 12-bit clock prescale with up to 64<br/>MHz</li> </ul>                                                                                        |

|                     | Supports 12-bit deadband (dead time)                                                                                                                                                  |

|                     | Up, down or up-down PWM counter type                                                                                                                                                  |

|                     | Supports brake function                                                                                                                                                               |

|                     | Supports mask function and tri-state output for each PWM channel                                                                                                                      |

|                     | Twelve 16-bit counters with 12-bit clock prescale for twelve 64 MHz<br>PWM output channels                                                                                            |

|                     | <ul> <li>Up to 12 independent input capture channels with 16-bit resolution<br/>counter</li> </ul>                                                                                    |

|                     | Supports dead time with maximum divided 12-bit prescale                                                                                                                               |

|                     | Up, down or up-down PWM counter type                                                                                                                                                  |

| Enhanced PWM (EPWM) | <ul> <li>Supports complementary mode for 3 complementary paired PWM<br/>output channels</li> </ul>                                                                                    |

|                     | Synchronous function for phase control                                                                                                                                                |

|                     | Counter synchronous start function                                                                                                                                                    |

|                     | Brake function with auto recovery mechanism                                                                                                                                           |

|                     | <ul> <li>Mask function and tri-state output for each PWM channel</li> </ul>                                                                                                           |

|                     | Able to trigger EADC or DAC to start conversion                                                                                                                                       |

|                     | <ul> <li>Two 16-bit counters with 12-bit clock prescale for twelve 64 MHz<br/>PWM output channels</li> </ul>                                                                          |

|                     | <ul> <li>Up to 6 independent input capture channels with 16-bit resolution<br/>counter</li> </ul>                                                                                     |

| Basic PWM (BPWM)    | Up, down or up-down PWM counter type                                                                                                                                                  |

|                     | Counter synchronous start function                                                                                                                                                    |

|                     | <ul> <li>Mask function and tri-state output for each PWM channel</li> </ul>                                                                                                           |

|                     | Able to trigger EADC to start conversion                                                                                                                                              |

|                     | 18-bit free running up counter for WDT time-out interval                                                                                                                              |

|                     | <ul> <li>Supports multiple clock sources from LIRC (default selection),<br/>HCLK/2048 and LXT with 8 selectable time-out period</li> </ul>                                            |

| Watabdag            | Able to wake up system from Power-down or Idle mode                                                                                                                                   |

| Watchdog            | Time-out event to trigger interrupt or reset system                                                                                                                                   |

|                     |                                                                                                                                                                                       |

|                     | <ul> <li>Supports four WDT reset delay periods, including 1026, 130, 18 or 3<br/>WDT_CLK reset delay period</li> </ul>                                                                |

|                     | <ul> <li>Supports four WDT reset delay periods, including 1026, 130, 18 or 3 WDT_CLK reset delay period</li> <li>Configured to force WDT enabled on chip power-on or reset</li> </ul> |

|                             | down counter with 11-bit prescale                                                                                                                                         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | Suspended in Idle/Power-down mode                                                                                                                                         |

| Analog Interfaces           |                                                                                                                                                                           |

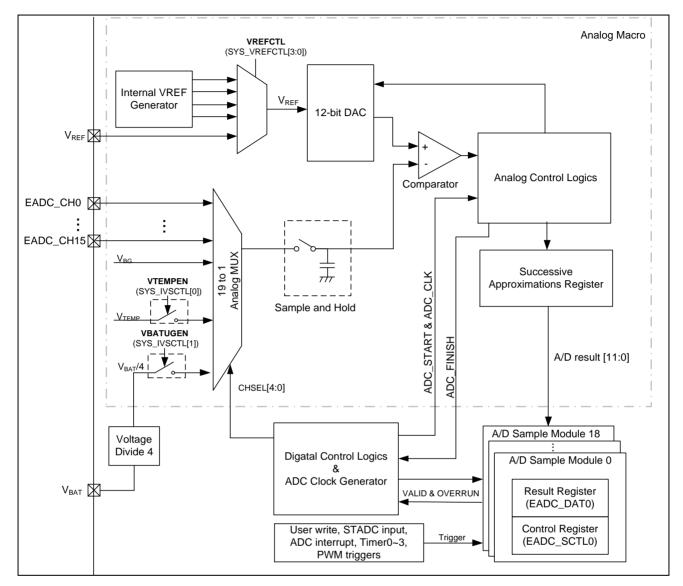

|                             | <ul> <li>One 12-bit, 16-ch 3.76 MSPS SAR EADC with up to 16 single-<br/>ended input channels or 8 differential input pairs; 10-bit accuracy is<br/>guaranteed.</li> </ul> |

|                             | <ul> <li>Three internal channels for V<sub>BAT</sub>, band-gap V<sub>BG</sub> input and<br/>Temperature sensor input.</li> </ul>                                          |

|                             | • Supports external VREF pin or internal reference voltage VREF: 1.6V, 2.0V, 2.5V, and 3.0V.                                                                              |

| Enhanced Analog-to-Digital  | • Two power saving modes: Power-down mode and Standby mode.                                                                                                               |

| Converter (EADC)            | Supports calibration capability.                                                                                                                                          |

|                             | <ul> <li>Analog-to-Digital conversion can be triggered by software enable,<br/>external pin, Timer 0~3 overflow pulse trigger or EPWM trigger.</li> </ul>                 |

|                             | Configurable EADC sampling time.                                                                                                                                          |

|                             | Up to 19 sample modules.                                                                                                                                                  |

|                             | <ul> <li>Double data buffers for sample module 0~3.</li> </ul>                                                                                                            |

|                             | PDMA operation.                                                                                                                                                           |

|                             | <ul> <li>Two 12-bit, 1 MSPS voltage type DAC with 8-bit mode and 8µs rail-<br/>to-rail settle time</li> </ul>                                                             |

| Digital-to-Analog Converter | <ul> <li>Maximum output voltage AV<sub>DD</sub> -0.2V in buffer mode.</li> </ul>                                                                                          |

| (DAC)                       | <ul> <li>Digital-to-Analog conversion triggered by Timer0~3, EPWM0,<br/>EPWM1, external trigger pin to start DAC conversion or software.</li> </ul>                       |

|                             | • Supports group mode for synchronized data update of two DACs.                                                                                                           |

|                             | PDMA operation.                                                                                                                                                           |

|                             | Two rail-to-rail Analog Comparators.                                                                                                                                      |

|                             | <ul> <li>Supports four multiplexed I/O pins at positive input.</li> </ul>                                                                                                 |

|                             | <ul> <li>Supports I/O pins, band-gap, DAC output, and 16-level Voltage<br/>divider from AV<sub>DD</sub> or V<sub>REF</sub> at negative input.</li> </ul>                  |

| Analog Comparator           | Supports four programmable propagation speeds for power saving.                                                                                                           |

| (ACMP)                      | <ul> <li>Supports wake up from Power-down by interrput.</li> </ul>                                                                                                        |

|                             | <ul> <li>Supports triggers for brake events and cycle-by-cycle control for<br/>PWM.</li> </ul>                                                                            |

|                             | Supports window compare mode and window latch mode.                                                                                                                       |

|                             | <ul> <li>Supports programmable hysteresis window: 0mV, 10mV, 20mV and<br/>30mV.</li> </ul>                                                                                |

| Communication Interfaces    |                                                                                                                                                                           |

|                             | Six sets of UARTs with up to 10.66 MHz baud rate                                                                                                                          |

| Low-power UART              | <ul> <li>Auto-Baud Rate measurement and baud rate compensation<br/>function</li> </ul>                                                                                    |

| Low-power OAKT              | <ul> <li>Supports low power UART (LPUART): baud rate clock from<br/>LXT(32.768 KHz) with 9600bps in Power-down mode even system<br/>clock is stopped</li> </ul>           |

- 16-byte FIFOs with programmable level trigger

- Auto flow control (nCTS and nRTS)

- Supports IrDA (SIR) function

- Supports LIN function on UART0 and UART1

- Supports RS-485 9-bit mode and direction control

- Supports nCTS, incoming data, Received Data FIFO reached threshold and RS-485 Address Match (AAD mode) wake-up function in idle mode

- Supports hardware or software enables to program nRTS pin to control RS-485 transmission direction

- Supports wake-up function

- 8-bit receiver FIFO time-out detection function

- Supports break error, frame error, parity error and receive/transmit FIFO overflow detection function

- PDMA operation

- Three sets of ISO-7816-3 which are compliant with ISO-7816-3 T=0, T=1

- Supports full duplex UART function

- 4-byte FIFOs with programmable level trigger

- Programmable guard time selection (11 ETU ~ 266 ETU)

- One 24-bit and two 8 bit time-out counters for Answer to Request (ATR) and waiting times processing

- Auto inverse convention function

- Stop clock level and clock stop (clock keep) function

- Transmitter and receiver error retry function

- Supports hardware activation, deactivation and warm reset sequence process

- Supports hardware auto deactivation sequence after card removal

- Three sets of I<sup>2</sup>C devices with Master/Slave mode

- Supports Standard mode (100 kbps), Fast mode (400 kbps) and Fast mode plus (1 Mbps)

Supports multiple address recognition (four slave address with

- Supports 10 bits mode

- Programmable clocks allowing for versatile rate control

- I<sup>2</sup>C

**Smart Card Interface**

- mask option)

Supports SM (Sytem Management) Bus and PM (Power Management) Bus

- Supports multi-address power-down wake-up function

- PDMA operation

- One set of SPI Quad controller with Master/Slave mode, up to 64 MHz at 2.7V~3.6V stsyem voltage.

Supports Dual and Quad I/O Transfer mode

- Supports one/two data channel half-duplex transfer

|                          | Supports receive-only mode                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | <ul> <li>Configurable bit length of a transfer word from 8 to 32-bit</li> </ul>                                                                         |

|                          | Provides separate 8-level depth transmit and receive FIFO buffers                                                                                       |

|                          | MSB first or LSB first transfer sequence                                                                                                                |

|                          | The byte reorder function                                                                                                                               |

|                          | Supports Byte or Word Suspend mode                                                                                                                      |

|                          | Supports 3-wired, no slave select signal, bi-direction interface                                                                                        |

|                          | <ul> <li>PDMA operation.</li> </ul>                                                                                                                     |

|                          | •                                                                                                                                                       |

|                          | <ul> <li>Up to four sets of SPI/I<sup>2</sup>S controllers with Master/Slave mode</li> </ul>                                                            |

|                          | <ul> <li>SPI can communicate at up to 64 Mbit/s</li> </ul>                                                                                              |

|                          | <ul> <li>SPI/I<sup>2</sup>S provides separate 4-level of 32-bit (or 8-level of 16-bit)<br/>transmit and receive FIFO buffers</li> </ul>                 |

|                          | SPI                                                                                                                                                     |

|                          | Configurable bit length of a transfer word from 8 to 32-bit                                                                                             |

|                          | MSB first or LSB first transfer sequence                                                                                                                |

|                          | Byte reorder function                                                                                                                                   |

| SPI/I <sup>2</sup> S     | Supports Byte or Word Suspend mode                                                                                                                      |

|                          | Supports one data channel half-duplex transfer                                                                                                          |

|                          |                                                                                                                                                         |

|                          | Supports receive-only mode                                                                                                                              |

|                          | I <sup>2</sup> S                                                                                                                                        |

|                          | <ul> <li>Supports mono and stereo audio data with 8-, 16-, 24- and 32-bit<br/>audio data sizes</li> </ul>                                               |

|                          | <ul> <li>Supports PCM mode A, PCM mode B, I2S and MSB justified data<br/>format</li> </ul>                                                              |

|                          | PDMA operation                                                                                                                                          |

|                          | One set of I <sup>2</sup> S interface with Master/Slave mode                                                                                            |

|                          | <ul> <li>I<sup>2</sup>S audio sampling frequencies up to 192 kHz are supported</li> </ul>                                                               |

|                          | <ul> <li>Supports mono and stereo audio data with 8-, 16-, 24- and 32-bit<br/>word sizes</li> </ul>                                                     |

|                          | <ul> <li>Two 16-level FIFO data buffers, one for transmitting and the other<br/>for receiving</li> </ul>                                                |

| I <sup>2</sup> S         | <ul> <li>Supports I<sup>2</sup>S protocols: Philips standard, MSB-justified, and LSB-<br/>justified data format</li> </ul>                              |

|                          | <ul> <li>Supports PCM protocols: PCM standard, MSB-justified, and LSB-<br/>justified data format</li> </ul>                                             |

|                          | <ul> <li>PCM protocol supports TDM multi-channel transmission in one<br/>audio sample; the number of data channel can be set as 2, 4, 6 or 8</li> </ul> |

|                          | <ul> <li>PDMA operation</li> </ul>                                                                                                                      |

|                          | Two sets of USCI, configured as UART, SPI or I <sup>2</sup> C function                                                                                  |

| Universal Serial Control | Supports single byte TX and RX buffer mode                                                                                                              |

| Interface (USCI)         | • UART                                                                                                                                                  |

|                          | <ul> <li>Supports one transmit buffer and two receive buffers for data</li> </ul>                                                                       |

|                          | Supports one transmit build and two receive builds for uala                                                                                             |

| payl | oad |

|------|-----|

|------|-----|

- Supports hardware auto flow control function and programmable flow control trigger level

- 9-bit Data Transfer

- Baud rate detection by built-in capture event of baud rate generator

- Supports wake-up function

- PDMA operation

- SPI

- · Supports Master or Slave mode operation

- Supports one transmit buffer and two receive buffer for data payload

- Configurable bit length of a transfer word from 4 to 16-bit

- Supports MSB first or LSB first transfer sequence

- Supports Word Suspend function

- Supports 3-wire, no slave select signal, bi-direction interface

- Supports wake-up function by slave select signal in slave mode

- · Supports one data channel half-duplex transfer

- PDMA operation

- I<sup>2</sup>C

- Supports master and slave device capability

- · Supports one transmit buffer and two receive buffer for data payload

- Communication in standard mode (100 kbps), fast mode (up to 400 kbps), and Fast mode plus (1 Mbps)

- Supports 10-bit mode

- · Supports 10-bit bus time out capability

- Supports bus monitor mode

- Supports power-down wake-up by data toggle or address match

- Supports multiple address recognition

- Supports device address flag

- Programmable setup/hold time

- Two sets of CAN 2.0B controllers

Each supports 32 Message Objects; each Message Object has its own identifier mask

Programmable FIFO mode (concatenation of Message Object)

Disabled Automatic Re-transmission mode for Time Triggered CAN applications

Supports power-down wake-up function

One set of Secure Digital Host Controller, compliant with SD Memory Card Specification Version 2.0

Supports 50 MHz to achieve 200 Mbps at 3.3V operation

Supports 50 MHz to achieve 200 Mbps at 3.3V operation

- Supports dedicated DMA master with Scatter-Gather function to accelerate the data transfer between system memory and SD/SDHC/SDIO card

|                                       | <ul> <li>Supports up to three memory banks with individual adjustment of timing parameter</li> </ul>                                              |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | <ul> <li>Each bank supports dedicated external chip select pin with polarity<br/>control and up to 1 MB addressing space</li> </ul>               |

|                                       | 8-/16-bit data width                                                                                                                              |

|                                       | Supports byte write in 16-bit data width mode                                                                                                     |

| External Bus Interface<br>(EBI)       | <ul> <li>Supports variable external bus base clock (MCLK) which based on HCLK</li> </ul>                                                          |

| ()                                    | <ul> <li>Configurable idle cycle for different access condition: Idle of Write<br/>command finish (W2X) and Idle of Read-to-Read (R2R)</li> </ul> |

|                                       | Supports Address/Data multiplexed mode                                                                                                            |

|                                       | <ul> <li>Supports address bus and data bus separate mode</li> </ul>                                                                               |

|                                       | Supports LCD interface i80 mode                                                                                                                   |

|                                       | PDMA operation                                                                                                                                    |

|                                       | <ul> <li>Supports four I/O modes: Quasi bi-direction, Push-Pull output,<br/>Open-Drain output and Input only with high impendence mode</li> </ul> |

|                                       | Selectable TTL/Schmitt trigger input                                                                                                              |

|                                       | <ul> <li>Configured as interrupt source with edge/level trigger setting</li> </ul>                                                                |

| GPIO                                  | <ul> <li>Supports independent pull-up/pull-down control</li> </ul>                                                                                |

| GPIO                                  | <ul> <li>Supports high driver and high sink current I/O</li> </ul>                                                                                |

|                                       | Supports software selectable slew rate control                                                                                                    |

|                                       | <ul> <li>Supports 5V-tolerance function except analog I/O. (Except PA.8 ~ 15; PB.0 ~ 15; PD.10 ~ 12; PF.2 ~ 5; nReset.)</li> </ul>                |

|                                       | <ul> <li>Improve access efficiency by using single cycle IO bus</li> </ul>                                                                        |

| Control Interfaces                    |                                                                                                                                                   |

|                                       | <ul> <li>Two QEI phase inputs (QEI_A, QEI_B) and one Index input<br/>(QEI_INDEX)</li> </ul>                                                       |

| Quadrature Encoder<br>Interface (QEI) | <ul> <li>Supports 2/4 times free-counting mode and 2/4 compare-counting mode</li> </ul>                                                           |

|                                       | Supports encoder pulse width measurement mode with ECAP                                                                                           |

|                                       | Input Capture Timer/Counter                                                                                                                       |

|                                       | Supports three input channels with independent capture counter hold register                                                                      |

| Enhanced Capture (ECAP)               | <ul> <li>24-bit Input Capture up-counting timer/counter supports captured<br/>events reset and/or reload capture counter</li> </ul>               |

|                                       | <ul> <li>Supports rising edge, falling edge and both edge detector options<br/>with noise filter in front of input ports</li> </ul>               |

|                                       | Supports compare-match function                                                                                                                   |

| Advanced Connectivity                 |                                                                                                                                                   |

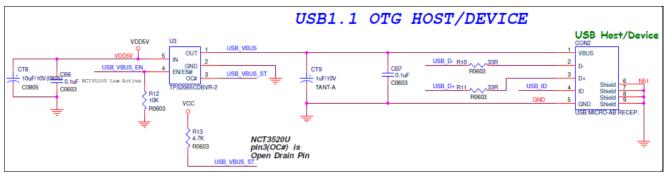

| USB 2.0 Full Speed with               | USB 2.0 Full Speed OTG (On-The-Go)                                                                                                                |

| on-chip transceiver                   | On-chip USB 2.0 full speed OTG transceiver                                                                                                        |

|                          | Compliant with USB OTG Supplement 2.0                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                          | <ul> <li>Configurable as host-only, device-only or ID-dependent</li> </ul>                                                 |

|                          | USB 1.1 Host Controller                                                                                                    |

|                          | <ul> <li>Compliant with USB Revision 1.1 Specification</li> </ul>                                                          |

|                          | Compatible with OHCI (Open Host Controller Interface) Revision 1.0                                                         |

|                          | <ul> <li>Supports full-speed (12Mbps) and low-speed (1.5Mbps) USB devices</li> </ul>                                       |

|                          | Supports Control, Bulk, Interrupt, Isochronous and Split transfers                                                         |

|                          | <ul> <li>Integrated a port routing logic to route full/low speed device to OHC controller</li> </ul>                       |

|                          | Supports an integrated Root Hub                                                                                            |

|                          | Supports port power control and port over current detection                                                                |

|                          | Built-in DMA                                                                                                               |

|                          | USB 2.0 Full Speed Device Controller                                                                                       |

|                          | Compliant with USB Revision 2.0 Specification                                                                              |

|                          | Supports crystal-less                                                                                                      |

|                          | Supports suspend function when no bus activity existing for 3 ms                                                           |

|                          | <ul> <li>12 configurable endpoints for configurable Isochronous, Bulk,<br/>Interrupt and Control transfer types</li> </ul> |

|                          | <ul> <li>1024 bytes configurable RAM for endpoint buffer</li> </ul>                                                        |

|                          | Remote wake-up capability                                                                                                  |

| Cryptography Accelerator |                                                                                                                            |

|                          | Hardware ECC accelerator                                                                                                   |

|                          | <ul> <li>Supports both prime field GF(p) and binary field GF(2m)</li> </ul>                                                |

|                          | • Supports NIST P-192, P-224, P-256, P-384 and P-521 curve sizes                                                           |

| Elliptic Curve           | • Supports NIST B-163, B-233, B-283, B-409 and B-571 curve sizes                                                           |

| Cryptography (ECC)       | • Supports NIST K-163, K-233, K-283, K-409 and K-571 curve sizes                                                           |

|                          | <ul> <li>Supports point multiplication, addition and doubling operations in<br/>GF(p) and GF(2m)</li> </ul>                |

|                          | <ul> <li>Supports modulus division, multiplication, addition and subtraction operations in GF(p)</li> </ul>                |

|                          | Hardware AES accelerator                                                                                                   |

| Advanced Encryption      | • Supports 128-bit, 192-bit and 256-bit key length and key expander, and is compliant with FIPS 197                        |

| Standard (AES)           | <ul> <li>Supports ECB, CBC, CFB, OFB, CTR, CBC-CS1, CBC-CS2 and<br/>CBC-CS3 block cipher modes</li> </ul>                  |

|                          | <ul> <li>Compliant with NIST SP800-38A and addendum</li> </ul>                                                             |

|                          | Hardware DES accelerator                                                                                                   |

| Data Encryption Standard | <ul> <li>Supports ECB, CBC, CFB, OFB, and CTR block cipher mode</li> </ul>                                                 |

| (DES)                    | <ul> <li>Compliant with FIPS 46-3</li> </ul>                                                                               |

| Triple Data Encryption   | Hardware Triple DES accelerator                                                                                            |

| . ,                      |                                                                                                                            |

| Standard (3DES)                          | • | Supports two or three different keys in each round<br>Supports ECB, CBC, CFB, OFB, and CTR block cipher mode<br>Implemented based on X9.52 standard and compliant with FIPS SP<br>800-67 |  |

|------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Secure Hash Algorithm<br>(SHA)           | • | Hardware SHA accelerator<br>Supports SHA-160, SHA-224, SHA-256 and SHA-384<br>Compliant with FIPS 180/180-2                                                                              |  |

| Pseudo Random Number<br>Generator (PRNG) | • | Supports 64-bit, 128-bit, 192-bit and 256-bit random number generation                                                                                                                   |  |

| True Randon Number<br>Generator (TRNG)   | • | Up to 800 random bits per second                                                                                                                                                         |  |

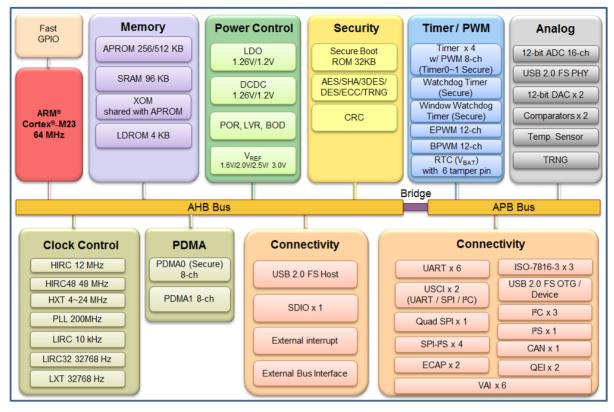

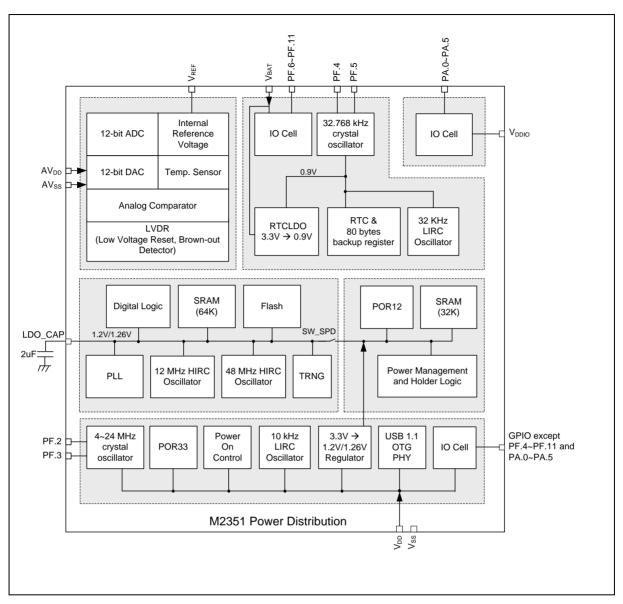

## 3 Block Diagram

Figure 3-1 NuMicro® M2351 Block Diagram

### 4 **Power Supplies**

This section describes design considerations related to the M2351 series power supply scheme and power operating modes.

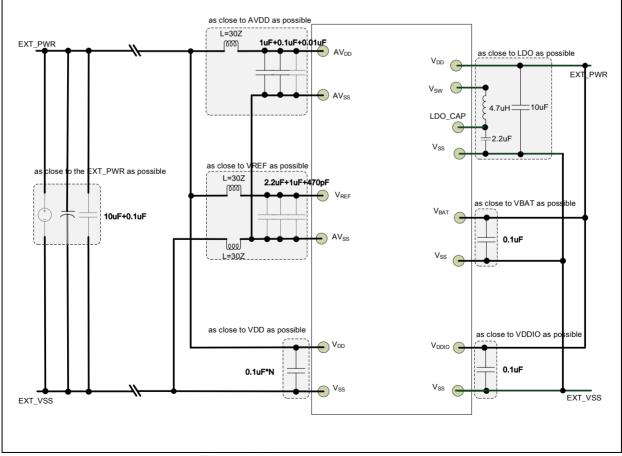

#### 4.1 **Power Supply Scheme**

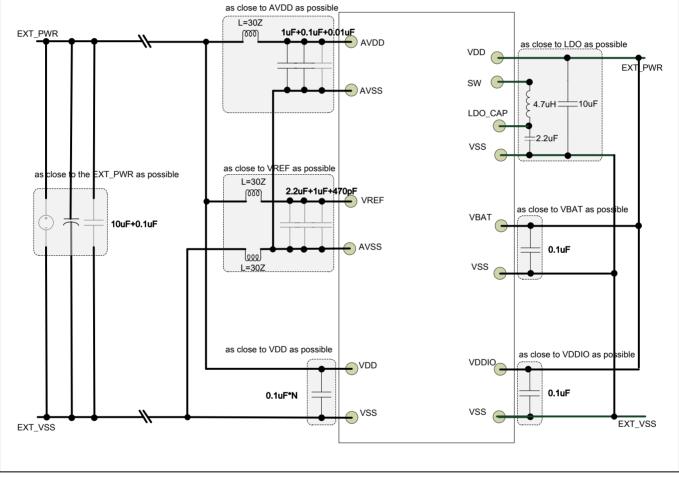

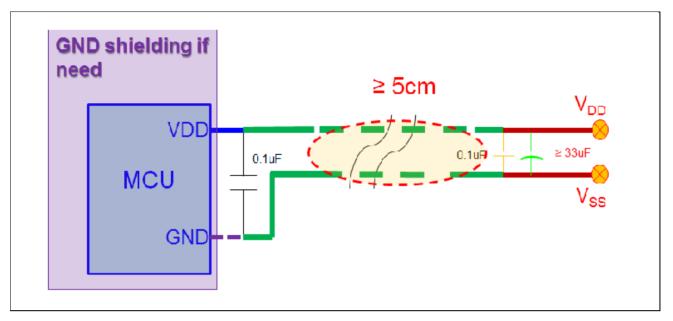

The M2351 series should be powered by a stabilized power supply  $V_{DD}$ . Some precautions need to be taken when using the power.

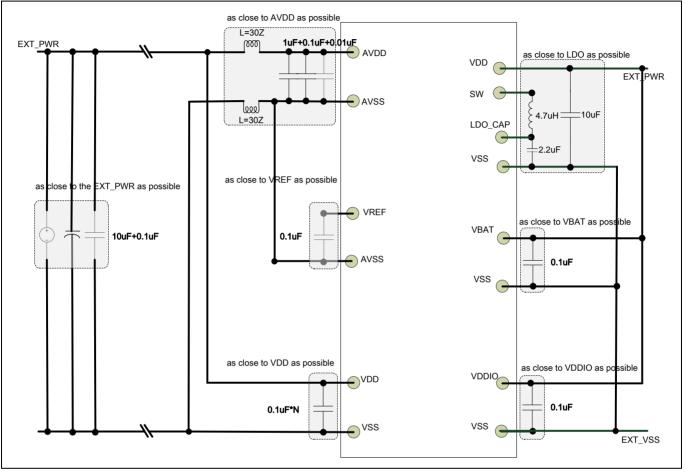

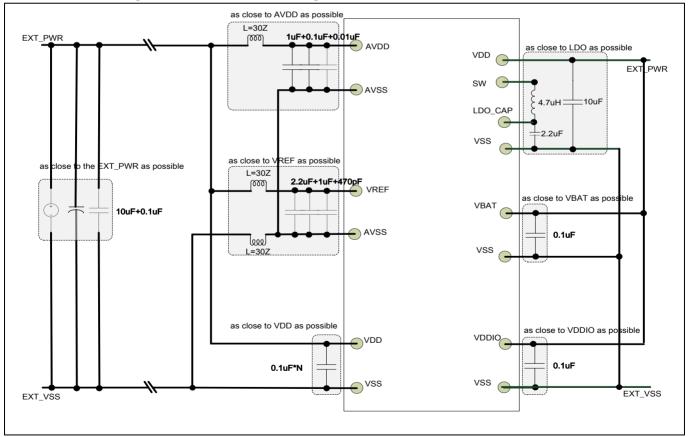

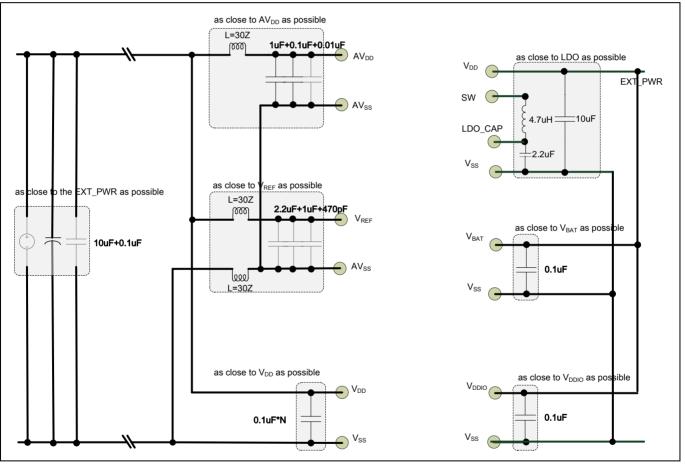

- The V<sub>DD</sub> pins must be connected to V<sub>DD</sub> (1.70V~3.6V) with external decoupling capacitors (a 0.1uF capacitor for each V<sub>DD</sub> pin and a 4.7uF capacitor for the whole chip).

- The AV<sub>DD</sub> pin must be connected to external decoupling capacitors (1uF+0.1uF+10nF).

- LDO\_CAP pin must be connected to external 2.2uF decoupling capacitor.

- The V<sub>REF</sub> pin can be connected to the AV<sub>DD</sub> external power supply via ferrite bead. If a separate, external reference voltage is applied on V<sub>REF</sub>, 2.2uF, 1nF and 470pF capacitors must be connected on this pin. In all cases, V<sub>REF</sub> must be kept between 0V and AV<sub>DD</sub>.

To keep the analog power stable, additional precautions need to be taken to filter analog noise. Refer to Figure 4-1 for board designing:

Figure 4-1 Power Supply Scheme

#### Note:

- 1. N is the number of  $V_{DD}$  and  $V_{SS}$  input pairs.

- 2. It is recommended that a 4.7 $\mu$ F or higher capacitor and a 0.1 $\mu$ F bypass capacitor be connected between V<sub>DD</sub> and the closest V<sub>SS</sub> pin of the device.

- 3. For ensuring power stability, a 2.2 $\mu$ F or higher capacitor must be connected between the LDO\_CAP pin and the closest V<sub>SS</sub> pin. Also, adding a 0.1 $\mu$ F bypass capacitor helps to suppress output noise.

- 4. Caution:

- If the ADC/DAC is used, the  $V_{DD}$  range is limited to 1.8 V to 3.6 V.

- If the ADC/DAC is not used, the  $V_{DD}$  range is 1.70 V to 3.6 V.

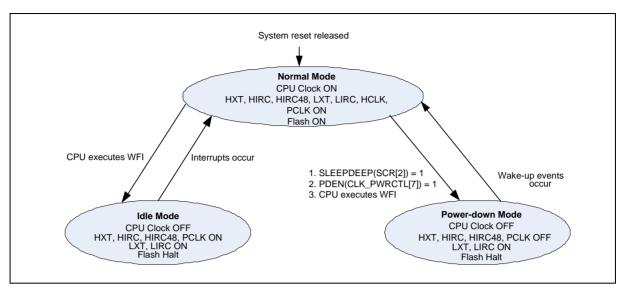

### 4.2 Power Modes and Wake-up Sources

The NuMicro<sup>®</sup> M2351 series has power manager unit to support several operating modes for saving power. Table 4-1 lists all power modes in the NuMicro<sup>®</sup> M2351 series.

| Mode                                            | CPU Operating Maximum<br>Speed<br>(MHz) | LDO_CAP<br>(V) | Clock Disable                                                                                                                                                  |

|-------------------------------------------------|-----------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal mode                                     | 48MHz                                   | 1.20           | All clocks are disabled by control register.<br>CLK_AHBCLK, CLK_APBCLK0 and<br>CLK_APBCLK1.                                                                    |

| Turbo mode                                      | 64MHz                                   | 1.26           | All clocks are disabled by control register.<br>CLK_AHBCLK, CLK_APBCLK0 and<br>CLK_APBCLK1.                                                                    |

| Idle mode                                       | CPU enter Sleep mode                    | keep           | Only CPU clock is disabled.                                                                                                                                    |

| Power-down mode (PD)                            | CPU enters Deep Sleep mode              | keep           | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Fast Wake-up Power-down<br>mode (FWPD)          | CPU enters Deep Sleep mode              | keep           | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Low leakage Power-down<br>mode<br>(LLPD)        | CPU enters Deep Sleep mode              | 0.9            | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Ultra Low leakage Power-down<br>mode<br>(ULLPD) | CPU enters Deep Sleep mode              | 0.8            | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Standby Power-down mode<br>(SPD)                | Power off                               | Floating       | Only LIRC/LXT still enable for RTC function and wake-up timer usage.                                                                                           |

| Deep Power-down mode<br>(DPD)                   | Power off                               | Floating       | Only LIRC/LXT still enable for RTC function and wake-up timer usage.                                                                                           |

Table 4-1 Power Mode Table

Each power mode has different entry setting and leaving condition. Table 4-2 shows the entry setting for each power mode. When chip power-on, chip is running in normal mode. User can enter each mode by setting SLEEPDEEP (SCR[2]), PDEN (CLK\_PWRCT[7]) and PDMSEL (CLK\_PMUCTL[2:0]) and execute WFI instruction.

| Register/Instruction<br>Mode         | - | PDEN<br>(CLK_PWRCTL[7]) | PDMSEL<br>(CLK_PMUCTL[2:0]) | CPU Run WFI Instruction |

|--------------------------------------|---|-------------------------|-----------------------------|-------------------------|

| Normal mode                          | 0 | 0                       | 0                           | NO                      |

| Idle mode                            | 0 | 0                       | 0                           | YES                     |

| Power-down mode                      | 1 | 1                       | 0                           | YES                     |

| Low leakage Power-down mode          | 1 | 1                       | 1                           | YES                     |

| Ultra Low leakage Power-down<br>mode | 1 | 1                       | 3                           | YES                     |

| Fast Wake-up Power-down mode         | 1 | 1                       | 2                           | YES                     |

| Standby Power-down mode              | 1 | 1                       | 4                           | YES                     |

| Deep Power-down mode                 | 1 | 1                       | 6                           | YES                     |

Table 4-2 Power Mode Entry Setting Table

There are several wake-up sources in Idle mode and Power-down mode. Table 4-3 lists the available clocks for each power mode.

| Power Mode       | Normal Mode                                           | Idle Mode                     | Power-Down Mode                                                                                                                               |

|------------------|-------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Definition       | CPU is in active state                                | CPU is in sleep state         | CPU is in sleep state and all clocks<br>stop except LXT and LIRC. SRAM<br>content be retained by setting<br>SYS_SRAMPCTL and<br>SYS_SRAMPPCT. |

| Entry Condition  | Chip is in normal mode after<br>system reset released | CPU executes WFI instruction. | CPU sets sleep mode enable and<br>Power-down enable and executes<br>WFI instruction.                                                          |

| Wake-up Sources  | N/A                                                   | All interrupts                | EINT, GPIO, UART, USBD, USBH,<br>OTG, CAN, BOD, WDT, SDH,<br>Timer, I²C, USCI, RTC and ACMP.                                                  |

| Available Clocks | All                                                   | All except CPU clock          | LXT and LIRC                                                                                                                                  |

| After Wake-up    | N/A                                                   | CPU back to normal mode       | CPU back to normal mode                                                                                                                       |

Table 4-3 Power Mode Difference Table

Figure 4-2 Power Mode State Machine

- 1. LXT ON or OFF depends on software setting in normal mode.

- 2. LIRC ON or OFF depends on software setting in normal mode.

- 3. If TIMER clock source is selected as LIRC/LXT and LIRC/LXT is on.

- 4. If WDT clock source is selected as LIRC and LIRC is on.

- 5. If RTC clock source is selected as LXT and LXT is on.

- 6. If UART clock source is selected as LXT and LXT is on.

|           | Normal Mode | Idle Mode | Power-Down Mode<br>(PD/FWPD/LLPD/ULLPD) | Power-Down Mode<br>(SPD/DPD) |

|-----------|-------------|-----------|-----------------------------------------|------------------------------|

| НХТ       | ON          | ON        | Halt                                    | Halt                         |

| HIRC      | ON          | ON        | Halt                                    | Halt                         |

| HIRC48    | ON          | ON        | Halt                                    | Halt                         |

| LXT       | ON          | ON        | ON/OFF <sup>1</sup>                     | ON/OFF <sup>1</sup>          |

| LIRC      | ON          | ON        | ON/OFF <sup>2</sup>                     | ON/OFF <sup>2</sup>          |

| PLL       | ON          | ON        | Halt                                    | Halt                         |

| CPU       | ON          | Halt      | Halt                                    | Halt                         |

| HCLK/PCLK | ON          | ON        | Halt                                    | Halt                         |

| FLASH     | ON          | ON        | Halt                                    | Halt                         |

| TIMER     | ON          | ON        | ON/OFF <sup>3</sup>                     | Halt                         |

| WDT       | ON          | ON        | ON/OFF <sup>4</sup>                     | Halt                         |

| RTC       | ON          | ON        | ON/OFF⁵                                 | ON/OFF⁵                      |

| UART      | ON          | ON        | ON/OFF <sup>6</sup>                     | Halt                         |

| Others    | ON          | ON        | Halt                                    | Halt                         |

Table 4-4 Clocks in Power Modes

The wake-up sources in Power-down mode:

EINT, GPIO, UART, USBD, USBH, OTG, CAN, BOD, ACMP, WDT, SDH, Timer, I<sup>2</sup>C, USCI, , , RTC.

After chip enters Power-down, the following wake-up sources can wake chip up to normal mode. Table 4-5 lists the condition about how to enter Power-down mode again for each peripheral.

\*User needs to wait this condition before setting PDEN(CLK\_PWRCTL[7]) and execute WFI to enter Power-down mode.

|                                |                                      | Power-down Mode             |     |     |                                                                                               |

|--------------------------------|--------------------------------------|-----------------------------|-----|-----|-----------------------------------------------------------------------------------------------|

| Wake-up<br>Source              | Wake-up Condition                    | PD<br>LLPD<br>ULLPD<br>FWPD | SPD | DPD | System Can Enter Power-down Mode Again<br>Condition*                                          |

| BOD                            | Brown-out Detector Reset / Interrupt | V                           | -   | -   | After software writes 1 to clear BODIF<br>(SYS_BODCTL[4]).                                    |

| вор                            | Brown-out Detector Reset             | -                           | V   | -   | After software writes 1 to clear BODWK<br>(CLK_PMUSTS[13]) when SPD mode is entered.          |

|                                |                                      | V                           | -   | -   | After software writes 1 to clear LVRF<br>(SYS_RSTSTS[3])                                      |

| LVR                            | LVR Reset                            | -                           | V   | -   | After software writes 1 to clear LVRWK<br>(CLK_PMUSTS[12]) when SPD mode is entered.          |

| POR                            | POR Reset                            | V                           | V   | -   | After software writes 1 to clear PORF<br>(SYS_RSTSTS[0]).                                     |

| EINT                           | External Interrupt                   | V                           | -   | -   | After software write 1 to clear the Px_INTSRC[n] bit.                                         |

| GPIO                           | GPIO Interrupt                       | V                           | -   | -   | After software write 1 to clear the Px_INTSRC[n] bit.                                         |

| GPIO(PA~P<br>D) Wake-up<br>pin | rising or falling edge event, 61-pin | -                           | v   | -   | GPxWK(CLK_PMUSTS[11:8]) is cleared when SPD mode is entered.                                  |

| GPIO(PC.0)<br>Wake-up pin      | rising or falling edge event , 1-pin | -                           | -   | V   | PINWK(CLK_PMUSTS[1]) is cleared when DPD mode is entered.                                     |

| TIMER                          | Timer Interrupt                      | V                           | -   | -   | After software writes 1 to clear TWKF<br>(TIMERx_INTSTS[1]) and TIF<br>(TIMERx_INTSTS[0]).    |

| Wakeup<br>timer                | Wakeup by wake-up timer time-out     | -                           | v   | v   | After software writes 1 to clear TMRWK<br>(CLK_PMUSTS[1]) when SPD or DPD mode is<br>entered. |

| WDT                            | WDT Interrupt                        | V                           | -   | -   | After software writes 1 to clear WKF<br>(WDT_CTL[5]) (Write Protect).                         |

|                                | Alarm Interrupt                      | V                           | -   | -   | After software writes 1 to clear ALMIF<br>(RTC_INTSTS[0]).                                    |

| RTC                            | Time Tick Interrupt                  | V                           | -   | -   | After software writes 1 to clear TICKIF<br>(RTC_INTSTS[1]).                                   |

|                                | Wakeup by RTC alarm                  | -                           | V   | V   | RTCWK (CLK_PMUSTS[5]) is cleared when DPD or SPD mode is entered.                             |

|                       | Wakeup by RTC tick time                                           | - | V | V | RTCWK (CLK_PMUSTS[5]) is cleared when DPD or SPD mode is entered.                                                                                                                                    |

|-----------------------|-------------------------------------------------------------------|---|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Wakeup by tamper event                                            | - | v | V | RTCWK (CLK_PMUSTS[5]) is cleared when DPD<br>or SPD mode is entered.                                                                                                                                 |

|                       | nCTS wake-up                                                      | V | - | - | After software writes 1 to clear CTSWKF<br>(UARTx_WKSTS[0]).                                                                                                                                         |

|                       | RX Data wake-up                                                   | V | - | - | After software writes 1 to clear DATWKF<br>(UARTx_WKSTS[1]).                                                                                                                                         |

| UART                  | Received FIFO Threshold Wake-up                                   | V | - | - | After software writes 1 to clear RFRTWKF<br>(UARTx_WKSTS[2]).                                                                                                                                        |

|                       | RS-485 AAD Mode Wake-up                                           | V | - | - | After software writes 1 to clear RS485WKF<br>(UARTx_WKSTS[3]).                                                                                                                                       |

|                       | Received FIFO Threshold Time-out<br>Wake-up                       | V | - | - | After software writes 1 to clear TOUTWKF<br>(UARTx_WKSTS[4]).                                                                                                                                        |

|                       | CTS Toggle                                                        | V | - | - | After software writes 1 to clear WKF<br>(UUART_WKSTS[0]).                                                                                                                                            |

| USCI UART             | Data Toggle                                                       | V | - | - | After software writes 1 to clear WKF<br>(UUART_WKSTS[0]).                                                                                                                                            |

|                       | Data toggle                                                       | V | - | - | After software writes 1 to clear WKF<br>(UI2C_WKSTS[0]).                                                                                                                                             |

| USCI I <sup>2</sup> C | Address match                                                     | V | - | - | After software writes 1 to clear WKAKDONE<br>(UI2C_PROTSTS[16], then writes 1 to clear WKF<br>(UI2C_WKSTS[0]).                                                                                       |

| USCI SPI              | SS Toggle                                                         | V | - | - | After software writes 1 to clear WKF<br>(USPI_WKSTS[0]).                                                                                                                                             |

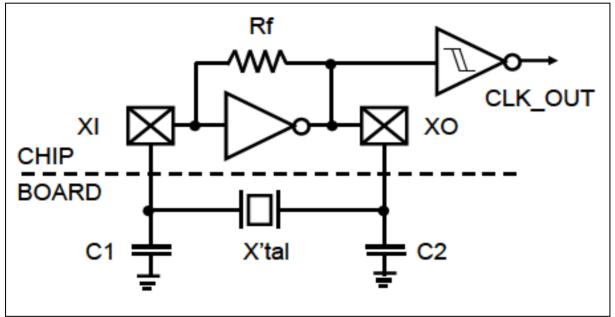

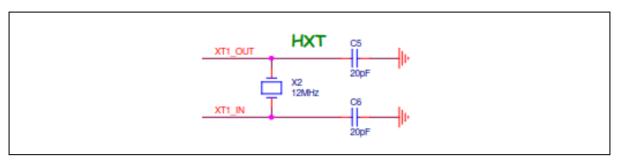

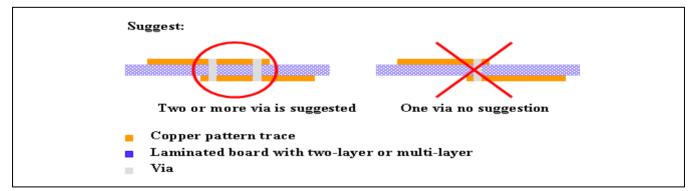

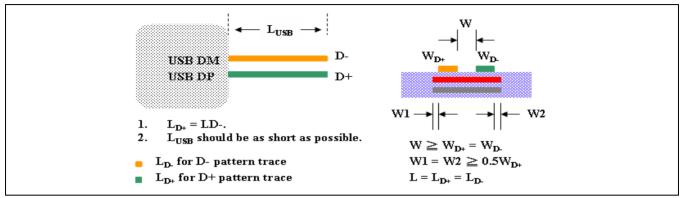

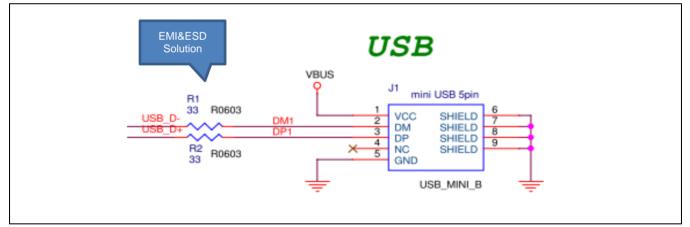

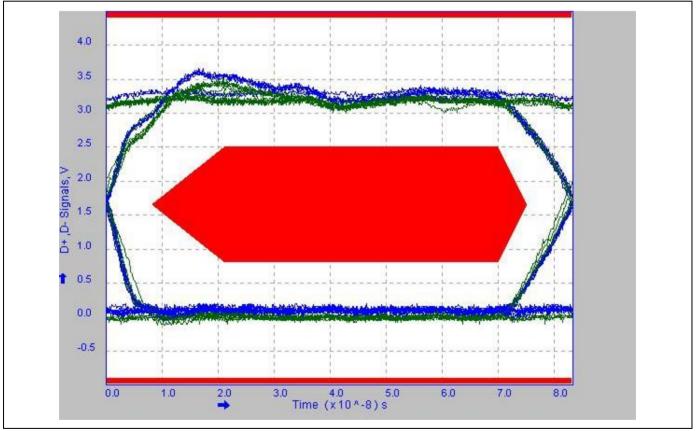

| I <sup>2</sup> C      | Address match wake-up                                             | V | - | - | After software writes 1 to clear WKAKDONE<br>(I2C_WKSTS[1]). Then software writes 1 to clear<br>WKIF(I2C_WKSTS[0]).                                                                                  |